### μPD80C35/C48, μPD48 8-BIT, SINGLE-CHIP CMOS MICROCOMPUTERS

### Description

The  $\mu$ PD80C35,  $\mu$ PD80C48, and  $\mu$ PD48 are true standalone 8-bit microcomputers fabricated using CMOS technology. All of the functional blocks necessary for an integrated microcomputer are incorporated, including a 1K-byte ROM ( $\mu$ PD80C48 only), a 64-byte RAM, 27 I/O lines, an 8-bit timer/event counter, and a clock generator. This integrated capability permits use in stand-alone applications. For designs requiring extra capability, the  $\mu$ PD80C35/ $\mu$ PD80C48 can be expanded using peripherals and is memory compatible with industry-standard 8080A/8085A processors.

Providing compatibility with industry-standard 8048, 8748, and 8035 processors, the  $\mu$ PD80C35/ $\mu$ PD80C48 features significant savings in power consumption. In addition to the power savings gained through CMOS technology, the  $\mu$ PD80C35/ $\mu$ PD80C48 offers two standby modes (Halt and Stop modes) to further minimize power drain.

### Features

- □ 8-Bit CPU with memory and I/O on a single-chip

- Hardware/software-compatible with industrystandard 8048, 8748, and 8035 processors

- □ 1K x 8 ROM (µPD80C48 only)

- 🗆 64 x 8 RAM

- □ 27 I/O lines

- $\Box$  2.5- $\mu$ s cycle time (6-MHz crystal)

- □ All instructions executable in 1 or 2 cycles

- □ 97 instructions: 70 percent are single-byte instructions

- Internal timer/event counter

- □ Two interrupts (external and timer)

- □ Easily expandable memory and I/O

- □ Bus compatible with 8080A/8085A peripherals

- □ Power-efficient CMOS technology requiring a single +2.5 to +6.0 V power supply

- Halt mode

- Stop mode

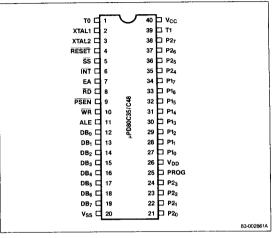

### **Pin Configurations**

#### 40-Pin Plastic DIP

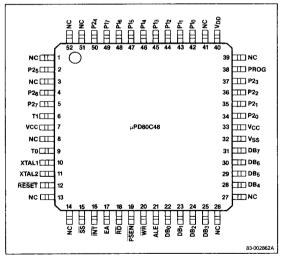

#### 52-Pin Plastic Miniflat

4

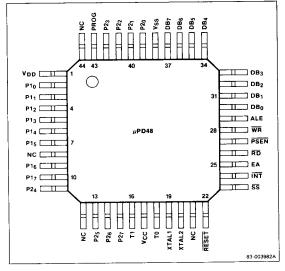

### **Pin Configurations (cont)**

### 44-Pin Plastic Miniflat

### **Ordering Information**

| Part<br>Number | Package<br>Type            | Max Frequency<br>of Operation | ROM    |

|----------------|----------------------------|-------------------------------|--------|

| µPD80C35C      | 40-pin plastic DIP         | 6 MHz                         | None   |

| µPD80C48C      | 40-pin plastic DIP         | 6 MHz                         | 1K x 8 |

| µPD80C48G-00   | 52-pin plastic<br>miniflat | 6 MHz                         | 1K x 8 |

| μPD48G-22      | 44-pin plastic<br>miniflat | 6 MHz                         | 1K x 8 |

#### Note:

$\mu$ PD80C48C,  $\mu$ PD80C48G-00, and  $\mu$ PD48G-22 have two optional port types: type 0, I<sub>OH</sub> =  $-5\mu$ A; type 1, I<sub>OH</sub> =  $-50\mu$ A. Type 0 or 1 can be selected independently for P1<sub>0</sub>-P1<sub>7</sub>, P2<sub>0</sub>-P2<sub>3</sub>, and P2<sub>4</sub>-P2<sub>7</sub>.

### **Pin Identification**

| Symbol                           | Function                    |

|----------------------------------|-----------------------------|

| то                               | Test 0 input/clock output   |

| XTAL1                            | Crystal 1 input             |

| XTAL2                            | Crystal 2 input             |

| RESET                            | Reset input                 |

| SS                               | Software stop input         |

| INT                              | Interrupt input             |

| EA                               | External access input       |

| RD                               | Read output                 |

| PSEN                             | Program store enable output |

| WR                               | Write output                |

| ALE                              | Address latch enable output |

| DB <sub>0</sub> -DB <sub>7</sub> | Bidirectional data bus      |

| V <sub>SS</sub>                  | Ground                      |

| P20-P27                          | Quasi-bidirectional port 2  |

| PROG                             | Program output              |

| V <sub>DD</sub>                  | Oscillator control voltage  |

| P10-P17                          | Quasi-bidirectional port 1  |

| T1                               | Test 1 input                |

| V <sub>CC</sub>                  | Primary power supply        |

| NC                               | No connection               |

|                                  |                             |

### **Pin Functions**

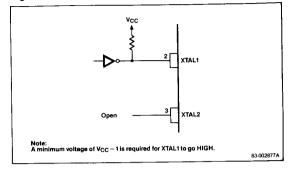

#### XTAL1, XTAL2 [Crystals 1, 2]

XTAL1 and XTAL2 are the crystal inputs for the internal clock oscillator. XTAL1 is also used as an input for external clock signals.

### T0 [Test 0]

The JT0 and JNT0 instructions test the level of T0 and, if it is high, the program address jumps to the specified address. T0 becomes a clock output when the ENT0 CLK instruction is executed.

### T1 [Test 1]

The JT1 and JNT1 instructions test the level of T1 and, if it is high, the program address jumps to the specified address. T1 becomes an internal counter input when the STRT CNT instruction is executed.

### RESET [Reset]

RESET initializes the processor and is also used to verify the internal ROM. RESET determines the oscillation <u>stabilizing</u> time during the release of STOP mode. The RESET pulse width requires at least 5 machine cycles when the supply voltage is within specifications and the oscillation frequency is stable.

### SS [Single Step]

$\overline{SS}$  causes the processor to execute the program one step at a time.

### INT [Interrupt]

INT starts an interrupt if interrupts are enabled. A reset disables an interrupt. INT can be tested with the JNI instruction and, depending on the results, a jump to the specified address can occur.

### EA [External Access]

EA disables internal program memory and fetches and accesses external program memory. EA is used for system testing and debugging.

### RD [Read]

RD enables a data read from external memory.

### WR [Write]

WR enables a data write to external memory.

### PSEN [Program Store Enable]

PSEN fetches instructions only from external program memory.

### ALE [Address Latch Enable]

ALE occurs at each cycle. The falling edge of ALE addresses external data memory or external program memory. ALE can also be used as a clock output.

### DB<sub>0</sub>-DB<sub>7</sub> [Data Bus]

$DB_0$ - $DB_7$  is a bidirectional port, which reads and writes data using RD and WR for latching. During an external program memory fetch,  $DB_0$ - $DB_7$  output the low-order eight bits of the memory address. PSEN fetches the instruction.  $DB_0$ - $DB_7$  also output the address of an external data memory fetch. The addressed data is read and written by RD and WR.

### P10-P17 [Port 1]

P10-P17 is an 8-bit quasi-bidirectional port.

### P20-P27 [Port 2]

P2<sub>0</sub>-P2<sub>7</sub> is an 8-bit quasi-bidirectional port. P2<sub>0</sub>-P2<sub>3</sub> output the high-order four bits of the address during an external program memory fetch. P2<sub>0</sub>-P2<sub>3</sub> also function as a 4-bit I/O bus for the  $\mu$ PD82C43 I/O port expander.

### PROG [Program Pulse]

PROG is used as an output pulse during a fetch when interfacing with the  $\mu$ PD82C43 I/O port expander.

### VDD [Oscillator Control Voltage]

$V_{DD}$  stops and starts the oscillator in STOP mode. STOP mode is enabled by forcing  $V_{DD}$  low during a rest.

### V<sub>CC</sub> [Primary Power Supply]

$V_{CC}$  is the primary power supply.  $V_{CC}$  must be between +2.5 V and +6.0 V for normal operation. In STOP mode,  $V_{CC}$  must be at least +2.0 V to ensure data retention.

### VSS [Ground]

V<sub>SS</sub> is ground potential.

### NC [No Connection]

NC is no connection.

## μ**PD80C35/C48,**μ**PD48**

#### **Block Diagram**

### **Absolute Maximum Ratings**

$\label{eq:rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_$

**Comment:** Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of the specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

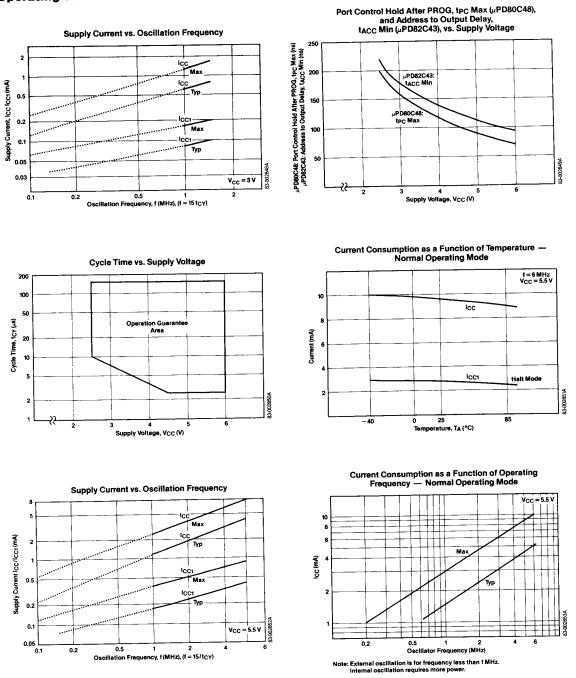

### **DC Characteristics**

#### Standard Voltage Range

$T_A = -40$  °C to +85 °C,  $V_{CC} = +5 V \pm 10\%$ ,  $V_{SS} = 0 V$

|                           |                      |                    | Limits |                 |      | Test                                                                            |

|---------------------------|----------------------|--------------------|--------|-----------------|------|---------------------------------------------------------------------------------|

| Parameter                 | Symbol               | Min                | Тур    | Max             | Unit | Conditions                                                                      |

| nput voltage<br>ow        | VIL                  | -0.3               |        | +0.8            | V    |                                                                                 |

| Input voltage             | VIH                  | V <sub>CC</sub> -2 |        | V <sub>CC</sub> | v    | Except XTAL1,<br>XTAL2, RESET                                                   |

| Ū                         | V <sub>IH1</sub>     | V <sub>CC</sub> -1 |        | V <sub>CC</sub> | V    | RESET, XTAL1,<br>XTAL2                                                          |

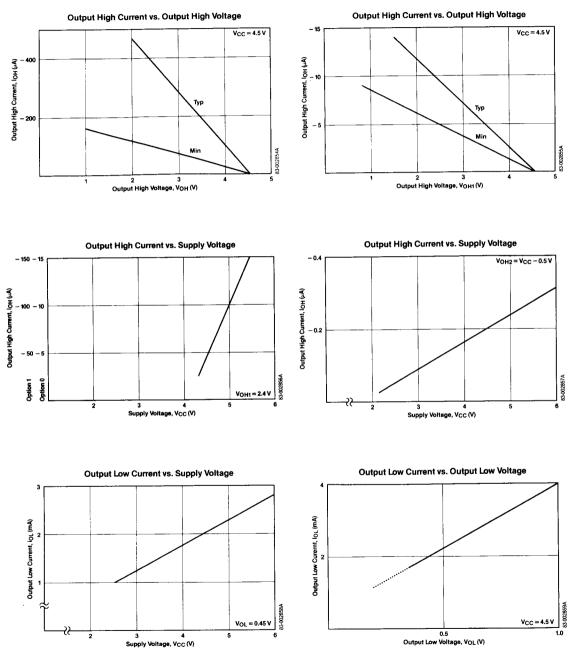

| Output voltage<br>low     | V <sub>OL</sub>      |                    |        | +0.45           | V    | 1 <sub>0L</sub> =2.0 mA                                                         |

| Output voltage<br>high    | V <sub>OH</sub>      | 2.4                |        |                 | V    | <u>Bus, RD</u> , WR,<br>PSEN, ALE, PROG,<br>T0; I <sub>0H</sub> = - 100 μA      |

|                           | V <sub>0H1</sub> (1  | ) 2.4              |        |                 | v    | $I_{OH} = -5 \mu A$ (type<br>0) port 1, port 2                                  |

|                           |                      | 2.4                |        |                 | v    | $I_{OH} = -50 \mu A$<br>(type 1) port 1,<br>port 2                              |

|                           | V <sub>OH2</sub>     | V <sub>CC</sub> -0 | .5     |                 | ۷    | All outputs,<br>$1_{OH} = -0.2 \mu\text{A}$                                     |

| Input current             | I <sub>ILP</sub> (1) |                    | - 15   | 40              | μA   | Port 1, port 2;<br>V <sub>IN</sub> ≤V <sub>IL</sub> (type 0)                    |

|                           |                      |                    |        | - 500           | μA   | Port 1, port 2;<br>V <sub>IN</sub> ≪V <sub>IL</sub> (type 1)                    |

|                           | IILC                 |                    |        | - 40            | μA   | SS, RESET;<br>V <sub>IN</sub> ≪V <sub>IL</sub>                                  |

| Input leakage<br>current  | LII                  |                    |        | ±1              | μA   | T1, ĪNT, V <sub>CC</sub> ;<br>V <sub>SS</sub> ≪V <sub>IN</sub> ≪V <sub>CC</sub> |

|                           | 1 <sub>LI2</sub>     |                    |        | ±3              | μA   | EA; V <sub>SS</sub> ≤V <sub>IN</sub> ≤<br>V <sub>CC</sub>                       |

| Output leakage<br>current | ILO                  |                    |        | ±1              | μA   | V <sub>SS</sub> ≪V <sub>O</sub> ≪V <sub>CC</sub><br>High impedance,<br>bus, T0  |

| Standby curren            | t I <sub>CC1</sub>   |                    | 0.4    | 0.8             | mA   | Halt mode<br>t <sub>CY</sub> = 2.5 µs                                           |

|                           | ICC2                 |                    | 1      | 20              | μA   | Stop mode<br>(Note 2)                                                           |

| Supply current            | Icc                  |                    | 4      | 8               | mA   | $t_{CY} = 2.5 \mu s$                                                            |

| Data retention voltage    | V <sub>CCDP</sub>    | 2.0                |        |                 | v    | Stop mode (V <sub>DD</sub> ,<br>RESET≤0.4 V)                                    |

|                           |                  |                     | Limits |                 |                | Test                                                                                    |

|---------------------------|------------------|---------------------|--------|-----------------|----------------|-----------------------------------------------------------------------------------------|

| Parameter                 | Symbol           | Min                 | Тур    | Max             | Unit           | Conditions                                                                              |

| nput voltage<br>ow        | VIL              | -0.3                |        | +0.18V(         | <sub>C</sub> V |                                                                                         |

| Input voltage<br>high     | VIH              | 0.7V <sub>CC</sub>  |        | V <sub>CC</sub> | v              | Except XTAL1,<br>XTAL2                                                                  |

|                           | V <sub>IH1</sub> | 0.8V <sub>CC</sub>  |        | V <sub>CC</sub> | ۷              | XTAL1, XTAL2                                                                            |

| Output voltage<br>low     | VOL              |                     |        | +0.45           | ۷              | I <sub>OL</sub> =1.0 mA                                                                 |

| Output voltage<br>high    | Voh              | 0.75V <sub>CC</sub> |        |                 | V              | Bus, RD, WR,<br>PSEN, ALE, PROG<br>T0; I <sub>0H</sub> = − 100 μA                       |

|                           | V <sub>0H1</sub> | 0.7V <sub>CC</sub>  | _      |                 | V              | All other outputs;<br>$I_{OH} = -1 \mu A$ (type<br>0) port 1, port 2                    |

|                           |                  | 0.7V <sub>CC</sub>  |        |                 | V              | All other outputs;<br>$I_{OH} = -10 \ \mu A$ (typ<br>1) port 1, port 2                  |

| Input current             | I <sub>ILP</sub> |                     | - 15   | -40             | μÂ             | Port 1, port 2;<br>V <sub>IN</sub> ≪V <sub>IL</sub> (type 0)                            |

|                           |                  |                     |        | - 500           | μA             | Port 1, port 2;<br>V <sub>IN</sub> ≤V <sub>IL</sub> (type 1)                            |

| Input leakage<br>current  | կլ               |                     |        | - 40            | μA             | SS, RESET; V <sub>IN</sub> ≪<br>V <sub>IL</sub>                                         |

|                           | <sup>1</sup> LI1 |                     |        | ±1              | μÂ             | T1, ÎNT, V <sub>SS</sub><br><v<sub>IN<v<sub>CC</v<sub></v<sub>                          |

|                           | I <sub>LI2</sub> |                     |        | ±5              | μA             | EA; V <sub>SS</sub><br><v<sub>IN<v<sub>CC</v<sub></v<sub>                               |

| Output leakage<br>current | ILO              |                     |        | ±1              | μΑ             | V <sub>SS</sub> <v<sub>0<v<sub>CC,<br/>Bus, T0—high<br/>impedance state</v<sub></v<sub> |

| Supply current            | ICC              |                     | 0.8    | 1.6             | mA             | $V_{CC} = 3 V$ ,<br>$t_{CY} = 10 \mu s$                                                 |

|                           |                  |                     | 6      | 12              | μA             | $V_{CC} = 6 V,$<br>$t_{CY} = 25 \mu s$                                                  |

| Standby current           | l loct           |                     | 100    | 200             | μA             | Halt mode;<br>$V_{CC} = 3 V$ ,<br>$t_{CY} = 10 \mu s$                                   |

|                           |                  |                     | 0.6    | 1.2             | mA             | $V_{CC} = 6 V,$<br>$t_{CY} = 2.5 \mu s$                                                 |

|                           | I <sub>CC2</sub> |                     | 1      | 20              | μA             | Stop mode,<br>V <sub>CC</sub> = 3 V                                                     |

|                           |                  |                     | 1      | 50              | μA             | $V_{CC} = 6 V$                                                                          |

#### Note:

(1) Types 0, 1 for µPD80C48 only.

Type 0 for µPD80C35 only.

(2) Input pin voltage is  $V_{IN} \leq V_{IL}$ , or  $V_{IN} \geq V_{IH}$ .

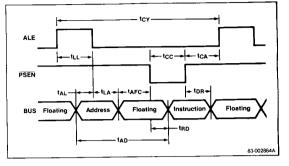

### **AC Characteristics**

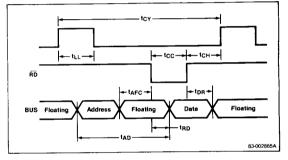

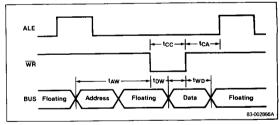

### Read, Write and Instruction Fetch: External Data and **Program Memory**

$T_A = -40^{\circ}$ C to +85°C,  $V_{CC} = V_{DD} = +5V \pm 10\%$ ;  $V_{SS} = 0V$

|                                          |                   |                          | Lim | its                         |      |      |            |

|------------------------------------------|-------------------|--------------------------|-----|-----------------------------|------|------|------------|

|                                          | -                 | V <sub>CC</sub><br>+5V ± |     | V <sub>CC</sub><br>2.5 V to |      |      | Test       |

| Parameter                                | Symbol            | Min                      | Max | Min                         | Max  | Unit | Conditions |

| ALE pulse width                          | tLL               | 400                      |     | 2160                        |      | ns   |            |

| Address setup<br>before ALE              | t <sub>AL</sub>   | 120                      |     | 1620                        |      | ns   |            |

| Address hold<br>from ALE                 | t <sub>LA</sub>   | 80                       |     | 330                         |      | ns   | (Note 1)   |

| Control pulse<br>width (RD, WR,<br>PSEN) | tcc               | 700                      |     | 3700                        |      | ns   |            |

| Data setup<br>before WR                  | t <sub>DW</sub>   | 500                      |     | 3500                        |      | ns   |            |

| Data hold after<br>WR                    | t <sub>WD</sub>   | 120                      |     | 370                         |      | ns   | (Note 2)   |

| Cycle time                               | tcy               | 2.5                      | 150 | 10                          | 150  | μs   | 6 MHz XTAL |

| Data hold                                | tDR               | 0                        | 200 | 0                           | 950  | ns   |            |

| PSEN, RD to data in                      | t <sub>RD</sub>   |                          | 500 |                             | 2750 | ns   |            |

| Address setup<br>before WR               | t <sub>AW</sub>   | 230                      |     | 3230                        |      | ns   | (Note 1)   |

| Address setup<br>before data in          | t <sub>AD</sub>   |                          | 950 |                             | 5450 |      |            |

| Address float to<br>RD, PSEN             | t <sub>AFC</sub>  | 0                        |     | 500                         | _    | ns   | i<br>      |

| Control pulse to<br>ALE                  | o t <sub>CA</sub> | 10                       |     | 10                          |      | ns   | ;<br>      |

### **Bus Timing Requirements (Note 1)**

| Symbol          | Timing Formula                 | Min/Max | Unit |

|-----------------|--------------------------------|---------|------|

|                 | (7 / 30) t <sub>CY</sub> -170  | Min     | ns   |

| AL              | (1/5) t <sub>CY</sub> -380     | Min     | ns   |

| LA              | (1/30) t <sub>CY</sub>         | Min     | ns   |

| t <sub>cc</sub> | (2/5) t <sub>CY</sub> -300     | Min     | ns   |

| tow             | (2/5) t <sub>CY</sub> - 500    | Min     | ns   |

| twp             | (1/30) t <sub>CY</sub> +40     | Min     | ns   |

| t <sub>DR</sub> | (1 / 10) t <sub>CY</sub> - 50  | Max     | ns   |

| t <sub>RD</sub> | (3 / 10) t <sub>CY</sub> - 250 | Мах     | ns   |

| taw             | (2/5) t <sub>CY</sub> -770     | Min     | ns   |

| t <sub>AD</sub> | (3/5) t <sub>CY</sub> - 550    | Max     | ns   |

| tAFC            | (1 / 15) t <sub>CY</sub> - 165 | Min     | ns   |

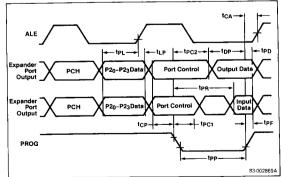

#### Port 2 Timing

$T_A = -40$  °C to +85 °C,  $V_{CC} = V_{DD} = +5 V \pm 10\%$ ;  $V_{SS} = 0 V$

|                                                         |                   |               | Lin | its                         |      |      |            |

|---------------------------------------------------------|-------------------|---------------|-----|-----------------------------|------|------|------------|

|                                                         | -                 | Vcc<br>+5 V 1 |     | V <sub>CC</sub><br>2.5 V to |      |      | Test       |

| Parameter                                               | Symbol            | Min           | Max | Min                         | Max  | Unit | Conditions |

| Port control<br>setup before<br>falling edge of<br>PROG | t <sub>CP</sub>   | 110           |     | 860                         |      | ns   |            |

| Port control hold<br>after falling edge<br>of PROG      | t <sub>PC</sub>   | 0             | 80  | 0                           | 200  | ns   | (Note 4)   |

| PROG to time P2<br>input must be<br>valid               | t <sub>PR</sub>   |               | 810 |                             | 5310 | ns   |            |

| Output data setup time                                  | t <sub>DP</sub>   | 250           |     | 3250                        |      | ns   | (Note 3)   |

| Output data hold time                                   | i t <sub>PD</sub> | 65            |     | 820                         |      | ns   |            |

| Input data hold<br>time                                 | tpF               | 0             | 150 | 0                           | 900  | ns   |            |

| PROG pulse<br>width                                     | tpp               | 1200          |     | 6450                        |      | ns   |            |

| Port 2   / 0 data<br>setup time                         | tpL               | 350           |     | 2100                        |      | ns   |            |

| Port 21/0 data<br>hold time                             | tLP               | 150           |     | 1400                        |      | ns   | i<br>      |

Note:

(1) Control outputs:  $C_L = 80 \text{ pF}$ , bus outputs:  $C_L = 150 \text{ pF}$

(2)  $C_L = 20 \, pF$

(3) Control outputs:  $C_L = 80 \, pF$

(4) Refer to the operating characteristics curves for supply voltage and port control hold.

| Symbol           | Timing Formula                 | Min/Max | Unit |

|------------------|--------------------------------|---------|------|

| t <sub>CP</sub>  | (1/10) t <sub>CY</sub> -140    | Min     | ns   |

| t <sub>PC2</sub> | (4 / 15) t <sub>CY</sub> - 200 | Min     | ns   |

| tpR              | (3/5) t <sub>CY</sub> -690     | Max     | ns   |

| t <sub>PF</sub>  | (1/10) t <sub>CY</sub> - 100   | Max     | ns   |

| t <sub>DP</sub>  | (2/5) t <sub>CY</sub> - 750    | Min     | ns   |

| t <sub>PD</sub>  | (1 / 10) t <sub>CY</sub> - 180 | Min     | ns   |

| tpp              | (7 / 10) t <sub>CY</sub> - 550 | Min     | ns   |

| tpL              | (7/30) t <sub>CY</sub> - 230   | Min     | ns   |

| tLP              | (1/6) t <sub>CY</sub> - 265    | Min     | ns   |

Note:

(1) Unlisted parameters are not affected by cycle time.

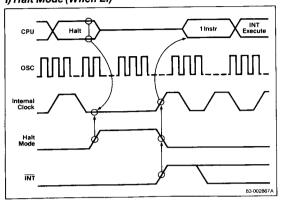

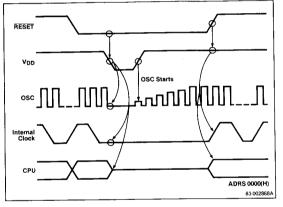

### **Timing Waveforms**

### Instruction Fetch From External Memory

### Read From External Data Memory

#### Write to External Memory

Low Power Standby Operation 1) Halt Mode (When El)

2) Stop Mode

#### Port 2 Timing

#### **Functional Description**

### **Standby Function**

#### Halt Mode

In Halt mode, the oscillator continues to operate, but the internal clock is disabled. The status of all internal logic just prior to execution of the HALT instruction is maintained by the CPU. In Halt mode, power consumption is less than 10 percent of normal  $\mu$ PD80C48 operation and less than 1 percent of normal 8048 operation.

The Halt mode is initiated by execution of the HALT instruction, and is released by either INT or RESET input.

**INT Input.** When the  $\overline{\text{INT}}$  pin receives a low-level input, if interrupts are enabled, the internal clock is restarted and the interrupt is executed after the first or second instruction following the HALT instruction. However, if interrupts are disabled, program operation is resumed from the next address following the HALT instruction. The first instruction following a HALT instruction should be a NOP instruction to ensure proper program execution.

If the Halt mode is released when interrupts are enabled, the interrupt service routine is usually executed after the first or second instruction following the release of Halt mode. However, if either a timer or external interrupt is accepted within one machine cycle prior to a HALT instruction, the corresponding timer or external interrupt service routine is executed immediately following the release of Halt mode. It is important to note this sequence of execution when considering interrupt service routine execution following a HALT instruction.

**RESET Input.** When a low-level input is received by the RESET pin, Halt mode is released and the normal reset operation is activated, restarting program operation from address 0.

#### Stop Mode

In Stop mode, the oscillator is deactivated and only the contents of RAM are maintained. The operation status of the  $\mu$ PD80C35/ $\mu$ PD80C48 resembles that of a reset condition. Because only the contents of RAM are maintained, Stop mode provides even lower power consumption than Halt mode, only requiring a minimum V<sub>CC</sub> as low as +2V.

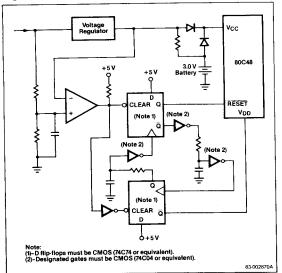

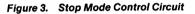

Stop mode is initiated by setting V<sub>DD</sub> to low when RE-SET is low, to protect the contents of RAM. Stop mode is released by first raising the supply voltage at the V<sub>CC</sub> pin from standby level to correct operating level and setting V<sub>DD</sub> to high when RESET is low. After the oscillator has been restarted and the oscillation has stabilized, RESET must be set to high, whereby program operation is started from address 0. Figure 1 shows the Stop mode circuit. Figure 1. Stop Mode Circuit

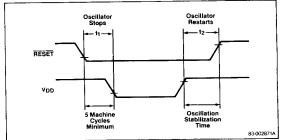

Stop Mode Circuit. Since  $V_{DD}$  controls the restarting of the oscillator, it is important that  $V_{DD}$  be protected from noise interference. The time required to reset the CPU is represented by  $t_1$  (see figure 2), which is a minimum of 5 machine cycles. The reset operation will not be completed in less than 5 machine cycles. In Stop mode, it is important to note that if  $V_{DD}$  goes low before 5 machine cycles have elapsed, the CPU will be deactivated and the output of ALE,  $\overline{RD}$ ,  $\overline{WR}$ ,  $\overline{PSEN}$ , and PROG will not have been stabilized.

Oscillation stabilization time is represented by t<sub>2</sub> (see figure 2). When V<sub>DD</sub> goes high, oscillator operation is reactivated, but it takes time before oscillation can be stabilized. In particular, such high Q resonators as crystals require longer periods to stabilize. Because there is a delay between restarting of the oscillator and oscillator stabilization, t<sub>2</sub> should be long enough to ensure that the oscillator has been fully stabilized.

To facilitate Stop mode control, an external capacitor can be connected to the RESET pin (see figure 3), affecting only  $t_2$ , allowing control of the oscillator stabilization time. When  $V_{DD}$  is asserted in Stop mode, the capacitor begins charging, pulling up RESET. When RE-SET reaches a threshold level equivalent to a logic 1, Stop mode is released. The time it takes RESET to reach the threshold level of logic 1 determines the oscillator stabilization time, which is a function of the capacitance and pull-up resistance values.

### **Port Operation**

NEC

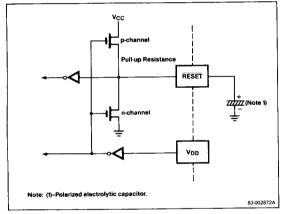

A port-loading option is offered at the time of ordering the mask. Individual source current requirements for Port 1 and the upper and lower halves of Port 2 may be factory set at either  $-5\mu$ A or  $-50\mu$ A (see Port-Loading Options table). The  $-50\mu$ A option is required for interfacing with TTL/NMOS devices. The  $-5\mu$ A option is recommended for interfacing to other CMOS devices. The CMOS option results in lower power consumption and greater noise immunity. Port lines P1<sub>0</sub>-P1<sub>7</sub> and P2<sub>4</sub>-P2<sub>7</sub> include a protective circuit "E" to prevent a signal conflict at the port. The circuit prevents a logic 1 from being written to a line that is being pulled down externally (see figure 4, Port Protection Circuit E diagram). When a logic 0 is detected at the port line and a logic 1 is written from the bus, the NOR gate sends a logic 1 to the D input of the flip-flop. The output is inverted, forcing the NAND gate to send a high-level output. This turns off transistor A, preventing the output of a logic 1 from the port.

### **Port-Loading Options**

$I_{OH}$  (min)  $V_{CC} = V_{DD} = 5 V \pm 10\%$ ;  $V_{OH} = 2.4 V$  (min)

| Option<br>Selected | P10-P17 | ₽2 <sub>0</sub> -₽2 <sub>3</sub> | P24-P27 | Unit |

|--------------------|---------|----------------------------------|---------|------|

| A                  | -5      | -5                               | - 5     | μA   |

| В                  | - 50    | - 5                              | -5      | μA   |

| C                  | - 5     | -50                              | -5      | μA   |

| D                  | - 50    | - 50                             | -5      | μA   |

| E                  | - 5     | -5                               | - 50    | μA   |

| F                  | - 50    | - 5                              | - 50    | μA   |

| G                  | - 5     | - 50                             | - 50    | μA   |

| н                  | - 50    | - 50                             | - 50    | μA   |

#### Note:

(1) The selection of  $I_{OH} = -5\mu A$  will result in a port source current of  $I_{ILP} = -40\mu A$  max when used as input port.

(2) The selection of  $I_{OH} = -50 \mu A$  will result in a port source current of  $I_{ILP} = -500 \mu A$  max when used as input port.

### **Oscillator Operation**

The oscillator maintains an internal frequency for clock generation and controls all system timing cycles. The oscillation is initiated by either a self-generating external resonator or external clock input. The oscillator acts as a high-gain amplifier which produces square-wave pulses at the frequency determined by the resonator or clock source to which it is connected.

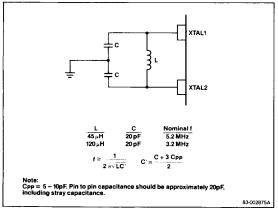

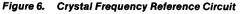

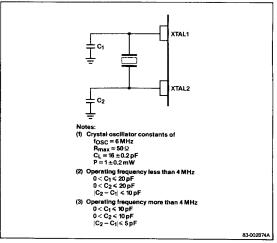

To obtain the oscillation frequency, an external LC network (figure 5) may be connected to the oscillator, or, a ceramic or crystal external resonator (figure 6) may be connected.

As the crystal frequency is lowered, there is an equivalent reduction in series resistance (R). As the temperature of the crystal is lowered, R is increased. Due to this relationship, it becomes difficult to stabilize oscillation when there is low power supply voltage. When  $V_{CC}$  is less than 2.7 V and the oscillator frequency is 3 MHz or less,  $T_A$  (ambient temperature) should not be less than  $-10^{\circ}$ C.

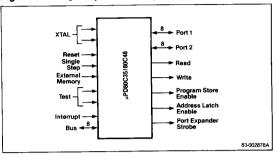

Figures 7 and 8 show the ceramic resonator and external clock frequency reference circuits. Figure 9 shows the  $\mu$ PD80C35/ $\mu$ PD80C48 major I/O signals.

Figure 7. Ceramic Resonator Frequency Reference Circuit

## Figure 8. External Clock Frequency Reference Circuit

### Figure 9. Major Input and Output Signals

### Instruction Set

### Instruction Set Symbol Definitions

| Symbol | Description                                         | Symbol |

|--------|-----------------------------------------------------|--------|

| A      | Accumulator                                         | SP     |

| AC     | Auxiliary carry flag                                | T      |

| addr   | Program or data memory address (a0-a7) or           | TF     |

|        | $(a_0 - a_{10})$                                    | T0, T1 |

| b      | Accumulator bit (b = 0-7)                           | #      |

| BS     | Bank switch                                         | @      |

| BUS    | Bus                                                 | x      |

| C      | Carry flag                                          |        |

| CLK    | Clock                                               |        |

| CNT    | Counter                                             | (x)    |

| data   | 8-bit binary data (d <sub>0</sub> -d <sub>7</sub> ) | ((x))  |

| DBF    | Memory bank flip-flop                               |        |

| F0, F1 | Flag 0, flag 1                                      | AND    |

| INT    | Interrupt pin                                       | OR     |

|        | Indicates the hex number of the specified register  | EXOR   |

|        | or port                                             |        |

| PC     | Program counter                                     |        |

| Pp     | Port 1, port 2, or ports 4-7 (p=1, 2 or 4-7)        |        |

| PSW    | Program status word                                 |        |

| Br     | Register $(r = 0-7)$                                |        |

| Symbol | Description                                                                                                 |

|--------|-------------------------------------------------------------------------------------------------------------|

| SP     | Stack pointer                                                                                               |

| T      | Timer                                                                                                       |

| TF     | Timer flag                                                                                                  |

| T0, T1 | Test 0, test 1 pin                                                                                          |

| #      | Prefix for immediate data                                                                                   |

| @      | Prefix for indirect address                                                                                 |

| x      | Indicates the hex number corresponding to the<br>accumulator bit or page number specified in the<br>operand |

| (x)    | Contents of RAM                                                                                             |

| ((x))  | Contents of memory location addressed by (x)                                                                |

| -      | Transfer direction, result                                                                                  |

| AND    | Logical product (logical AND)                                                                               |

| OR     | Logical sum (logical OR)                                                                                    |

| EXOR   | Exclusive-OR                                                                                                |

|        | Complement                                                                                                  |

| Mnemonic<br>Accumulator |                                                |                                                                                                                                                                                                                                                                                                                                                                                               | Hax   |                | ſ                         | ō              | <b>Operation Code</b> | n Code | -                |                |                |        |       |

|-------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|---------------------------|----------------|-----------------------|--------|------------------|----------------|----------------|--------|-------|

| Accumulator             | Function                                       | Description                                                                                                                                                                                                                                                                                                                                                                                   | Code  | 5              | å                         | õ              | 4                     | ő      | D2               | ŏ              | Do             | Cycles | Bytes |

|                         |                                                |                                                                                                                                                                                                                                                                                                                                                                                               |       |                |                           |                |                       |        |                  |                |                |        |       |

| ADD A, # data           | (A) ← (A) + data                               | Adds immediate data $d_0$ – $d_7$ to the accumulator. Sets or clears both carry flags. (Note 2)                                                                                                                                                                                                                                                                                               | 8     | с <del>С</del> | 0 <sup>9</sup>            | ი მ            | 6 O                   | မ ဗိ   | 0 <sup>6</sup> 0 | ÷- ₽           | <del>4</del> م | 2      | 2     |

| ADD A, Rr               | $(A) \leftarrow (A) + (Rr)$<br>r = 0-7         | Adds the contents of register Rr to the accumulator. Sets or clears both carry flags. (Note 2)                                                                                                                                                                                                                                                                                                | 6n(4) | 0              | -                         | -              | 0                     | -      | <i>۱</i>         | -              | <i>ـ</i>       | -      | -     |

| ADD A, @ Rr             | $(A) \leftarrow (A) + ((Rr))$<br>r = 0-1       | Adds the contents of the internal data memory location specified by bits 0–5 of register Rr to the accumulator. Sets or clears both carry flags. (Note 2)                                                                                                                                                                                                                                     | 6n(4) | 0              | -                         | -              | 0                     | 0      | 0                | 0              | L              | -      |       |

| ADDC A, # data          | (A) (A) + (C) + data                           | Adds, with carry, immediate data d <sub>0</sub> -d <sub>7</sub> to the accumulator. Sets or clears both carry flags. (Note 2)                                                                                                                                                                                                                                                                 | 5     | 9 Q            | ဝမ္                       | ဝမ်            | - 4                   | 0 წ    | ° <sup>2</sup> 0 | - 2            | <del>-</del> 8 | 5      | 2     |

| ADDC A, Rr              | (A) $\leftarrow$ (A) + (C) + (Rr)<br>r = 0-7   | Adds, with carry, the contents of register Rr to the accumulator.<br>Sets or clears both carry flags. (Note 2)                                                                                                                                                                                                                                                                                | 7n(4) | 0              | -                         | -              | -                     | -      | -                | <b>ب</b>       | -              | -      | -     |

| ADDC A, @ Rr            | $(A) \leftarrow (A) + (C) + ((Rr))$<br>r = 0-1 | Adds, with carry, the contents of the internal data memory location specified by bits 0–5 of register Rr, to the accumulator. Sets or clears both carry flags. (Note 2)                                                                                                                                                                                                                       | 7n(4) | 0              | -                         | -              | -                     | 0      | 0                | 0              | -              | -      | -     |

| ANL A, # data           | (A) ← (A) AND data                             | Takes the logical product (logical AND) of immediate data dg-d7<br>and the contents of the accumulator, and stores the result in the<br>accumulator.                                                                                                                                                                                                                                          | 53    | d7 0           | <del>4</del> <del>4</del> | d5 O           | - 2                   | ဝမ်း   | 40 O             | - 5            | - 응            | 5      | 2     |

| ANL A, Rr               | (A) $\leftarrow$ (A) AND (Rr)<br>r = $0-7$     | Takes the logical product (logical AND) of the contents of register<br>Rr and the accumulator, and stores the result in the accumulator.                                                                                                                                                                                                                                                      | 5n(4) | 0              | -                         | 0              | -                     | -      | <b>ـ</b>         | -              | -              | F      | ÷     |

| ANL A, @ Rr             | (A) ← (A) AND ((Rr))<br>r = 0-1                | Takes the logical product (logical AND) of the contents of the<br>internal data memory location specified by bits 0–5 of register Rr,<br>and the accumulator, and stores the result in the accumulator.                                                                                                                                                                                       | 5n(4) | 0              | -                         | 0              | -                     | 0      | 0                | 0              | L              | -      | -     |

| CPL A                   | (A) +- (Ā)                                     | Takes the complement of the contents of the accumulator.                                                                                                                                                                                                                                                                                                                                      | 37    | 0              | 0                         | -              | -                     | 0      | -                | -              | -              | -      | -     |

| CLRA                    | (A) 0                                          | Clears the contents of the accumulator.                                                                                                                                                                                                                                                                                                                                                       | 27    | 0              | 0                         | -              | 0                     | 0      | -                | -              | -              | -      | -     |

| DA A                    |                                                | Converts the contents of the accumulator to BCD. Sets or clears the carry flags. When the lower 4 bits ( $A_0-A_3$ ) are greater than 9, or if the auxiliary carry flag has been set, adds 6 to ( $A_0-A_3$ ). When the upper 4 bits ( $A_4-A_7$ ) are greater than 9 or if the carry flag (C) has been set, adds 6 to ( $A_4-A_7$ ). If an overflow occurs at this point, C is set. (Note 2) | 57    | 0              | -                         | 0              | -                     | 0      | -                | -              | -              | -      | -     |

| DEC A                   | (A) (A) 1                                      | Decrements the contents of the accumulator by 1.                                                                                                                                                                                                                                                                                                                                              | 20    | 0              | 0                         | 0              | 0                     | 0      | -                | -              | -              | -      | -     |

| INC A                   | (A) (A) + 1                                    | Increments the contents of the accumulator by 1.                                                                                                                                                                                                                                                                                                                                              | 17    | 0              | 0                         | 0              |                       | 0      |                  | -              | -              | -      | -     |

| ORL A, # data           | (A) ← (A) OR data                              | Takes the logical sum (logical OR) of immediate data d <sub>0</sub> -d <sub>7</sub> and the<br>contents of the accumulator, and stores the result in the<br>accumulator.                                                                                                                                                                                                                      | 43    | 0<br>d7        | - ф                       | <del>д</del> 0 | d4 0                  | 05     | d 0              | <del>-</del> 2 | <del>-</del> 9 | 5      | 5     |

| orl a, ri               | (A) + (A) OR (Rr) r = 0-7                      | Takes the logical sum (logical OR) of register Rr and the contents of the accumulator, and stores the result in the accumulator.                                                                                                                                                                                                                                                              | 4n(4) | 0              | -                         | 0              | 0                     | -      | -                | -              | -              | -      | -     |

4-224

This Material Copyrighted By Its Respective Manufacturer

| _          |

|------------|

| =          |

| -          |

| •          |

|            |

| •••        |

| -          |

| _          |

| -          |

| -          |

| •          |

|            |

| 60         |

|            |

| -          |

| - 5        |

|            |

| - 0        |

| . <b>—</b> |

|            |

| _          |

| - 63       |

| -          |

|            |

| _          |

| - <b>L</b> |

|            |

| _          |

| - 673      |

| - <b>H</b> |

|            |

| _          |

| _          |

|            |

| Instruction Set    | on Set (cont)                                                                                                                           |                                                                                                                                                                                                                       |       |                                  |                |          |                 |                     |                     |               |        |       |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------|----------------|----------|-----------------|---------------------|---------------------|---------------|--------|-------|

|                    |                                                                                                                                         |                                                                                                                                                                                                                       | Hex   |                                  |                | ð        | Operation Code  | Code                |                     |               | ,      |       |

| Mnemonic           | Function                                                                                                                                | Description                                                                                                                                                                                                           | Code  | 5                                | ດ້             | ŝ        | *               | ۔<br>۵              | D2                  | å             | Cycles | Bytes |

| Accumulator (cont) | 1                                                                                                                                       |                                                                                                                                                                                                                       |       |                                  |                |          |                 |                     |                     |               |        |       |

| ORL A, @ Rr        | (A) (A) OR ((Rr))<br>r = 0-1                                                                                                            | Takes the logical sum (logical OR) of the contents of the internal<br>data memory location specified by bits 0–5 in register Rr, and the<br>contents of the accumulator, and stores the result in the<br>accumulator. | 4n(4) | 0                                | -              | 0        | 0               | 0                   | 0                   | 0             | -      | -     |

| RL A               | (AN + 1) - (AN)<br>$(A_0) - (A_7) N = 0-6$                                                                                              | Rotates the contents of the accumulator one bit to the left. The MSB is rotated into the LSB.                                                                                                                         | E7    | -                                | ۰              | -        | 0               | 0                   | -                   | -             | -      | -     |

| RLC A              | $(AN + 1) \leftarrow (AN); N = 0-6$<br>$(A_0) \leftarrow (C)$<br>$(C) \leftarrow (A_7)$                                                 | Rotates the contents of the accumulator one bit to the left through carry.                                                                                                                                            | F7    | <del>.</del>                     | -              | -        | -               | 0                   | -                   | -             | -      | -     |

| RR A               | $(AN) \leftarrow (AN + 1); N = 0-6$<br>$(A_7) \leftarrow (A_0)$                                                                         | Rotates the contents of the accumulator one bit to the right. The LSB is rotated into the MSB.                                                                                                                        | 11    | 0                                | -              | -        | -               | 0                   | -                   | -             | -      | -     |

| RRC A              | $(AN) \leftarrow (AN + 1); N = 0-6$<br>$(A_7) \leftarrow (C)$<br>$(C) \leftarrow (A_0)$                                                 | Rotates the contents of the accumulator one bit to the right through carry.                                                                                                                                           | 67    | 0                                | -              | -        | 0               | 0                   | -                   |               |        | -     |

| SWAP A             | (A4-A7) + (A0-A3)                                                                                                                       | Exchanges the contents of the lower 4 bits of the accumulator with the upper 4 bits of the accumulator.                                                                                                               | 47    | 0                                | -              | 0        | 0               | 0                   | -                   | -             | -      |       |

| XRL A, # data      | (A) (A) XOR data                                                                                                                        | Takes the exclusive OR of immediate data $d_0-d_7$ and the contents of the accumulator, and stores the result in the accumulator.                                                                                     | D3    | 1<br>d <sub>7</sub>              | - 9<br>d6      | d5<br>d5 | 1<br>d4         | 0<br>d3             | d2<br>0             | 1<br>գ_<br>40 | 2      | 2     |

| XRL A, Rr          | $(A) \leftarrow (A) XOR (Rr)$ $r = 0-7$                                                                                                 | Takes the exclusive OR of the contents of register Ar and the accumulator, and stores the result in the accumulator.                                                                                                  | Dn(4) | -                                | -              | 0        | -               | -                   | <i>ـ</i>            | -             | -      | -     |

| XRL A, @ Rr        | (A) $-$ (A) XOR ((Rr))<br>r = 0-1                                                                                                       | Takes the exclusive OR of the contents of the location in data<br>memory specified by bits 0–5 in register Rr, and the accumulator,<br>and stores the result in the accumulator.                                      | Dn(4) | -                                | -              | 0        | -               | 0                   | 0                   | 0             |        | -     |

| Branch             |                                                                                                                                         |                                                                                                                                                                                                                       |       |                                  |                |          |                 |                     |                     |               |        |       |

| DJNZ Rr, addr      | $\begin{array}{l} (Rr) \leftarrow (Rr) - 1; \ r = 0 - 7 \\ \text{If } (Rr) \neq 0; \\ (PC_0 - PC_7) \leftarrow \text{addr} \end{array}$ | Decrements the contents of register Rr by 1, and if the result is not equal to 0, jumps to the address indicated by $a_0-a_7$ .                                                                                       | ធ     | 1<br>a7                          | a <sub>6</sub> | a5<br>1  | 0<br>a4         | a <sub>3</sub>      | r<br>a2             | г г<br>а1 а0  |        | 2     |

| JBb addr           | $(PC_0 - PC_7) - addr if b = 1$<br>(PC) = (PC) + 2 if b = 0                                                                             | Jumps to the address specified by $a_0$ - $a_7$ if the bit in the accumulator specified by $b_0$ - $b_2$ is set.                                                                                                      | x2(6) | b <sub>2</sub><br>a <sub>7</sub> | <sup>4</sup> 8 | b0<br>a5 | 94 <del>-</del> | 0<br><sup>3</sup> 3 | 0<br><sup>a</sup> 2 | 1 0<br>a1 a0  | 5      | 5     |

|                    |                                                                                                                                         |                                                                                                                                                                                                                       |       |                                  |                |          |                 |                     |                     |               |        |       |

## μ**PD80C35/C48, μPD48**

|               |                                                                                                                                             |                                                                                                                                                                                                             | Ver      |                     |                     | ð                   | eratio           | <b>Operation Code</b> |                     |                  |                      |        |       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|---------------------|---------------------|------------------|-----------------------|---------------------|------------------|----------------------|--------|-------|

| Mnemonic      | Function                                                                                                                                    | Description                                                                                                                                                                                                 | Code     | 5                   | å                   | ŝ                   | 4                | ő                     | D2                  | ā                | 5<br>6               | Cycles | Bytes |

| Branch (cont) |                                                                                                                                             |                                                                                                                                                                                                             |          |                     |                     |                     |                  |                       |                     |                  |                      |        |       |

| JC addr       | $(PC_0 - PC_7) \leftarrow addr if C = 1$<br>(PC) $\leftarrow (PC) + 2 if C = 0$                                                             | Jumps to the address specified by $a_0-a_7$ if the carry flag is set.                                                                                                                                       | F6       | 1<br>a7             | 1<br>a <sub>6</sub> | a5                  | - 1<br>94        | 93 0                  | 1<br>a <sub>2</sub> | - 19<br>- 19     | 9 Q                  | 2      | 5     |

| JF0 addr      | $(PC_0 - PC_7) \leftarrow addr if F0 = 1$<br>(PC) $\leftarrow (PC) + 2 if F0 = 0$                                                           | Jumps to the address specified by $a_0-a_7$ if F0 is set.                                                                                                                                                   | B6       | 1<br>a <sub>7</sub> | 0<br>9 <sup>6</sup> | a5                  | a4 1             | 0<br>33               | 1<br>a <sub>2</sub> | a <sub>1</sub> a | 0<br>30              | 2      | 5     |

| JF1 addr      | $(PC_0-PC_7) \leftarrow addr if F1 = 1$<br>(PC) $\leftarrow (PC) + 2 if F1 = 0$                                                             | Jumps to the address specified by $a_0-a_7$ if F1 is set.                                                                                                                                                   | 76       | 0<br>a7             | <del>4</del> 98     | a5 1                | 1<br>a4          | 0<br>a3               | 1<br>a <sub>2</sub> | a 1<br>81        | 0<br>80              | 2      | 2     |

| JMP addr      | $(PC_{10} - PC_{10}) \leftarrow (addr_8 - addr_{10})$<br>$(PC_{0} - PC_{7}) \leftarrow (addr_{0} - addr_{7})$<br>$(PC_{11}) \leftarrow DBF$ | Jumps directly to the address specified by $a_0^{-a_{10}}$ and the DBF.                                                                                                                                     | x4(6)    | a10<br>a7           | ag<br>a6            | a5<br>a5            | a4<br>0          | 0<br>a <sub>3</sub>   | a <sub>2</sub> 1    |                  | 0 <mark>9</mark> 0 0 | 5      | 5     |

| JMPP @ A      | (PC <sub>0</sub> -PC <sub>7</sub> )                                                                                                         | Replaces the lower 8 bits of the program counter with the contents<br>of program memory specified by the contents of the accumulator,<br>producing a jump to the specified address within the current page. | 83       | -                   | 0                   | -                   | -                | 0                     | 0                   | -                | -                    | 5      | -     |

| JNC addr      | $(PC_0-PC_7) \leftarrow addr if C = 0$<br>(PC) $\leftarrow$ (PC) + 2 if C = 1                                                               | Jumps to the address specified by $a_0-a_7$ if the carry flag is not set.                                                                                                                                   | E6       | 1<br>a7             | a <sub>6</sub> 1    | - 3 <sup>9</sup>    | 94 O             | 0<br><sup>3</sup> 3   | 1<br>a2             |                  | a0<br>90             | 2      | 2     |

| JNI addr      | $(PC_0 - PC_7) - addr if   = 0$<br>(PC) - (PC) + 2 if   = 1                                                                                 | Jumps to the address specified by $a_0\text{-}a_7$ if the interrupt flag is not set.                                                                                                                        | 86       | 1<br>a7             | 0<br>a <sub>6</sub> | ၀ မို               | a4<br>0          | 0<br><sup>3</sup> 3   | a <sub>2</sub>      |                  | 0<br>80              | 2      | 5     |

| JNT0 addr     | $(PC_0 - PC_7) \leftarrow addr if T0 = 0$<br>(PC) $\leftarrow (PC) + 2 if T0 = 1$                                                           | Jumps to the address specified by $a_0-a_7$ if test 0 is low.                                                                                                                                               | 26       | 0<br>a7             | 0 %                 | a5 -                | a4<br>0          | 0<br>a3               | 1<br>a <sub>2</sub> | a1<br>31         | a0<br>10             | 2      | 2     |

| JNT1 addr     | $(PC_0-PC_7) - addr if T1 = 0$<br>(PC) - (PC) + 2 if T1 = 1                                                                                 | Jumps to the address specified by $a_0 - a_7$ if test 1 is low.                                                                                                                                             | 46       | 0<br>a7             | a <sub>6</sub>      | a5<br>0             | 9 <sup>4</sup> 0 | 0<br>a3               | a <sub>2</sub>      | a -              | a0<br>80             | 2      | 5     |

| JNZ addr      | $(PC_0 - PC_7) \leftarrow addr \text{ if } A \neq 0$<br>(PC) \leftarrow (PC) + 2 if A = 0                                                   | Jumps to the address specified by $a_0-a_7$ if the contents of the accumulator are not equal to 0.                                                                                                          | 96       | 1<br>a7             | 0<br>a <sub>6</sub> | a5<br>0             | a4 1             | a3 0                  | 1<br>a2             | <del>م</del> - ۴ | a0                   | 5      | 7     |

| JTF addr      | $(PC_0-PC_7) \leftarrow addr if TF = 1$<br>$(PC) \leftarrow (PC) + 2 if TF = 0$                                                             | Jumps to the address specified by $a_0-a_7$ if the timer flag is set. The timer flag is cleared after the instruction is executed.                                                                          | 16       | 0<br>a7             | 0<br>a <sub>6</sub> | a5 0                | a4 -             | a3 0                  | 1<br>a2             | a1 -             | a0<br>80             | 5      | 5     |

| JT0 addr      | $(PC_0-PC_7) \leftarrow addr if T0 = 1$<br>(PC) $\leftarrow (PC) + 2 if T0 = 0$                                                             | Jumps to the address specified by $a_0-a_7$ if test 0 is high.                                                                                                                                              | 36       | 0<br>a7             | 0<br>a <sub>6</sub> | <del>a</del> 5 -    | 1<br>84          | a <sub>3</sub> 0      | a2                  | <del>न</del> स्  | 0 8                  | 5      | 5     |

| JT1 addr      | $(PC_0 - PC_7) \leftarrow addr if T1 = 1$<br>(PC) $\leftarrow (PC) + 2 if T1 = 0$                                                           | Jumps to the address specified by $a_0$ - $a_7$ if test 1 is high.                                                                                                                                          | 56       | a7                  | - a6                | ၀ ဗိ                | a4 1             | 33 O                  | - <sup>4</sup>      | a, 1             | 90<br>90             | 5      | 5     |

| Zſ            | $(PC_0 - PC_7) \leftarrow addr if A = 0$<br>(PC) $\leftarrow (PC) + 2 if A = 1$                                                             | Jump to the address specified by $a_0-a_7$ if the contents of the accumulator are equal to 0.                                                                                                               | 90<br>Ce | 1<br>a7             | a <sub>6</sub>      | 0<br>a <sub>5</sub> | 0<br>a4          | a3<br>93              | 1<br>a2             | 4 F              | 9 O                  | 2      | 2     |

|               |                                                                                                                                             |                                                                                                                                                                                                             |          |                     |                     |                     |                  |                       |                     |                  |                      |        |       |

| Instructio       | Instruction Set (cont)         |                                                                                                                                                                                      |                |         |                     | ľ              |            | .                                    |     |     |        |       |

|------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|---------------------|----------------|------------|--------------------------------------|-----|-----|--------|-------|

|                  |                                |                                                                                                                                                                                      | Hex            |         |                     |                | <u>a</u>   |                                      |     | 1   |        |       |

| Mnemonic         | Function                       | Description                                                                                                                                                                          | e<br>Code<br>C | 5       | å                   | -<br>-         | 2<br>2     | 5                                    | ٥   | 8   | Cycles | bytes |

| Control          | Î                              |                                                                                                                                                                                      |                |         |                     |                |            |                                      |     |     |        |       |

| ENI              |                                | Enables external interrupts. When external interrupts are enabled,<br>a low-level input to the INT pin causes the processor to vector to<br>the interrupt service routine.           | 02             | 0       | 0                   | 0              | 0          | -                                    | 0   | -   | -      | -     |

| I SIQ            |                                | Disables external interrupts. When external interrupts are<br>disabled, low-level inputs to the INT pin have no effect on program<br>execution.                                      | 15             | 0       | 0                   | 0              | 1 0        | -                                    | 0   | -   | -      | -     |

| ENTO CLK         |                                | Enables clock output to pin T0.                                                                                                                                                      | 75             | 0       | -                   | -              | -          | 1                                    | 0   | -   | -      | -     |

| SEL MB0          | (DBF) +- 0                     | Clears the memory bank flip-flop, selecting program memory bank 0 (program memory addresses 0-2047(10)). Clears PC <sub>11</sub> after the next JMP or CALL instruction.             | ES             | -       | -                   | -              | 0          | -                                    | 0   | -   | -      | -     |

| SEL MB1          | (D8F) ← 1                      | Sets the memory bank flip-flop, selecting program memory bank 1 (program memory addresses 2048–4095 <sub>(10)</sub> ). Sets PC <sub>11</sub> after the next JMP or CALL instruction. | F5             | -       | -                   | -              | -          | 0                                    | 0   | -   | -      | -     |

| SEL RBO          | (BS) 0                         | Selects data memory bank 0 by clearing bit 4 (bank switch) of the PSW. Specifies data memory addresses $0^{-7}(10)$ as registers $0^{-7}$ of data memory bank 0.                     | C5             | -       |                     | 0              | 0          | - 1                                  | 0   | -   | -      | -     |

| SEL RB1          | (BS) ← 1                       | Selects data memory bank 1 by setting bit 4 (bank switch) of the PSW. Specifies data memory 24–31( $_{\rm 10}$ ) as registers 0–7 of data memory bank 1.                             | 02             | -       | -                   | 0              | -          | 0                                    | 0   | -   | -      | -     |

| HALT             |                                | Initiates halt mode.                                                                                                                                                                 | 6              | 0       | 0                   | 0              | 0          | 0                                    | 0   | -   | -      | -     |

| Data Moves       |                                |                                                                                                                                                                                      |                |         |                     |                |            |                                      |     |     |        |       |

| MOV A, # data    | (A) 🔶 data                     | Moves immediate data $d_0$ - $d_7$ into the accumulator.                                                                                                                             | 23             | 0<br>d7 | 0<br>d <sub>6</sub> | d <sub>5</sub> | 0 4<br>0   | 0 0<br>d <sub>3</sub> d <sub>2</sub> |     | - ₽ | 2      | 2     |

| MOV A, Rr        | (A) $\leftarrow$ (Rr); r = 0-7 | Moves the contents of register Rr into the accumulator.                                                                                                                              | Fn(4)          | -       | -                   | -              | -          | -                                    | -   | -   | -      | -     |