## PRELIMINARY DATA SHEET

## MOS INTEGRATED CIRCUIT

## $\mu$ PD17202AGF-011

# 4-BIT SINGLE-CHIP MICROCONTROLLER WITH LCD CONTROLLER/DRIVER AND KEY SCAN CIRCUIT FOR FPC (FRONT PANEL CONTROLLER)

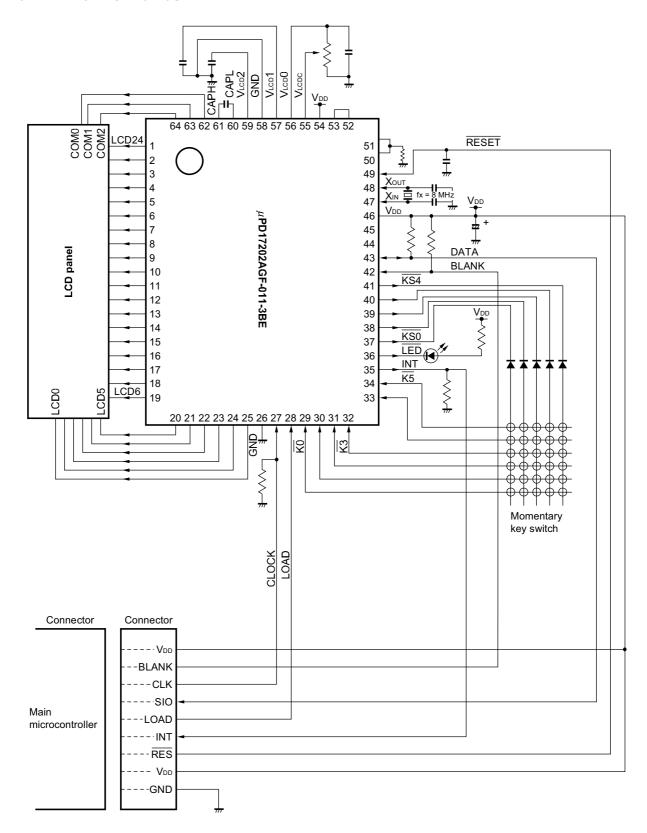

The  $\mu$ PD17202AGF-011 is a CMOS microcontroller for the FPC (Front Panel Controller) of a car stereo system. This microcontroller is housed in a 64-pin QFP and is provided with an LCD controller/driver and key scan circuit, enabling the reduction of the amount of wiring between the front panel of the car stereo system and the master microcontroller.

#### **FEATURES**

• LCD controller/driver : Can display up to 75 segments.

1/3 duty, 1/3 bias, frame frequency: 325.5 Hz

• Key scan circuit : Can read up to 30 (5  $\times$  6) keys.

• LED output : 1 pin

· 3-wire serial communication mode: CLOCK, DATA, and LOAD pins

Supply voltage : V<sub>DD</sub> = 4.5 to 5.5 V

System clock : fx = 8 MHz

#### **ORDERING INFORMATION**

Part NumberPackageμPD17202AGF-011-3BE64-pin plastic QFP (14  $\times$  20 mm, 1.0-mm pitch)

The information in this document is subject to change without notice.

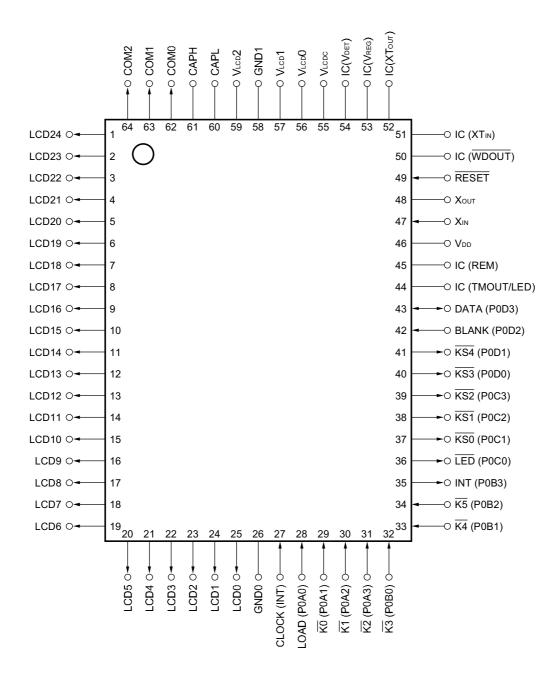

#### PIN CONFIGURATION (Top View)

64-pin plastic QFP (14  $\times$  20 mm, 1.0-mm pitch)  $\mu$ PD17202AGF-011-3BE

Remarks 1. IC: Internally Connected

**2.** ( ): Pin names of  $\mu$ PD17202AGF- $\times\times$ -3BE

## **CONTENTS**

| 1. | PIN FUNCTION                                                     | 4  |

|----|------------------------------------------------------------------|----|

|    | 1.1 Pin Function List                                            | 4  |

| 2. | CONFIGURATION OF KEY MATRIX                                      | 6  |

|    | 2.1 Layout of Key Matrix                                         | 6  |

|    | 2.1 Layout of Key Matrix                                         | 7  |

| 3. | KEY SCAN                                                         |    |

|    | 3.1 Key Scan Function                                            | 8  |

|    | 3.2 Data Configuration                                           | Ś  |

| 4. | LCD DISPLAY FUNCTION                                             | 10 |

|    | 4.1 Configuration of LCD Data Segment and LCD Panel Display Data | 10 |

|    | 4.2 LCD Display Data Configuration                               | 12 |

| 5. | SERIAL DATA COMMUNICATION                                        |    |

|    | 5.1 Serial Data Input                                            | 14 |

|    | 5.2 Serial Data Output                                           | 15 |

|    | 5.3 Timing Chart of Serial Data Communication                    |    |

| 6. | APPLICATION CIRCUIT EXAMPLE                                      | 19 |

| 7. | ELECTRICAL SPECIFICATIONS (preliminary)                          | 20 |

| 8. | PACKAGE DRAWINGS                                                 | 25 |

## 1. PIN FUNCTION

## 1.1 Pin Function List

| Pin No.        | Pin No. Symbol Pin Name Description |                               |                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O Format                 |

|----------------|-------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1<br>to<br>25  | to<br>LCD0                          | LCD segment signal output     | These pins output segment signals to an LCD panel. They are used to control the display on the LCD panel by forming a matrix with COM0 through COM2 (pins 62 through 64).                                                                                                                                                                                                                                                  | CMOS push-<br>pull output  |

| 26<br>58       | GND0<br>GND1                        | Ground                        | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                 | _                          |

| 27             | CLOCK                               | Clock input                   | Serial communication clock input.  Data is input to or output from the DATA pin (pin 43) at the rising edge of the clock input to this pin.                                                                                                                                                                                                                                                                                | Input                      |

| 28             | LOAD                                | Load input                    | Serial communication load input.  Commands are executed and the output status is cleared in synchronization with the rising edge of this pin. While this pin is high, clock input is invalid. This pin is connected to an internal pull-up resistor.                                                                                                                                                                       | Input                      |

| 29<br>to<br>34 | K0<br>to<br>K5                      | Key return signal input       | These pins input key return signals from a key matrix.  These pins are connected to an internal pull-down resistor.                                                                                                                                                                                                                                                                                                        | Input                      |

| 35             | INT                                 | Key scan end<br>signal output | This pin outputs a key scan end signal to the master microcontroller.  It goes high when key scanning has ended after execution of a key data output command.  This pin goes low at the rising edge of the LOAD pin (pin 28) after data has been output. While this pin is low, key data cannot be correctly output.  The initial value of this pin is the low level. Be sure to connect a pull-down resistor to this pin. | CMOS push-<br>pull output  |

| 36             | LED                                 | LED output                    | This pin is connected to an LED that is used to check connection with the master microcontroller.  When this pin is low, the LED lights.  This pin is output depending on the LED data value of display data input (data A, refer to 4.2 LCD Display Data Configuration).  This pin is floated in the initial status.                                                                                                      | N-ch open-<br>drain output |

| 37<br>to<br>41 | KS0<br>to<br>KS4                    | Key source output             | These pins output key source signals to a key matrix.                                                                                                                                                                                                                                                                                                                                                                      | N-ch open-<br>drain output |

| Pin No.        | Symbol                  | Pin Name                                      | Description                                                                                                                                                                                                   | I/O Format                 |

|----------------|-------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 42             | BLANK                   | Blank input                                   | By connecting an external controller to this pin, the display of the LCD panel can be turned ON/OFF.                                                                                                          | Input                      |

|                |                         |                                               | Input level LCD display status                                                                                                                                                                                |                            |

|                |                         |                                               | Low Lights                                                                                                                                                                                                    |                            |

|                |                         |                                               | High Extinguishes                                                                                                                                                                                             |                            |

|                |                         |                                               | To control this pin, connect it to an external controller via pull-up resistor; otherwise, connect it to GND via pull-down resistor.                                                                          |                            |

| 43             | DATA                    | Serial data I/O                               | Serial communication data I/O pin.  This pin outputs data from the rising edge of the LOAD pin (pin 28) after a key data output signal has been received, to the next rising edge; otherwise, it inputs data. | N-ch open-<br>drain output |

| 44, 45         | IC                      | Internally connected                          | Connect nothing to these pins.                                                                                                                                                                                | _                          |

| 50, 51         |                         |                                               | Connect these pins to GND via pull-down resistor.                                                                                                                                                             |                            |

| 52, 53         |                         |                                               | Short-circuit pins 52 and 53.                                                                                                                                                                                 |                            |

| 54             |                         |                                               | Connect this pin to V <sub>DD</sub> .                                                                                                                                                                         |                            |

| 46             | V <sub>DD</sub>         | Power supply                                  | This is a common power supply pin (VDD = 2.2 to 5.5 V).                                                                                                                                                       | _                          |

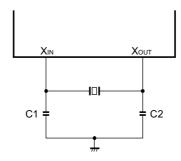

| 47             | Xin                     | Crystal resonator                             | These pins are used to connect a crystal resonator.                                                                                                                                                           | Input                      |

| 48             | Хоит                    |                                               | Connect an 8-MHz ceramic oscillator or crystal resonator to these pins. The accuracy of the watch is influenced only by the oscillation frequency of the oscillator.                                          | _                          |

| 49             | RESET                   | Reset input                                   | Reset input.                                                                                                                                                                                                  | Input                      |

| 55             | VLCDC                   | LCD reference<br>voltage adjustment           | This pin is used to adjust the reference voltage for the LCD driver. Example $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                           | _                          |

| 56<br>57<br>59 | VLCDO<br>VLCD1<br>VLCD2 | LCD regulator                                 | LCD regulator pin.                                                                                                                                                                                            | _                          |

| 60<br>61       | CAPL<br>CAPH            | LCD boosting capacitor                        | These pins connect a capacitor used to boost the LCD driver voltage. Connect a capacitor of 0.47 $\mu\text{F}$ between the CAPL and CAPH pins.                                                                | _                          |

| 62<br>to<br>64 | COM0<br>to<br>COM2      | Common signal output of LCD controller/driver | These pins output the common signals of the LCD controller/driver.                                                                                                                                            | CMOS 3-<br>state output    |

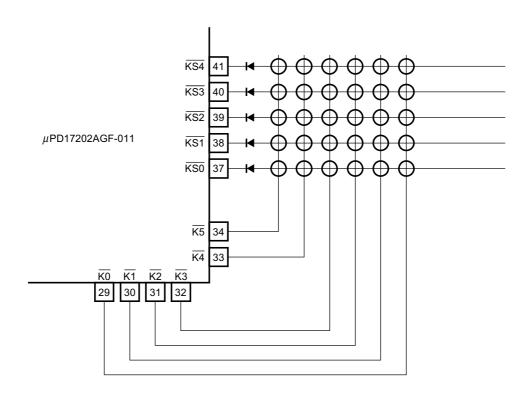

## 2. CONFIGURATION OF KEY MATRIX

## 2.1 Layout of Key Matrix

The  $\mu$ PD17202AGF-011 can be used to configure a key matrix of up to 30 keys, KEY0 through KEY29, by using the  $\overline{\text{KS0}}$  through  $\overline{\text{KS4}}$  pins (key source pins) and  $\overline{\text{K0}}$  through  $\overline{\text{K5}}$  pins (key return pins).

Keys KEY0 through KEY29 are allocated as shown below. The details of each key can be set arbitrarily.

| Input Pin (Pin No.) Output Pin (Pin No.) | K0 (29) | K1 (30) | K2 (31) | K3 (32) | K4 (33) | K5 (34) |

|------------------------------------------|---------|---------|---------|---------|---------|---------|

| KS0 (37)                                 | KEY0    | KEY1    | KEY2    | KEY3    | KEY4    | KEY5    |

| KS1 (38)                                 | KEY6    | KEY7    | KEY8    | KEY9    | KEY10   | KEY11   |

| KS2 (39)                                 | KEY12   | KEY13   | KEY14   | KEY15   | KEY16   | KEY17   |

| KS3 (40)                                 | KEY18   | KEY19   | KEY20   | KEY21   | KEY22   | KEY23   |

| KS4 (41)                                 | KEY24   | KEY25   | KEY26   | KEY27   | KEY28   | KEY29   |

Remark Numbers in brackets ( ) are pin numbers.

## 2.2 Connection of Key Matrix

An example of connection of the key matrix is shown below.

#### 3. KEY SCAN

## 3.1 Key Scan Function

Key scanning is started when a key data output command is executed.

The INT pin (pin 35) goes high when key scanning has ended.

The INT pin goes low when the LOAD pin (pin 28) goes high.

KS0

KS1

KS2

KS3

KS4

1.6 - 1.9 ms (2.8 - 3.4 ms)<sup>Note</sup>

Key data output command

Key data output command

Key data output command

Figure 3-1. Timing Chart of Key Scanning

$\textbf{Note} \quad \text{The value in brackets ( \ ) is when "display data input + key data output" is executed.}$

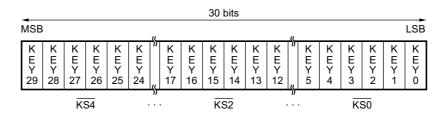

## 3.2 Data Configuration

The data output by the key data output command consists of 30 bits.

The contents of the output data are as shown below.

Figure 3-2. Configuration of Output Data (Key Data Output)

The status of the output data can be identified by the data of each bit as shown below.

| Data | Status  |  |  |

|------|---------|--|--|

| 0    | Key off |  |  |

| 1    | Key on  |  |  |

## 4. LCD DISPLAY FUNCTION

## 4.1 Configuration of LCD Data Segment and LCD Panel Display Data

The segments consisting of LCD0 through LCD24 pins and COM0 through COM2 pins correspond to the LCD panel display data as shown in the table below.

**Table 4-1 Configuration of LCD Segment** and **Table 4-2 Display Data Table** correspond to each other. Any LCD display setting can be performed based on these tables.

Table 4-1. Configuration of LCD Segment

| Common Pin<br>(Pin No.)<br>Segment Pin<br>(Pin No.) | COM0 (62) | COM1 (63) | COM2 (64) |

|-----------------------------------------------------|-----------|-----------|-----------|

| LCD0 (25)                                           | B4        | A0        | В0        |

| LCD1 (24)                                           | A3        | A1        | B1        |

| LCD2 (23)                                           | A4        | A2        | B2        |

| LCD3 (22)                                           | В9        | A5        | B5        |

| LCD4 (21)                                           | A8        | A6        | В6        |

| LCD5 (20)                                           | A9        | A7        | В7        |

| LCD6 (19)                                           | B14       | A10       | B10       |

| LCD7 (18)                                           | A13       | A11       | B11       |

| LCD8 (17)                                           | A14       | A12       | B12       |

| LCD9 (16)                                           | B19       | A15       | B15       |

| LCD10 (15)                                          | A18       | A16       | B16       |

| LCD11 (14)                                          | A19       | A17       | B17       |

| LCD12 (13)                                          | B24       | A20       | B20       |

| LCD13 (12)                                          | A23       | A21       | B21       |

| LCD14 (11)                                          | A24       | A22       | B22       |

| LCD15 (10)                                          | B33       | B38       | B28       |

| LCD16 (9)                                           | B29       | A25       | B25       |

| LCD17 (8)                                           | A28       | A26       | B26       |

| LCD18 (7)                                           | A29       | A27       | B27       |

| LCD19 (6)                                           | B34       | A30       | B30       |

| LCD20 (5)                                           | A33       | A31       | B31       |

| LCD21 (4)                                           | A34       | A32       | B32       |

| LCD22 (3)                                           | B39       | A35       | B35       |

| LCD23 (2)                                           | A38       | A36       | B36       |

| LCD24 (1)                                           | A39       | A37       | B37       |

10

Table 4-2. Display Data Table

| Segment   | Δ.  | В        |

|-----------|-----|----------|

| Data Name | А   | В        |

| D40       | A0  | В0       |

| D39       | A1  | B1       |

| D38       | A2  | B2       |

| D37       | A3  | B3 Note  |

| D36       | A4  | B4       |

| D35       | A5  | B5       |

| D34       | A6  | В6       |

| D33       | A7  | В7       |

| D32       | A8  | B8 Note  |

| D31       | A9  | В9       |

| D30       | A10 | B10      |

| D29       | A11 | B11      |

| D28       | A12 | B12      |

| D27       | A13 | B13 Note |

| D26       | A14 | B14      |

| D25       | A15 | B15      |

| D24       | A16 | B16      |

| D23       | A17 | B17      |

| D22       | A18 | B18 Note |

| D21       | A19 | B19      |

| D20       | A20 | B20      |

| D19       | A21 | B21      |

| D18       | A22 | B22      |

| D17       | A23 | B23 Note |

| D16       | A24 | B24      |

| D15       | A25 | B25      |

| D14       | A26 | B26      |

| D13       | A27 | B27      |

| D12       | A28 | B28      |

| D11       | A29 | B29      |

| D10       | A30 | B30      |

| Segment<br>Data Name | А   | В   |

|----------------------|-----|-----|

| D9                   | A31 | B31 |

| D8                   | A32 | B32 |

| D7                   | A33 | B33 |

| D6                   | A34 | B34 |

| D5                   | A35 | B35 |

| D4                   | A36 | B36 |

| D3                   | A37 | B37 |

| D2                   | A38 | B38 |

| D1                   | A39 | B39 |

Note The data of segments B3, B8, B13, B18, and B23 are invalid. Do not input anything for these data.

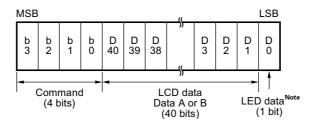

#### 4.2 LCD Display Data Configuration

LCD display data is divided into two parts, A and B, for transmission (refer to Table 4-2 Display Data Table).

The data consists of a command (4 bits), LCD data (40 bits), and LED data (1 bit), or a total of 45 bits (only when data A is transmitted. Data B consists of 44 bits, excluding LED data (1 bit)).

Figure 4-1. Configuration of Input Data for LCD Display

Note D0 (= LED data) is necessary only when data A is transmitted.

The status of the data can be identified by the data of each bit (0 or 1) as shown below.

| Data | Status        |  |  |

|------|---------------|--|--|

| 0    | Extinguishers |  |  |

| 1    | Lights        |  |  |

The last 4 bits of the input data is read at the rising edge of the LOAD pin (pin 28) as a command, and the previous data is displayed on the LCD when display data input is identified.

When a low level is input to the BLANK pin (pin 42), the LCD display is turned ON (the LED also lights when data A is transmitted). When a high level is input to the BLANK pin, the LCD display is turned OFF (refer to **5.2 Serial Data Output**).

Setting of the BLANK pin does not affect any operations other than the LCD display.

The LCD display data is extinguished in the initial status (even if the BLANK pin is low level).

The configuration of the LCD display data commands (4 bits of MSB) is shown below.

Table 4-3. Serial Data I/O Commands

|        | Comi   | mand |    | Operation                                  |  |

|--------|--------|------|----|--------------------------------------------|--|

| b3     | b2     | b1   | b0 | Operation                                  |  |

| 0      | 0      | 1    | 0  | Inputs display data (data A)               |  |

| 0      | 0      | 1    | 1  | Inputs display data (data B)               |  |

| 0      | 1      | 0    | ×  | Outputs key data                           |  |

| 0      | 1      | 1    | 0  | Inputs display data (A) + outputs key data |  |

| 0      | 1      | 1    | 1  | Inputs display data (B) + outputs key data |  |

| 1      | 1      | 0    | ×  | Outputs key data                           |  |

| 1      | 1      | 1    | ×  | Outputs key data                           |  |

| Others | Others |      |    | Setting prohibited                         |  |

×: Undefined

## 5. SERIAL DATA COMMUNICATION

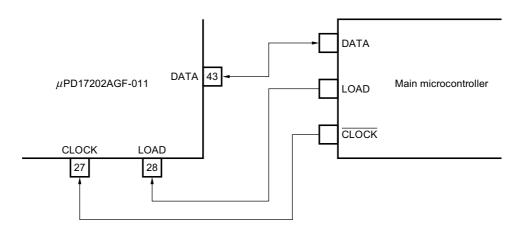

The  $\mu$ PD17202AGF-011 inputs or outputs data from or to the main microcontroller through 3-wire serial communication, using the CLOCK (pin 27), DATA (pin 43), and LOAD (pin 28) pins.

Figure 5-1 shows connection between the  $\mu$ PD17202AGF-011 and main microcontroller.

Figure 5-1. Connection between  $\mu$ PD17202AGF-011 and Main Microcontroller

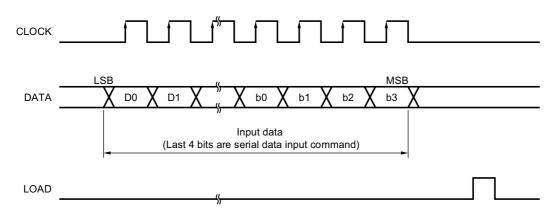

#### 5.1 Serial Data Input

The serial data is input in synchronization with the rising of the CLOCK pin (pin 27) in the input status (the initial status is "input").

The last 4 bits read at the rising edge of the LOAD pin (pin 28) are identified and processed as a command. Figure 5-2 shows the timing chart of serial data input.

Table 5-1 lists the serial data I/O commands.

Figure 5-2. Timing Chart of Serial Data Input

Table 5-1. Serial Data I/O Commands

|        | Command |    |    | Operation                                  |  |

|--------|---------|----|----|--------------------------------------------|--|

| b3     | b2      | b1 | b0 | Operation                                  |  |

| 0      | 0       | 1  | 0  | Inputs display data (data A)               |  |

| 0      | 0       | 1  | 1  | Inputs display data (data B)               |  |

| 0      | 1       | 0  | ×  | Outputs key data                           |  |

| 0      | 1       | 1  | 0  | Inputs display data (A) + outputs key data |  |

| 0      | 1       | 1  | 1  | Inputs display data (B) + outputs key data |  |

| 1      | 1       | 0  | ×  | Outputs key data                           |  |

| 1      | 1       | 1  | ×  | Outputs key data                           |  |

| Others |         |    |    | Setting prohibited                         |  |

#### ×: Undefined

Remarks 1. For the data configuration of display data input, refer to 4. LCD DISPLAY FUNCTION.

- 2. For the data configuration of key data output, refer to 3. KEY SCAN.

- 3. Execute display data input before key data output.

- **4.** If a pulse is input to the LOAD pin without display data input, the device does not operate.

- 5. The device does not operate when data other than an I/O command is input.

#### 5.2 Serial Data Output

Serial data is output in synchronization with the rising of the CLOCK pin (pin 27) in the output status (the output status is established only when the key data output command is executed).

Serial data is output in the following procedure. Figure 5-3 shows the timing chart of serial data output.

- <1> Input a key data output command.

- <2> Input a pulse to the LOAD pin (pin 28) (the output status is established when this pin goes high).

- <3> Input the clock (data is output in synchronization with the rising of the clock).

- <4> Input a pulse to the LOAD pin (the input status is established when this pin goes high).

CLOCK

LSB MSB LSB MSB

DATA X b0 X b1 X b2 X b3 X X K0 X K1 X K29

Input data

Output data

Output status

Input status

Output status

Figure 5-3. Timing Chart of Serial Data Output

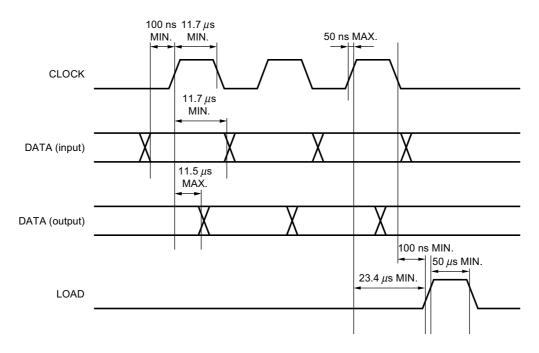

## 5.3 Timing Chart of Serial Data Communication

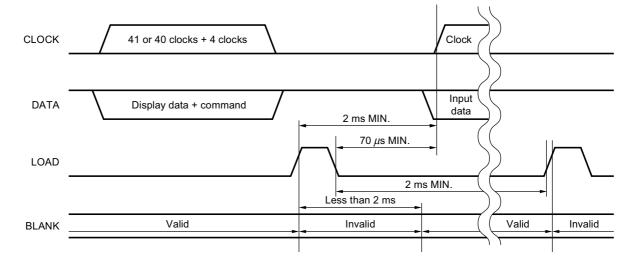

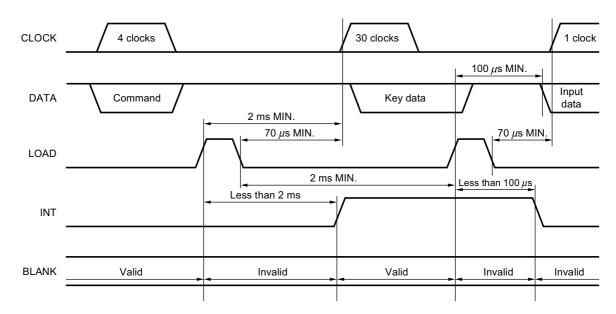

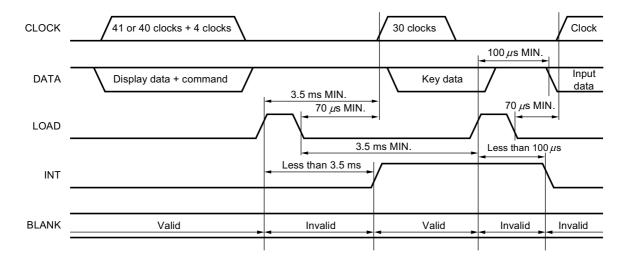

The I/O timing charts of the respective pins during serial data communication are shown below.

#### (1) Serial data I/O

Remark Maximum clock frequency: 43 kHz

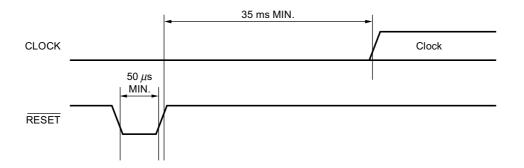

## (2) On reset execution

#### (3) On execution of display data input

/alid : The device operates within 50 μs after the value of the BLANK pin has been changed. If the clock is input to the CLOCK pin, however, the higher the clock frequency, the slower

the operation (example: operates within 1 ms at 43 kHz).

Invalid: The device does not operate even if the value of the BLANK pin has been changed. If

the value of the pin is changed during this period, the device operates after the pin value

has become valid.

#### (4) On execution of key data output

BLANK pin

Valid : The device operates within 50  $\mu$ s after the value of the BLANK pin has been changed.

If the clock is input to the CLOCK pin, however, the higher the clock frequency, the slower plane of the clock is input to the CLOCK pin, however, the higher the clock frequency is a slower plane of the clock is input to the CLOCK pin, however, the higher the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency in the clock frequency is a slower plane of the clock frequency

the operation (example: operates within 1 ms at 43 kHz).

nvalid: The device does not operate even if the value of the BLANK pin has been changed. If the value of the pin is changed during this period, the device operates after the pin value

has become valid.

## **NEC**

#### (5) On execution of display data input + key data

$\label{eq:bounds} \text{Valid} \quad : \quad \text{The device operates within 50 $\mu$s after the value of the BLANK pin has been changed.} \\ \text{BLANK pin} \quad \text{If the clock is input to the CLOCK pin, however, the higher the clock frequency, the slower the operation (example: operates within 1 ms at 43 kHz).} \\ \text{Invalid:} \quad \text{The device does not operate even if the value of the BLANK pin has been changed. If} \\ \text{Invalid:} \quad \text{The device does not operate even if the value of the BLANK pin has been changed.} \\ \text{Invalid:} \quad \text{The device does not operate even if the value of the BLANK pin has been changed.} \\ \text{Invalid:} \quad \text{The device does not operate even if the value of the BLANK pin has been changed.} \\ \text{Invalid:} \quad \text{The device does not operate even if the value of the BLANK pin has been changed.} \\ \text{Invalid:} \quad \text{The device does not operate even if the value of the BLANK pin has been changed.} \\ \text{Invalid:} \quad \text{The device does not operate even if the value of the BLANK pin has been changed.} \\ \text{Invalid:} \quad \text{The device does not operate even if the value of the BLANK pin has been changed.} \\ \text{Invalid:} \quad \text{The device does not operate even if the value of the BLANK pin has been changed.} \\ \text{Invalid:} \quad \text{The device does not operate even if the value of the BLANK pin has been changed.} \\ \text{Invalid:} \quad \text{The device operate even if the value of the BLANK pin has been changed.} \\ \text{The device operate even if the value of the BLANK pin has been changed.} \\ \text{The device operate even if the value of the BLANK pin has been changed.} \\ \text{The device operate even if the value of the BLANK pin has been changed.} \\ \text{The device operate even if the value of the BLANK pin has been changed.} \\ \text{The device operate even if the value of the BLANK pin has been changed.} \\ \text{The device operate even if the value of the BLANK pin has been changed.} \\ \text{The device operate even if the value of the BLANK pin has been changed.} \\ \text{The device operate even if the value of the BLANK pin has been changed.} \\ \text{The device operate even if the value ev$

the value of the pin is changed during this period, the device operates after the pin value

has become valid.

## 6. APPLICATION CIRCUIT EXAMPLE

## 7. ELECTRICAL SPECIFICATIONS (preliminary)

Absolute Maximum Ratings (T<sub>A</sub> = 25 °C)

| Parameter                 | Symbol          | Condition                    | Condition   |                               | Unit |

|---------------------------|-----------------|------------------------------|-------------|-------------------------------|------|

| Supply voltage            | V <sub>DD</sub> |                              |             | -0.3 to +7.0                  | V    |

| Input voltage             | Vı              |                              |             | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage            | Vo              |                              |             | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| High-level output current | Іон             | REM pin                      | Peak        | -30                           | mA   |

|                           |                 |                              | r.m.s value | -20                           | mA   |

|                           |                 | 1 pin                        | Peak        | -7.5                          | mA   |

|                           |                 | (other than REM pin)         | r.m.s value | -5.0                          | mA   |

|                           |                 | All pins<br>(except REM pin) | Peak        | -22.5                         | mA   |

|                           |                 |                              | r.m.s value | -15.0                         | mA   |

| Low-level output current  | Гог             | loL 1 pin                    | Peak        | 7.5                           | mA   |

|                           |                 |                              | r.m.s value | 5.0                           | mA   |

|                           |                 | All pins                     | Peak        | 30                            | mA   |

|                           |                 |                              | r.m.s value | 20                            | mA   |

| Operating temperature     | Та              |                              |             | —20 to +75                    | °C   |

| Storage temperature       | Tstg            |                              |             | -40 to +125                   | °C   |

Caution If the rated value of even one of the above parameters is exceeded even momentarily, the quality of the product may be affected. The absolute maximum ratings, therefore, define the values exceeding which the product may be physically damaged. Be sure to use the product without ever exceeding these values.

Capacitance (T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 0 V)

| Parameter         | Symbol | Condition                     | MIN. | TYP. | MAX. | Unit |

|-------------------|--------|-------------------------------|------|------|------|------|

| Input capacitance | Cin    | INT and RESET pins            |      |      | 10   | pF   |

|                   | CPIN   | Other than INT and RESET pins |      |      | 10   | pF   |

## Recommended Operation Range ( $T_A = -20 \text{ to } +75 ^{\circ}\text{C}$ )

| Parameter                          | Symbol           | Condition                        | MIN. | TYP. | MAX. | Unit |

|------------------------------------|------------------|----------------------------------|------|------|------|------|

| Supply voltage                     | V <sub>DD0</sub> | Where system clock is fx = 4 MHz |      | 3.0  | 5.5  | V    |

|                                    | V <sub>DD1</sub> | Where system clock is fx = 8 MHz | 4.5  | 5.0  | 5.5  | V    |

| System clock oscillation frequency | fx               |                                  | 1.0  | 4.0  | 8.0  | MHz  |

#### System Clock Oscillation Circuit Characteristics ( $T_A = -20 \text{ to } +75 ^{\circ}\text{C}$ , $V_{DD} = 2.2 \text{ to } 5.5 \text{ V}$ )

| Oscillator                  | Recommended<br>Constants | Parameter                             | Condition                                                                 | MIN. | TYP. | MAX. | Unit |

|-----------------------------|--------------------------|---------------------------------------|---------------------------------------------------------------------------|------|------|------|------|

| Ceramic<br>resonator Note 1 | Xin Xout                 | Oscillation frequency (fx) Note 2     |                                                                           | 1.0  | 4.0  | 8.0  | MHz  |

|                             |                          | Oscillation stabilization time Note 3 | After V <sub>DD</sub> has reached MIN. value of oscillation voltage range |      |      | 4    | ms   |

| Crystal resonator Note 1    | XIN XOUT                 | Oscillation frequency (fx) Note 2     |                                                                           | 1.0  | 4.0  | 8.0  | MHz  |

|                             |                          | Oscillation stabilization             | $V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$                                  |      |      | 10   | ms   |

|                             | <u></u>                  | time Note 3                           |                                                                           |      |      | 30   | ms   |

Notes 1. Use of the ceramic resonator and crystal resonator shown on the next page is recommended.

- 2. The oscillation frequency only indicates the characteristics of the oscillation circuit. For the instruction execution time, refer to **Recommended Operation Range**.

- 3. The oscillation stabilization time is the time required for oscillation to stabilize after VDD application or release of the STOP mode.

Caution When using the system clock oscillation circuit, wire the portion indicated by the dotted lines in the above figures to avoid adverse influence from wiring capacitance.

- · Keep the wiring length as short as possible.

- Do not cross the wiring with any other signal lines. Do not route the wiring in the vicinity of a line through which a high alternating current flows.

- Always keep the ground point of the capacitor of the oscillation circuit at the same potential as GND. Do not ground the capacitor to a ground pattern through which a high current flows.

- · Do not extract signals from the oscillation circuit.

#### **Recommended Oscillator**

## Ceramic resonator

| Manufacturer          | Part Number  | External Capacitance (pF) |        | Oscillation<br>Range (V | •    | Remark     |                |

|-----------------------|--------------|---------------------------|--------|-------------------------|------|------------|----------------|

|                       |              | C1                        | C2     | MIN.                    | MAX. |            |                |

| Murata Mfg. Co., Ltd. | CSA3.58MG    | 30                        | 30     | 2.0                     | 6.0  |            |                |

|                       | CSA4.00MG    | 30                        | 30     | 2.0                     | 6.0  |            |                |

|                       | CSA4.19MG    | 30                        | 30     | 2.0                     | 6.0  |            |                |

|                       | CST3.58MGW   | Unnec-                    | Unnec- | 2.0                     | 6.0  | Capacitor- |                |

|                       | CST4.00MGW   | essary                    | essary | essary                  | 2.0  | 6.0        | contained type |

|                       | CST4.19MGW   |                           |        | 2.0                     | 6.0  |            |                |

| Kyocera Corp.         | KBR3.58MS    | 33                        | 33     | 2.0                     | 6.0  |            |                |

|                       | KBR4.0MS     | 33                        | 33     | 2.0                     | 6.0  |            |                |

|                       | KRB4.19MS    | 33                        | 33     | 2.0                     | 6.0  |            |                |

| Toko Ceramic Co. Ltd. | CRHF4.00     | 18                        | 18     | 2.0                     | 6.0  |            |                |

| Daishinku Corp.       | PRS0400BCSAN | 39                        | 33     | 2.0                     | 6.0  |            |                |

## Crystal resonator

| Manufacturer  | Frequency<br>(MHz) | Potoinor |    | External<br>Capacitance (pF) |      | n Voltage<br>) | Remark |

|---------------|--------------------|----------|----|------------------------------|------|----------------|--------|

|               | (141112)           |          | C1 | C2                           | MIN. | MAX.           |        |

| Kinseki Corp. | 4.0                | HC-49U-S | 22 | 22                           | 2.0  | 6.0            |        |

## **External Circuit Example**

## DC Characteristics ( $V_{DD}$ = 3 V, $T_A$ = -20 to +75 °C, $f_X$ = 4 MHz)

| Parameter                         | Symbol            | Condit                                         | ion                                           | MIN.                | TYP.    | MAX.                | Unit |

|-----------------------------------|-------------------|------------------------------------------------|-----------------------------------------------|---------------------|---------|---------------------|------|

| Low-voltage detection voltage     | VDET              | R = 2.2 MΩ                                     |                                               | 1.3                 | 2.0     | 2.9                 | V    |

| High-level input voltage          | V <sub>IH1</sub>  | RESET, INT pins                                |                                               | 0.8 V <sub>DD</sub> |         | V <sub>DD</sub>     | V    |

|                                   | V <sub>IH2</sub>  | Other than RESET, IN                           | Γpins                                         | 0.7 VDD             |         | V <sub>DD</sub>     | V    |

| Low-level input voltage           | V <sub>IL1</sub>  | RESET, INT pins                                |                                               | 0                   |         | 0.2 V <sub>DD</sub> | V    |

|                                   | V <sub>IL2</sub>  | Other than RESET, IN                           | Γpins                                         | 0                   |         | 0.3 V <sub>DD</sub> | V    |

| High-level input current          | I <sub>IH1</sub>  | INT pin                                        | V <sub>IH</sub> = V <sub>DD</sub>             |                     |         | 0.2                 | μΑ   |

|                                   | I <sub>IH2</sub>  | RESET pin                                      | V <sub>IH</sub> = V <sub>DD</sub>             |                     |         | 0.2                 | μΑ   |

|                                   | Іінз              | P0A through P0D pins                           | V <sub>IH</sub> = V <sub>DD</sub>             |                     |         | 0.2                 | μΑ   |

| Low-level input current           | IIL1              | INT pin                                        | VIL = 0 V                                     |                     |         | -0.2                | μΑ   |

|                                   | l <sub>IL2</sub>  | RESET pin                                      | V <sub>IL</sub> = 0 V<br>w/o pull-up resistor |                     |         | -0.2                | μΑ   |

|                                   | IIL3              |                                                | V <sub>IL</sub> = 0 V<br>w/pull-up resistor   | -30                 | -60     | -120                | μА   |

|                                   | l <sub>IL4</sub>  | P0A, P0B pins                                  | V <sub>IL</sub> = 0 V<br>w/o pull-up resistor |                     |         | -0.2                | μΑ   |

|                                   | I <sub>IL5</sub>  |                                                | V <sub>IL</sub> = 0 V<br>w/pull-up resistor   | -8                  | -15     | -30                 | μΑ   |

|                                   | IIL6              | P0C, P0D pins                                  | VIL = 0 V                                     |                     |         | -0.2                | μΑ   |

| High-level output current         | Іон1              | P0A, P0B pins                                  | V <sub>OH</sub> = V <sub>DD</sub> - 0.3 V     | -0.6                | -2.0    | -4.0                | mA   |

|                                   | <b>І</b> он2      | REM pin                                        | V <sub>OH</sub> = V <sub>DD</sub> - 2.0 V     | -7.0                | -15.0   | -25.0               | mA   |

|                                   | Іонз              | LED pin                                        | VoH = VDD - 0.3 V                             | -0.3                | -1.0    | -2.0                | mA   |

| Low-level output current          | lo <sub>L1</sub>  | P0A, P0B pins                                  | Vol = 0.3 V                                   | 0.5                 | 1.5     | 2.5                 | mA   |

|                                   | lol2              | P0C, P0D pins                                  | Vol = 0.3 V                                   | 0.5                 | 1.5     | 2.5                 | mA   |

|                                   | Іоьз              | REM pin                                        | Vol = 0.3 V                                   | 0.5                 | 1.5     | 2.5                 | mA   |

|                                   | lo <sub>L4</sub>  | LED, WDOUT pins                                | Vol = 0.3 V                                   | 0.5                 | 1.5     | 2.5                 | mA   |

| Supply current                    | I <sub>DD1</sub>  | Operating mode                                 |                                               |                     | 0.6     | 1.5                 | mA   |

|                                   | I <sub>DD2</sub>  | HALT mode                                      |                                               |                     | 0.5     | 1.5                 | mA   |

| VLCDC voltage                     | VLCDC             | V <sub>DD</sub> = 3 V, T <sub>A</sub> = 25 °C, | R1 = R2 = 1 MΩ                                | 0.5                 | 0.6     | 0.7                 | V    |

| LCD output voltage variable range | V <sub>LCD0</sub> | External variable resist                       | or (0 to 2.2 MΩ)                              | 0.8                 |         | 1.8                 | V    |

| Doubler output voltage            | V <sub>LCD1</sub> | C1 to C4 = 0.47 µF                             |                                               | 1.9 VLCD0           | 2 VLCD0 |                     | V    |

| Tripler output voltage            | V <sub>LCD2</sub> | C1 to C4 = 0.47 µF                             |                                               | 2.85 VLCD0          | 3 VLCD0 |                     | V    |

| Common output current             | Ісом              | V <sub>DS</sub> = 0.2 V                        |                                               | 30                  |         |                     | μΑ   |

| Segment output current            | ILCD              | V <sub>DS</sub> = 0.2 V                        | V <sub>DS</sub> = 0.2 V                       |                     |         |                     | μΑ   |

## AC Characteristics (T<sub>A</sub> = -20 to +75 °C, V<sub>DD</sub> = 3 V)

| Parameter                   | Symbol | Condition | MIN. | TYP. | MAX. | Unit |

|-----------------------------|--------|-----------|------|------|------|------|

| INT high-, low-level widths | tіон   |           | 50   |      |      | μs   |

|                             | tioL   |           | 50   |      |      | μs   |

| RESET low-level width       | trsL   |           | 50   |      |      | μs   |

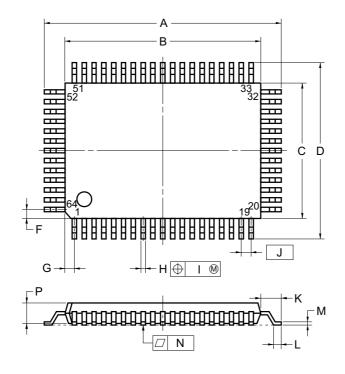

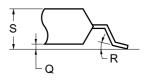

## 8. PACKAGE DRAWINGS

## 64 PIN PLASTIC QFP (14×20)

detail of lead end

#### NOTE

Each lead centerline is located within 0.20 mm (0.008 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| Α    | 23.2±0.2               | $0.913^{+0.009}_{-0.008}$ |

| В    | 20.0±0.2               | $0.787^{+0.009}_{-0.008}$ |

| С    | 14.0±0.2               | 0.551+0.009               |

| D    | 17.2±0.2               | 0.677±0.008               |

| F    | 1.0                    | 0.039                     |

| G    | 1.0                    | 0.039                     |

| Н    | 0.40±0.10              | $0.016^{+0.004}_{-0.005}$ |

| ı    | 0.20                   | 0.008                     |

| J    | 1.0 (T.P.)             | 0.039 (T.P.)              |

| K    | 1.6±0.2                | 0.063±0.008               |

| L    | 0.8±0.2                | $0.031^{+0.009}_{-0.008}$ |

| М    | $0.15^{+0.10}_{-0.05}$ | $0.006^{+0.004}_{-0.003}$ |

| N    | 0.10                   | 0.004                     |

| Р    | 2.7                    | 0.106                     |

| Q    | 0.125±0.075            | 0.005±0.003               |

| R    | 5°±5°                  | 5°±5°                     |

| S    | 3.0 MAX.               | 0.119 MAX.                |

|      |                        |                           |

S64GF-100-3B8, 3BE-3

#### NOTES FOR CMOS DEVICES —

## (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note: Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

## (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note: No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS device behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note: Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

## **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 800-366-9782 Fax: 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.1.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### **NEC Electronics (Germany) GmbH**

Benelux Office Eindhoven, The Netherlands Tel: 040-2445845

Fax: 040-244580

#### **NEC Electronics (France) S.A.**

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### **NEC Electronics (France) S.A.**

Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

#### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### **NEC Electronics Singapore Pte. Ltd.**

United Square, Singapore 1130 Tel: 253-8311

Tel: 253-8311 Fax: 250-3583

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-719-2377 Fax: 02-719-5951

#### **NEC do Brasil S.A.**

Sao Paulo-SP, Brasil Tel: 011-889-1680 Fax: 011-889-1689

J96. 8

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5