# μPD8080AF 8-BIT N-CHANNEL MICROPROCESSOR FAMILY

#### **DESCRIPTION**

The  $\mu$ PD8080AF is a complete 8-bit parallel processor for use in general purpose digital computer systems. It is fabricated on a single LSI chip using N-channel silicon gate MOS process, which offers much higher performance than conventional microprocessors (1.28  $\mu$ s minimum instruction cycle). A complete microcomputer system is formed when the  $\mu$ PD8080AF is interfaced with I/O ports (up to 256 input and 256 output ports) and any type or speed of semiconductor memory. It is available in a 40 pin ceramic or plastic package.

#### **FEATURES**

- 78 Powerful Instructions

- Three Devices Three Clock Frequencies μPD8080AF – 2.0 MHz μPD8080AF-2 – 2.5 MHz μPD8080AF-1 – 3.0 MHz

- Direct Access to 64K Bytes of Memory with 16-Bit Program Counter

- 256 8-Bit Input Ports and 256 8-Bit Output Ports

- Double Length Operations Including Addition

- · Automatic Stack Memory Operation with 16-Bit Stack Pointer

- TTL Compatible (Except Clocks)

- Multi-byte Interrupt Capability

- Fully Compatible with Industry Standard 8080A

- · Available in either Plastic or Ceramic Package

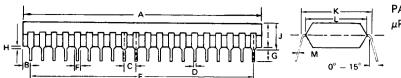

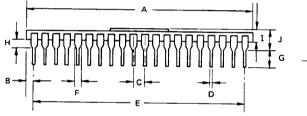

#### PIN CONFIGURATION

## µPD8080AF

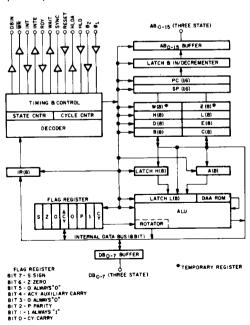

The  $\mu$ PD8080AF contains six 8-bit data registers, an 8-bit accumulator, four testable flag bits, and an 8-bit parallel binary arithmetic unit. The  $\mu$ PD8080AF also provides decimal arithmetic capability and it includes 16-bit arithmetic and immediate operators which greatly simplify memory address calculations, and high speed arithmetic operations.

The µPD8080AF utilizes a 16-bit address bus to directly address 64K bytes of memory, is TTL compatible (1.9 mA), and utilizes the following addressing modes: Direct; Register; Register Indirect; and Immediate.

The µPD8080AF has a stack architecture wherein any portion of the external memory can be used as a last in/first out (LIFO) stack to store/retrieve the contents of the accumulator, the flags, or any of the data registers.

The  $\mu$ PD8080AF also contains a 16-bit stack pointer to control the addressing of this external stack. One of the major advantages of the stack is that multiple level interrupts can easily be handled since complete system status can be saved when an interrupt occurs and then restored after the interrupt is complete. Another major advantage is that almost unlimited subroutine nesting is possible.

This processor is designed to greatly simplify system design. Separate 16-line address and 8-line bidirectional data buses are employed to allow direct interface to memories and I/O ports. Control signals, requiring no decoding, are provided directly by the processor. All buses, including the control bus, are TTL compatible.

Communication on both the address lines and the data lines can be interlocked by using the HOLD input. When the Hold Acknowledge (HLDA) signal is issued by the processor, its operation is suspended and the address and data lines are forced to be in the FLOATING state. This permits other devices, such as direct memory access channels (DMA), to be connected to the address and data buses.

The  $\mu$ PD8080AF has the capability to accept a multiple byte instruction upon an interrupt. This means that a CALL instruction can be inserted so that any address in the memory can be the starting location for an interrupt program. This allows the assignment of a separate location for each interrupt operation, and as a result no polling is required to determine which operation is to be performed.

NEC offers three versions of the  $\mu$ PD8080AF. These processors have all the features of the  $\mu$ PD8080AF except the clock frequency ranges from 2.0 MHz to 3.0 MHz. These units meet the performance requirements of a variety of systems while maintaining software and hardware compatibility with other 8080A devices.

FUNCTIONAL DESCRIPTION

BLOCK DIAGRAM

## PIN IDENTIFICATION

| _                              |                                 |                                         | μι Doddoni                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------|---------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                                 | PIN                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NO.                            | SYMBOL                          | NAME                                    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1,<br>25 <b>-2</b> 7,<br>29-40 | A15 - A0                        | Address Bus<br>(output three-<br>state) | The address bus is used to address memory (up to 64K 8-bit words) or specify the I/O device number (up to 256 input and 256 output devices). Ag is the least significant bit.                                                                                                                                                                                                                                                                                             |

| 2                              | VSS                             | Ground (input)                          | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

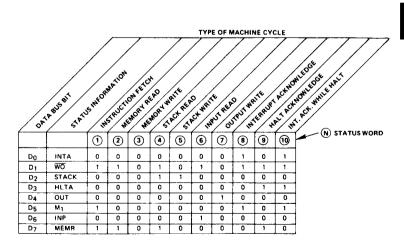

| 3-10                           | D <sub>7</sub> — D <sub>0</sub> | Data Bus (input/<br>output three-state) | The bidirectional data bus communicates between the processor,<br>memory, and I/O devices for instructions and data transfers. Dur-<br>ing each sync time, the data bus contains a status word that<br>describes the current machine cycle. Do is the least significant bit.                                                                                                                                                                                              |

| 11                             | VBB                             | VBB Supply Voltage (input)              | -5V ± 5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12                             | RESET                           | Reset (input)                           | If the RESET signal is activated, the program counter is cleared.<br>After RESET, the program starts at location 0 in memory. The INTE and HLDA flip-flops are also reset. The flags, accumulator, stack pointer, and registers are not cleared. (Note: External synchronization is not required for the RESET input signal which must be active for a minimum of 3 clock periods.)                                                                                       |

| 13                             | HOLD                            | Hold (input)                            | HOLD requests the processor to enter the HOLD state. The HOLD state allows an external device to gain control of the µPD8080AF address and data buses as soon as the µPD8080AF has completed its use of these buses for the current machine cycle. It is recognized under the following conditions:  The processor is in the HALT state.  The processor is in the T2 or TW stage and the READY signal is active.  As a result of entering the HOLD state, the ADDRESS BUS |

|                                |                                 |                                         | (A15 – A0) and DATA BUS (D7 – D0) are in their high impedance state. The processor indicates its state on the HOLD ACKNOWLEDGE (HLDA) pin.                                                                                                                                                                                                                                                                                                                                |

| 14                             | INT                             | Interrupt Request<br>(input)            | The µPD8080AF recognizes an interrupt request on this line at the end of the current instruction or while halted. If the µPD8080AF is in the HOLD state, or if the Interrupt Enable flip-flop is reset, it will not honor the request.                                                                                                                                                                                                                                    |

| 15                             | φ2                              | Phase Two (input)                       | Phase two of processor clock.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16                             | INTE ①                          | Interrupt Enable<br>(output)            | INTE indicates the content of the internal interrupt enable flip-flop. This flip-flop is set by the Enable (EI) or reset by the Disable (DI) interrupt instructions and inhibits interrupts from being accepted by the processor when it is reset. INTE is automatically reset (disabling further interrupts) during T <sub>1</sub> of the instruction fetch cycle (M <sub>1</sub> ) when an interrupt is accepted and is also reset by the RESET signal.                 |

| 17                             | DBIN                            | Data Bus In<br>(output)                 | DBIN indicates that the data bus is in the input mode. This signal is used to enable the gating of data onto the $\mu$ PD8080AF data bus from memory or input ports.                                                                                                                                                                                                                                                                                                      |

| 18                             | WR                              | Write (output)                          | $\overline{WR}$ is used for memory WRITE or I/O output control. The data on the data bus is valid while the $\overline{WR}$ signal is active ( $\overline{WR}$ = 0).                                                                                                                                                                                                                                                                                                      |

| 19                             | SYNC                            | Synchronizing Signal<br>(output)        | The SYNC signal indicates the beginning of each machine cycle.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 20                             | vcc                             | VCC Supply<br>Voltage (input)           | +5V ± 5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21                             | HLDA                            | Hold Acknowledge<br>(output)            | HLDA is in response to the HOLD signal and indicates that the data and address bus will go to the high impedance state. The                                                                                                                                                                                                                                                                                                                                               |

## uPD8080AF

| Operating Temperature                       | +70°C ABSOLUTE MAXIMUM |

|---------------------------------------------|------------------------|

| Storage Temperature65°C to                  |                        |

| All Output Voltages0.3 to +2                | 0 Volts                |

| All Input Voltages ①0.3 to +2               | 0 Volts                |

| Supply Voltages VCC, VDD and VSS ①0.3 to +2 | O Volts                |

| Power Dissipation                           | 1.5W                   |

| Note: ① Relative to VBB.                    |                        |

| $T_a = 25^{\circ}C$                         |                        |

\*COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device

$T_a = 0^{\circ} C \text{ to } +70^{\circ} C$ ,  $V_{DD} = +12 V \pm 5\%$ ,  $V_{CC} = +5 V \pm 5\%$ ,  $V_{BB} = -5 V \pm 5\%$ ,  $V_{SS} = 0 V$ ,

|                                             |                 |                     | LIM  | ITS                   |          | -                                                                                                                        |

|---------------------------------------------|-----------------|---------------------|------|-----------------------|----------|--------------------------------------------------------------------------------------------------------------------------|

| PARAMETER                                   | SYMBOL          | MIN                 | TYP  | MAX                   | UNIT     | TEST CONDITIONS                                                                                                          |

| Clock Input Low<br>Voltage                  | VILC            | VSS - 1             |      | V <sub>SS</sub> + 0.8 | v        |                                                                                                                          |

| Clock Input High<br>Voltage                 | VIHC            | 9.0                 |      | V <sub>DD</sub> + 1   | ٧        |                                                                                                                          |

| Input Low Voltage                           | VIL             | V <sub>SS</sub> - 1 |      | V <sub>SS</sub> + 0.8 | V        |                                                                                                                          |

| Input High Voltage                          | VIH             | 3.3                 |      | Vcc + 1               | V        |                                                                                                                          |

| Output Low Voltage                          | VOL             |                     |      | 0.45                  | ٧        | IOL = 1.9 mA on all outputs                                                                                              |

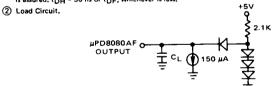

| Output High Voltage                         | Voн             | 3.7                 |      |                       | V        | IOH = - 150 μΑ ②                                                                                                         |

| Avg. Power Supply<br>Current (VDD)          | IDD(AV)         |                     | 40   | 70                    | mA       |                                                                                                                          |

| Avg. Power Supply<br>Current (VCC)          | ICC(AV)         |                     | 60   | 80                    | mA       | tCY min                                                                                                                  |

| Avg. Power Supply<br>Current (VBB)          | (BB(AV)         |                     | 0.01 | 1                     | mA       |                                                                                                                          |

| Input Leakage                               | IL              |                     |      | ±10 ②                 | μА       | VSS < VIN < VCC                                                                                                          |

| Clock Leakage                               | <sup>I</sup> CL |                     |      | ±10 ②                 | μΑ       | VSS ≤ VCLOCK ≤ VDD                                                                                                       |

| Data Bus Leakage<br>in Input Mode           | יסג 🛈           |                     |      | -100<br>-2 ②          | μA<br>mA | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>SS</sub> + 0.8V<br>V <sub>SS</sub> + 0.8V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> |

| Address and Data Bus<br>Leakage During HOLD | lŧį             |                     |      | +10<br>- 100 ②        | μА       | VADDR/DATA * VCC<br>VADDR/DATA * VSS + 0.45V                                                                             |

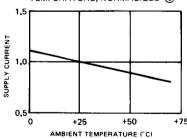

#### TYPICAL SUPPLY CURRENT VS. TEMPERATURE, NORMALIZED ③

- Notes: 1 When DBIN is high and  $V_{IN} > V_{IH}$  internal active pull-up resistors will be switched onto the data bus,

- ② Minus (-) designates current flow out of the device. ③  $\Delta I \text{ supply/} \Delta T_a = -0.45\%/^{\circ}C$ .

$T_a = 25^{\circ}C$ ,  $V_{CC} = V_{DD} = V_{SS} = 0V$ ,  $V_{RR} = -5V$ .

|                    | ,      |     |       |     |      |                        |

|--------------------|--------|-----|-------|-----|------|------------------------|

|                    |        |     | LIMIT | S   |      |                        |

| PARAMETER          | SYMBOL | MIN | TYP   | MAX | UNIT | TEST CONDITIONS        |

| Clock Capacitance  | Cφ     |     | 17    | 25  | ρF   | f <sub>c</sub> = 1 MHz |

| Input Capacitance  | CIN    |     | 6     | 10  | pF   | Unmeasured Pins        |

| Output Capacitance | COUT   | 1   | 10    | 20  | ρF   | Returned to VSS        |

CAPACITANCE

DC CHARACTERISTICS

# AC CHARACTERISTICS μPD8080AF

$T_a = 0^{\circ}\text{C to} + 70^{\circ}\text{C}$ ,  $V_{DD} = +12\text{V} \pm 5\%$ ,  $V_{CC} = +5\text{V} \pm 5\%$ ,  $V_{BB} = -5\text{V} \pm 5\%$ ,  $V_{SS} = 0\text{V}$ , unless otherwise specified.

|                                                                 |                                 |      | LIMITS |                 |      |                             |

|-----------------------------------------------------------------|---------------------------------|------|--------|-----------------|------|-----------------------------|

| PARAMETER                                                       | SYMBOL                          | MIN  | TYP    | MAX             | UNIT | TEST CONDITIONS             |

| Clock Period                                                    | tCY 3                           | 0.48 |        | 2.0             | μsec |                             |

| Clock Rise and Fall Time                                        | t <sub>r</sub> , t <sub>f</sub> | 0    |        | 50              | nsec |                             |

| φ1 Pulse Width                                                  | t <sub>Ø</sub> 1                | -60  |        |                 | nsec |                             |

| φ2 Pulse Width                                                  | t <sub>Ø</sub> 2                | 220  |        | -               | nsec | ,                           |

| Delay φ1 to φ2                                                  | <sup>t</sup> D1                 | 0    |        |                 | nsec |                             |

| Delay $\phi$ 2 to $\phi$ 1                                      | tD2                             | 70   |        |                 | nsec |                             |

| Delay $\phi$ 1 to $\phi$ 2 Leading Edges                        | tD3                             | 80   |        |                 | nsec |                             |

| Address Output Delay From #2                                    | tDA ②                           |      |        | 200             | nsec | 0 100 - 5                   |

| Data Output Delay From ¢2                                       | tpp ②                           |      |        | 220             | nsec | CL = 100 pF                 |

| Signal Output Delay From φ1,<br>or φ2 (SYNC, WR, WAIT,<br>HLDA) | tDC ②                           |      |        | 120             | nsec | C <sub>L</sub> = 50 pF      |

| DBIN Delay From Ø2                                              | tDF ②                           | 25   | 1      | 140             | nsec |                             |

| Delay for Input Bus to Enter<br>Input Mode                      | t <sub>DI</sub> ①               |      |        | <sup>t</sup> DF | nsec |                             |

| Data Setup Time During φ1 and DB1N                              | <sup>†</sup> DS1                | 30   |        |                 | nsec |                             |

| Data Setup Time to φ2 During DBIN                               | <sup>t</sup> DS2                | 150  |        |                 | nsec |                             |

| Data Hold Time From φ2 During<br>DBIN                           | ton ①                           | 0    |        |                 | nsec |                             |

| INTE Output Delay From φ2                                       | tIE ②                           |      |        | 200             | nsec | C <sub>L</sub> = 50 pF      |

| READY Setup Time During φ2                                      | tRS                             | 120  |        | Ĺ               | nsec |                             |

| HOLD Setup Time to φ2                                           | tHS                             | 140  |        |                 | nsec |                             |

| INT Setup Time During φ2 (During φ1 in Halt Mode)               | tis                             | 120  |        |                 | nsec |                             |

| Hold Time from φ2 (READY, INT, HOLD)                            | ŧн                              | 0    |        |                 | nsec |                             |

| Delay to Float During Hold<br>(Address and Data Bus)            | tFD                             |      |        | 120             | nsec |                             |

| Address Stable Prior to WR                                      | taw ②                           | (§   |        |                 | nsec |                             |

| Output Data Stable Prior to WR                                  | tow ②                           | 6    |        |                 | nsec |                             |

| Output Data Stable From WR                                      | two ②                           | 0    |        | 1               | nsec | CL = 100 pF: Addres         |

| Address Stable from WR                                          | twa ②                           | 0    |        | Ī               | nsec | Data                        |

| HLDA to Float Delay                                             | the 2                           | 8    |        | 1               | nsec | C <sub>L</sub> ≈ 50 pF: WR, |

| WR to Float Delay                                               | twe ②                           | 9    |        |                 | nsec | HLDA, DBIN                  |

| Address Hold Time after DBIN during HLDA                        | tan ②                           | -20  |        |                 | nsec | 1                           |

Notes: ① Data input should be enabled with DBIN status. No bus conflict can then occur and data hold time is assured. tpH = 50 ns or tpF, whichever is less.

3 Actual tCY =  $t_{D3} + t_{r\phi2} + t_{\phi2} + t_{f\phi2} + t_{D2} + t_{r\phi1} > t_{CY}$  Min.

$T_a = 0^{\circ} C$  to +70° C,  $V_{DD} = +12 V \pm 5\%$ ,  $V_{CC} = +5 V \pm 5\%$ ,  $V_{BB} = -5 V \pm 5\%$ ,  $V_{SS} = 0 V$ , unless otherwise specified.

AC CHARACTERISTICS μPD8080AF-1

|                                                                 |                                 |      | LIMITS |     |      |                                       |

|-----------------------------------------------------------------|---------------------------------|------|--------|-----|------|---------------------------------------|

| PARAMETER                                                       | SYMBOL                          | MIN  | TYP    | MAX | UNIT | TEST CONDITIONS                       |

| Clock Period                                                    | tcy ③                           | 0,32 |        | 2.0 | μsec |                                       |

| Clock Rise and Fall Time                                        | t <sub>r</sub> , t <sub>f</sub> | 0    |        | 25  | nsec |                                       |

| φ1 Pulse Width                                                  | <sup>t</sup> ø1                 | 50   |        |     | nsec |                                       |

| φ2 Pulse Width                                                  | t <sub>Ø</sub> 2                | 145  |        |     | nsec |                                       |

| Delay $\phi$ 1 to $\phi$ 2                                      | <sup>t</sup> D1                 | 0    |        |     | nsec | · · · · · · · · · · · · · · · · · · · |

| Delay φ2 to φ1                                                  | †D2                             | 60   |        |     | nsec |                                       |

| Delay φ1 to φ2 Leading Edges                                    | <sup>t</sup> D3                 | 60   |        |     | nsec |                                       |

| Address Output Delay From $\phi2$                               | tDA ②                           |      |        | 150 | nsec | C <sub>1</sub> = 100 pF               |

| Data Output Delay From $\phi2$                                  | too ②                           |      |        | 180 | nsec | C[ + 100 pr                           |

| Signal Output Delay From φ1,<br>or φ2 (SYNC, WR, WAIT,<br>HLDA) | ¹pc ②                           |      |        | 110 | nsec | C <sub>L</sub> = 50 pF                |

| DBIN Delay From ¢2                                              | tDF ②                           | 25   |        | 130 | пѕес |                                       |

| Delay for Input Bus to Enter<br>Input Mode                      | t <sub>DI</sub> ①               |      |        | †DF | пѕес |                                       |

| Data Setup Time During $\phi 1$ and DBIN                        | t <sub>DS1</sub>                | 10   |        |     | nsec |                                       |

| Data Setup Time to φ2 During<br>DBIN                            | <sup>†</sup> DS2                | 120  |        |     | nsec |                                       |

| Data Hold Time From ¢2 During<br>DBIN                           | трн ①                           | 0    |        |     | nsec |                                       |

| INTE Output Delay From $\phi2$                                  | tiE ②                           |      |        | 200 | nsec | C <sub>L</sub> = 50 pF                |

| READY Setup Time During ¢2                                      | tRS                             | 90   |        |     | nsec |                                       |

| HOLD Setup Time to φ2                                           | tHS                             | 120  |        |     | nsec |                                       |

| tNT Setup Time During ¢2<br>(for all modes)                     | tis                             | 100  |        |     | nsec |                                       |

| Hold Time from φ2 (READY,<br>INT, HOLD)                         | t <sub>H</sub>                  | 0    |        |     | nsec |                                       |

| Delay to Float During Hold<br>(Address and Data Bus)            | <sup>t</sup> FD                 |      |        | 120 | nsec |                                       |

| Address Stable Prior to WR                                      | taw ②                           | (5)  |        |     | nsec |                                       |

| Output Data Stable Prior to WR                                  | tow ②                           | 6    |        |     | nsec |                                       |

| Output Data Stable From WR                                      | two ②                           | 0    |        |     | nsec | CL = 100 pF: Address,                 |

| Address Stable from WR                                          | twa ②                           | 0    |        |     | nsec | Data                                  |

| HLDA to Float Delay                                             | the ②                           | 8    |        |     | nsec | C <sub>L</sub> = 50 pF: WR,           |

| WR to Float Delay                                               | twr ②                           | 9    |        |     | nsec | HLDA, DBIN                            |

| Address Hold Time after DBIN during HLDA                        | tан ②                           | -20  |        |     | nsec |                                       |

#### Notes Continued:

- 4 The following are relevant when interfacing the  $\mu$ PD8080AF to devices having  $V_{IH} = 3.3V$ .

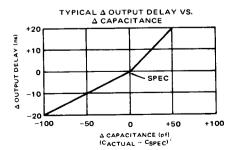

- a. Maximum output rise time from 0.8V to 3.3V = 100 ns at  $C_L$  = SPEC. b. Output delay when measured to 3.0V = SPEC +60 ns at  $C_L$  = SPEC. c. If  $C_L \neq$  SPEC, add 0.6 ns/pF if  $C_L > C_{SPEC}$ , subtract 0.3 ns/pF (from modified delay) if  $C_L < C_{SPEC}$ .

#### **AC CHARACTERISTICS** μPD8080AF-2

$T_a = 0^{\circ} C \text{ to } +70^{\circ} C$ ,  $V_{DD} = +12 V \pm 5\%$ ,  $V_{CC} = +5 V \pm 5\%$ ,  $V_{BB} = -5 V \pm 5\%$ ,  $V_{SS} = 0 V$ , unless otherwise specified.

|                                                                                           |                                 |          | IMITS |                 |      |                                 |  |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------|----------|-------|-----------------|------|---------------------------------|--|--|--|

| PARAMETER                                                                                 | SYMBOL                          | MIN      | TYP   | MAX             | UNIT | TEST CONDITIONS                 |  |  |  |

| Clock Period                                                                              | ích ③                           | 0,38     |       | 2,0             | μsec |                                 |  |  |  |

| Clock Rise and Fall Time                                                                  | t <sub>r</sub> , t <sub>f</sub> | 0        |       | 50              | nsec |                                 |  |  |  |

| φ1 Pulse Width                                                                            | t <sub>Ø</sub> 1                | 60       |       |                 | nsec |                                 |  |  |  |

| φ2 Pulse Width                                                                            | t <sub>Ø</sub> 2                | 175      |       |                 | nsec |                                 |  |  |  |

| Delay $\phi$ 1 to $\phi$ 2                                                                | <sup>†</sup> D1                 | 0        |       |                 | nsec |                                 |  |  |  |

| Delay $\phi$ 2 to $\phi$ 1                                                                | tD2                             | 70       |       |                 | nsec |                                 |  |  |  |

| Delay $\phi$ 1 to $\phi$ 2 Leading Edges                                                  | t <sub>D3</sub>                 | 70       |       |                 | nsec |                                 |  |  |  |

| Address Output Delay From $\phi2$                                                         | ¹DA ②                           |          |       | 175             | nsec | C 100 - E                       |  |  |  |

| Data Output Delay From ¢2                                                                 | too ②                           |          |       | 200             | nsec | C <sub>L</sub> = 100 pF         |  |  |  |

| Signal Output Delay From $\phi$ 1,<br>or $\phi$ 2 (SYNC, $\overline{WR}$ , WAIT,<br>HLDA) | tDC ②                           |          |       | 120             | nsec | C <sub>L</sub> = 50 pF          |  |  |  |

| DB1N Delay From $\phi2$                                                                   | tDF ②                           | 25       |       | 140             | nsec |                                 |  |  |  |

| Delay for Input Bus to Enter<br>Input Mode                                                | נםו 🛈                           |          |       | t <sub>DF</sub> | nsec |                                 |  |  |  |

| Data Setup Time During $\phi$ 1 and DBIN                                                  | t <sub>DS1</sub>                | 20       |       |                 | nsec |                                 |  |  |  |

| Data Setup Time to $\phi2$ During<br>DBIN                                                 | <sup>t</sup> DS2                | 130      |       |                 | nsec |                                 |  |  |  |

| Data Hold Time From $\phi$ 2 During DBIN                                                  | tDH ①                           | 0        |       |                 | nsec |                                 |  |  |  |

| INTE Output Delay From $\phi$ 2                                                           | tIE ②                           |          |       | 200             | nsec | CL = 50 pF                      |  |  |  |

| READY Setup Time During #2                                                                | †RS                             | 90       |       |                 | nsec |                                 |  |  |  |

| HOLD Setup Time to φ2                                                                     | tHS                             | 120      |       | L               | nsec |                                 |  |  |  |

| INT Setup Time During φ2 (for all modes)                                                  | tis                             | 100      |       |                 | nsec |                                 |  |  |  |

| Hold Time from φ2 (READY,<br>INT, HOLD)                                                   | tH                              | 0        |       |                 | nsec |                                 |  |  |  |

| Delay to Float During Hold<br>(Address and Data Bus)                                      | tFD                             |          |       | 120             | nsec |                                 |  |  |  |

| Address Stable Prior to WR                                                                | taw ②                           | <b>⑤</b> |       |                 | nsec |                                 |  |  |  |

| Output Data Stable Prior to WR                                                            | tow ②                           | <b>©</b> |       |                 | nsec |                                 |  |  |  |

| Output Data Stable From WR                                                                | two ②                           | 0        |       |                 | nsec | C <sub>L</sub> = 100 pF: Addres |  |  |  |

| Address Stable from WR                                                                    | twa ②                           | 0        |       |                 | nsec | Data                            |  |  |  |

| HLDA to Float Delay                                                                       | the ②                           | 8        |       |                 | nsec | · C <sub>L</sub> = 50 pF: WR,   |  |  |  |

| WR to Float Delay                                                                         | twr ②                           | <u></u>  |       |                 | nsec | HLDA, DBIN                      |  |  |  |

| Address Hold Time after DBIN during HLDA                                                  | ¹AH ②                           | -20      |       |                 | nsec |                                 |  |  |  |

Notes Continued: ⑤

| Device      | †AW                      |

|-------------|--------------------------|

| μPD8080AF   | 2 tCY - tD3 - tro2 - 140 |

| μPD8080AF-2 | 2 tCY - tD3 - tro2 - 130 |

| μPD8080AF-1 | 2 tCY - tD3 - tro2 - 110 |

| 6 | Device      | <sup>t</sup> DW                                               |

|---|-------------|---------------------------------------------------------------|

|   | μPD8080AF   | t <sub>CY</sub> - t <sub>D3</sub> - t <sub>r\phi2</sub> - 170 |

|   | μPD8080AF-2 | $t_{CY} - t_{D3} - t_{r\phi 2} - 170$                         |

|   | µPD8080AF-1 | tCY - tD3 - tro2 - 150                                        |

- (9) If not HLDA,  $t_{WD} = t_{WA} = t_{D3} + t_{r\phi2} + 10$  ns, If HLDA,  $t_{WD} = t_{WA} = t_{WF}$ . (8)  $t_{HF} = t_{D3} + t_{r\phi2} 50$  ns. (9)  $t_{WF} = t_{D3} + t_{r\phi2} 10$  ns.

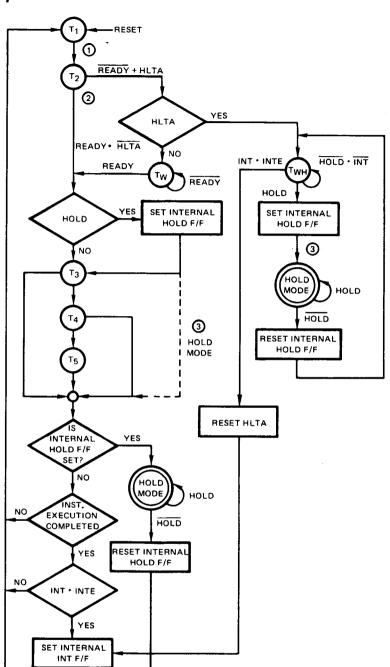

PROCESSOR STATE TRANSITION DIAGRAM

Notes:

INTE F/F is reset if internal INT F/F is set.

Internal INT F/F is reset if INTE F/F is reset.

If required, T<sub>4</sub> and T<sub>5</sub> are completed simultaneously with entering hold state.

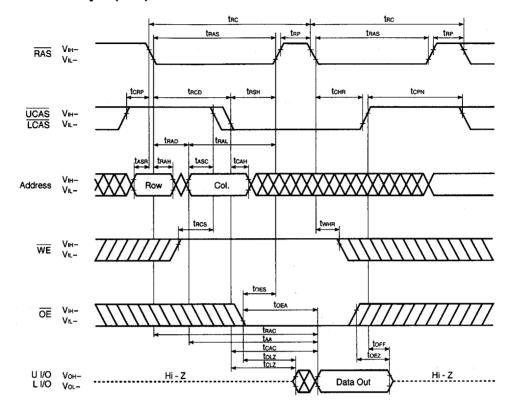

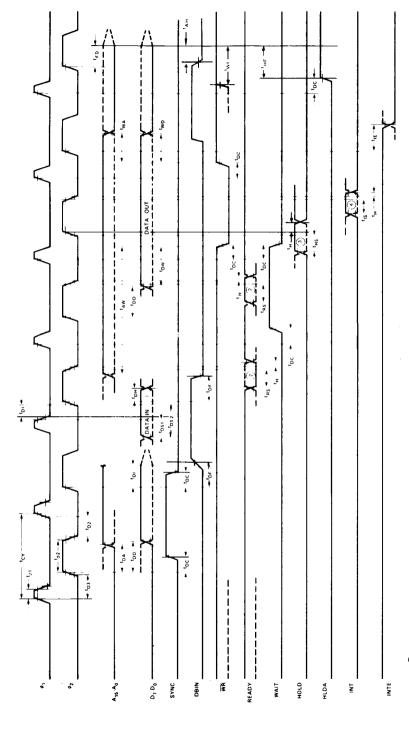

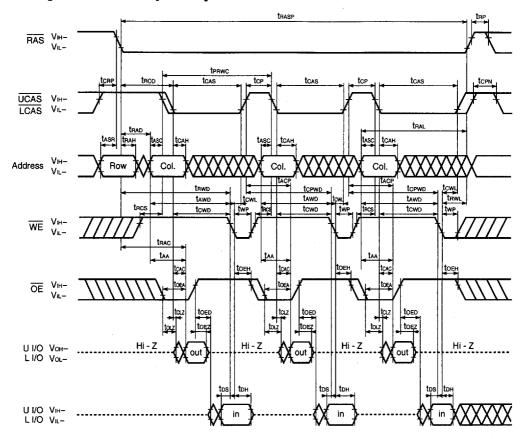

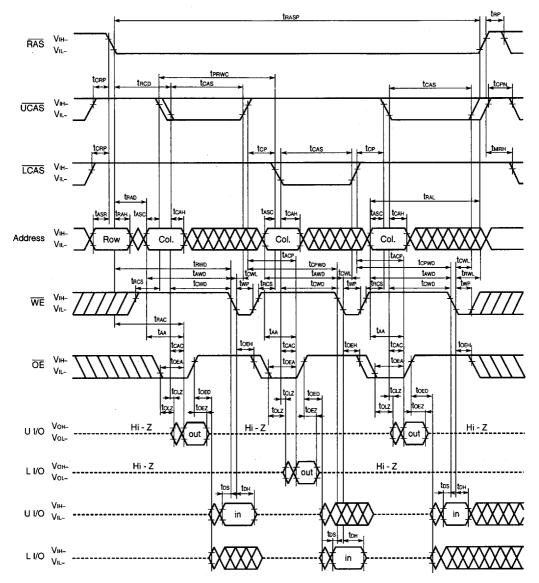

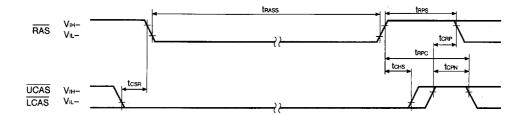

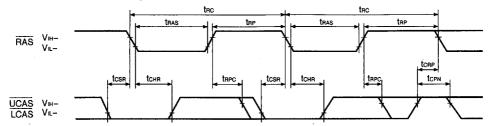

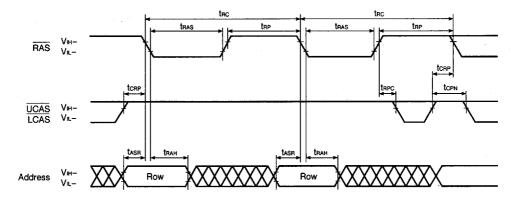

Notes: ① Data in must be stable for this period during DBIN • 13. Both tps1 and tps2 must be satisfied.

Ready signal must be stable for this period during T2 or Tw. (Must be externally synchronized.)

Hold signal must be stable for this period during T2 or TW when entering hold mode, and during T3, T4, T5 and TWH when in hold mode. 00

Interrupt signal must be stable during this period of the last clock cycle of any instruction in order to be recognized in the following instruction. (External synchronization is not required.) **a**

This timing diagram shows timing relationships only; it does not represent any specific machine cycle. (External synchronization is not required.) @ @

Timing measurements are made at the following reference voltages: CLOCK "1" = 8.0V, "0" = 1,0V; INPUTS "1" = 3,3V; "0" = 0,8V; OUTPUTS "1" = 2,0V, "0" = 0,8V.

The instruction set includes arithmetic and logical operators with direct, register, indirect, and immediate addressing modes.

Move, load, and store instruction groups provide the ability to move either 8 or 16 bits of data between memory, the six working registers and the accumulator using direct, register, indirect, and immediate addressing modes.

The ability to branch to different portions of the program is provided with direct, conditional, or computed jumps. Also the ability to call and return from subroutines is provided both conditionally and unconditionally. The RESTART (or single byte call instruction) is useful for interrupt vector operation.

Conditional jumps, calls and returns execute based on the state of the four testable flags (Sign, Zero, Parity and Carry). The state of each flag is determined by the result of the last instruction executed that affected flags. (See Instruction Set Table.)

The Sign flag is set (High) if bit 7 of the result is a "1"; otherwise it is reset (Low). The Zero flag is set if the result is "0"; otherwise it is reset. The Parity flag is set if the modulo 2 sum of the bits of the result is "0" (Even Parity); otherwise (Odd Parity) it is reset. The Carry flag is set if the last instruction resulted in a carry or a borrow out of the most significant bit (bit 7) of the result; otherwise it is reset.

In addition to the four testable flags, the  $\mu$ PD8080AF has another flag (ACY) that is not directly testable. It is used for multiple precision arithmetic operations with the DAA instruction. The Auxiliary Carry flag is set if the last instruction resulted in a carry or a borrow from bit 3 into bit 4; otherwise it is reset.

Double precision operators such as stack manipulation and double add instructions extend both the arithmetic and interrupt handling capability of the  $\mu PD8080AF$ . The ability to increment and decrement memory, the six general registers and the accumulator are provided as well as extended increment and decrement instructions to operate on the register pairs and stack pointer. Further capability is provided by the ability to rotate the accumulator left or right through or around the carry bit.

Input and output may be accomplished using memory addresses as I/O ports or the directly addressed I/O provided for in the #PD8080AF instruction set.

The special instruction group completes the µPD8080AF instruction set: NOP, HALT stop processor execution; DAA provides decimal arithmetic capability; STC sets the carry flag; CMC complements it; CMA complements the contents of the accumulator; and XCHG exchanges the contents of two 16-bit register pairs directly.

Data in the  $\mu$ PD8080AF is stored as 8-bit binary integers. All data/instruction transfers to the system data bus are in the following format:

D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub>

MSB DATA WORD LSB

Instructions are one, two, or three bytes long. Multiple byte instructions must be stored in successive locations of program memory. The address of the first byte is used as the address of the instruction.

One Byte Instructions

D7 D6 D5 D4 D3 D2 D1 D0 OP CODE

Two Byte Instructions

D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> OP CODE

D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> OPERAND

Three Byte Instructions

D7

D6

D5

D4

D3

D2

D1

D0

C

D7

D6

D5

D4

D3

D2

D1

D0

L

D7

D6

D5

D4

D3

D2

D1

D0

L

OP CODE Jump, call or direct load and store instructions

TYPICAL INSTRUCTIONS

Register to register, memory reference, arithmetic or logical rotate, return, push, pop, enable

or disable interrupt instructions

Immediate mode or I/O instruc-

LOW ADDRESS OR OPERAND 1

HIGH ADDRESS OR OPERAND 2

INSTRUCTION SET

DATA AND INSTRUCTION FORMATS

|                                                                                         |                                                                                                                                      |                                       |     | _                            |                            |                  |                       |          |                |                                      |      |             |          |       |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                     |                                |                |                       |                        |                        | ľ              |                              | 90   | UU      | <b>~</b> : |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|------------------------------|----------------------------|------------------|-----------------------|----------|----------------|--------------------------------------|------|-------------|----------|-------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|--------------------------------|----------------|-----------------------|------------------------|------------------------|----------------|------------------------------|------|---------|------------|

| MNEMONIC <sup>1</sup>                                                                   | DESCRIPTION                                                                                                                          | D <sub>7</sub>                        |     |                              |                            |                  | COD<br>D <sub>2</sub> |          | D <sub>O</sub> | Clock<br>Cycles 3                    | NDIS | FLA<br>SEBO | PARITY & | CARRY | MNEMONIC <sup>1</sup>                                                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Dy     |                     |                                |                |                       |                        | DE <sup>2</sup>        | 1 D            | Clock<br>Cycles <sup>3</sup> | SIGN | 2680 PT | PARITY S   |

|                                                                                         |                                                                                                                                      |                                       | М   | OVE                          |                            |                  |                       |          |                |                                      |      |             |          |       |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LOAG   | RE                  | GIST                           | ΓEΑ            | PAIF                  |                        |                        |                |                              |      |         |            |

| MQV 6 s<br>MQV M,s                                                                      | Move register to register<br>Move register to memory                                                                                 | 0                                     | 1   | d<br>1                       | đ                          | đ                | 5                     | 5        | 5              | 5                                    |      |             |          |       | LX+B <sub>(</sub> D16                                                       | Louid immediate register<br>pair BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0      | 0                   | 0                              | 0              | 0                     | c                      |                        | ,              | 10                           |      |         |            |

| MOV d,M                                                                                 | Move memory to register                                                                                                              | 0                                     | 1   | ď                            | d                          | đ                | 1                     | 1        | 0              | 7                                    |      |             |          |       | LXI D,D16                                                                   | Load immediate register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                     |                                |                |                       |                        |                        |                |                              |      |         |            |

| MVId,D8<br>MVIM,D8                                                                      | Move immediate to register<br>Move immediate to memory                                                                               |                                       | 0   | 1                            | d<br>1                     | б<br>Ө           | 1                     | 1        | 0              | 7<br>10                              |      |             |          |       | LXI H,D16                                                                   | pair DE<br>Load immediate register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0      | 0                   | 0                              | 1              | 0                     |                        |                        |                | 10                           |      |         |            |

|                                                                                         |                                                                                                                                      | NCREM                                 | ENT | /DE                          | CRE                        | MEN              | т                     |          |                |                                      |      |             |          |       | LXI SP,D16                                                                  | pair HL<br>Load immediate Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0      | 0                   | 1                              | 0              | 0                     | C                      | 0                      | 1              | 10                           |      |         |            |

| INR d                                                                                   | Increment register                                                                                                                   | 0                                     | 0   | d                            | d                          | ø                | ١                     | 0        | 0              | 5                                    | •    | •           | •        |       |                                                                             | Painter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0      | 0                   | 1                              | 1              | 0                     | 0                      | . 0                    | 1              | 10                           |      |         |            |

| OCR d<br>INR M                                                                          | Decrement register<br>Increment memory                                                                                               |                                       | 0   | d<br>1                       | d<br>1                     | d                | 1                     | 0        | 0              | 5<br>10                              | :    | :           | :        |       |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                     | PUSE                           | <u> </u>       |                       |                        |                        |                |                              |      |         |            |

| DCR M                                                                                   | Decrement memory                                                                                                                     | 0                                     | 0   | ,                            | 1                          | 0                | 1                     | 0        | 1              | 10                                   | •    | •           | •        |       | PU\$H B                                                                     | Push register pair BC<br>on stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1      | 1                   | 0                              | n              | 0                     | 1                      | 0                      | 1              | 11                           |      |         |            |