# UM82C284-10/-12

Clock Generator and Ready Interface

### Features

- Generates system clock for 80286 processors

- Uses crystal or TTL signal for frequency source

- Provides local READY and Multibus\* READY synchronization

- 18-pin package

- Single +5V power supply

- Generates system reset output from schmitt trigger input

### **General Description**

UM82C284 is a clock generator/driver which provides clock signals for 80286 processors and support components. It also contains logic to supply READY to the CPU from

either asynchronous or synchronous sources and synchronous RESET from an asynchronous input with hysteresis, It is fabricated with Si-Gate CMOS process.

7-200

- 19<sup>19</sup> - 1

# Absolute Maximum Ratings\*

| Temperature Under Bias                    |

|-------------------------------------------|

| Storage Temperature                       |

| All Output and Supply Voltages0.5V to +7V |

| All Input Voltages1.0V to +5.5V           |

| Power Dissipation                         |

### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

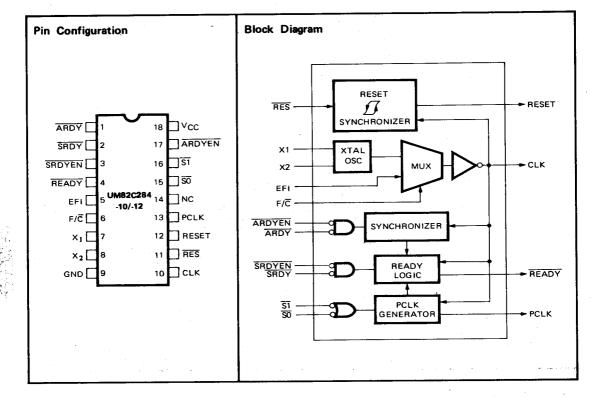

# Pin Description

| Symbol          | Туре | Name and Function                                                                                                                                                                                                                                                                                                                 |

|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK             | 0    | System Clock is the signal used by the processor and support devices which must be synchro-<br>nous with the processor. The frequency of the CLK output has twice the desired internal pro-<br>cessor clock frequency. CLK can drive both TTL and MOS level inputs.                                                               |

| F/C             | 1    | Frequency/Crystal Select is a strapping option to select the source for the CLK output. When $F/C$ is strapped LOW, the internal crystal oscillator drives CLK. When $F/C$ is strapped HIGH, the EFI input drives the CLK output.                                                                                                 |

| X1, X2          | 1    | Crystal In are the pins to which a parallel resonant fundamental mode crystal is attached for the internal oscillator. When $F/\overline{C}$ is LOW, the internal oscillator will drive the CLK output at the crystal frequency. The crystal frequency must be twice the desired internal processor clock frequency.              |

| EFI             | 1    | External Frequency In drives CLK when the $F/\overline{C}$ input is strapped HIGH. The EFI input frequency must be twice the desired internal processor clock frequency.                                                                                                                                                          |

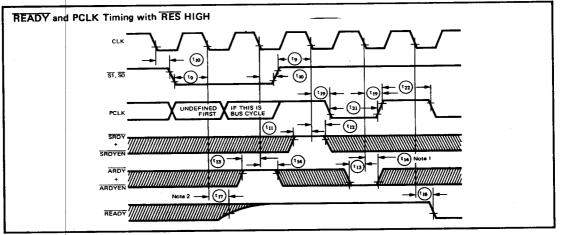

| PCLK            | 0    | Peripheral Clock is an output which provides a 50% duty cycle clock with 1/2 the frequency of CLK. PLCK will be in phase with the internal processor clock following the first bus cycle after the processor has been reset.                                                                                                      |

| ARDYEN          | 1    | Asynchronous Ready Enable is an active LOW input which qualifies the ARDY input. ARDYEN selects ARDY as the source of ready for the current bus cycle. Inputs to ARDYEN may be applied asynchronously to CLK. Setup and hold times are given to assure a guaranteed response to synchronous inputs.                               |

| ARDY            | 1    | Asynchronous Ready is an active LOW input used to terminate the current bus cycle. The ARDY input is qualified by ARDYEN. Inputs to ARDY may be applied asynchronously to CLK. Setup and hold times are given to assure a guaranteed response to synchronous inputs.                                                              |

| SRDYEN          |      | Synchronous Ready Enable is an active LOW input which qualifies SRDY. SRDYEN selects SRDY as the source for READY to the CPU for the current bus cycle. Setup and hold times must be satisfied for proper operation.                                                                                                              |

| SRDY            |      | Synchronous Ready is an active LOW input used to terminate the current bus cycle. The SRDY input is qualified by the SRDYEN input. Setup and hold times must be satisfied for proper operation.                                                                                                                                   |

| READY           | 0    | Ready is an active LOW output which signals that the current bus cycle is to be completed. The SRDY, SRDYEN, ARDY, ARDYEN, S1, S0 and RES inputs which control READY are explained later in the READY generator section. READY is an open collector output requiring an external 300 ohm pullup resistor.                         |

| <u>50, 51</u>   | 1    | Status inputs prepare the UM82C284 for a subsequent bus cycle. So and S1 synchronize PCLK to the internal processor clock and control READY. These inputs have pullup resistors to keep them HIGH if nothing is driving them. Setup and hold times must be satisfied for proper operation.                                        |

| RESET           | 0    | Reset is an active HIGH output which is derived from the RES input. RESET is used to force the system into an initial state. When RESET is active, READY will be active (LOW).                                                                                                                                                    |

| RES             | 1    | Reset In is an active LOW input which generates the system reset signal, RESET. Signals to RES may be applied asynchronously to CLK. A Schmitt trigger input is provided on RES, so that an RC circuit can be used to provide a time delay. Setup and hold times are given to assure a guaranteed response to synchronous inputs. |

| V <sub>DD</sub> |      | System Power: +5V power supply.                                                                                                                                                                                                                                                                                                   |

| V <sub>SS</sub> | 1    | System Ground: 0 volts.                                                                                                                                                                                                                                                                                                           |

# 7-201

### **Functional Description**

#### Introduction

The UM82C284 generates the clock, ready, and reset signals required for 80286 processors and support components. The UM82C284 is packaged in an 18-pin DIP and contains a crystal controlled oscillator, MOS clock generator, peripheral clock generator, Multibus ready synchronization logic and system reset generation logic.

### **Clock Generator**

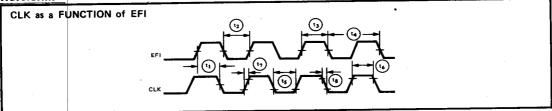

The CLK output provides the basic timing control for an 80286 system. CLK has output characteristics sufficient to drive MOS devices. CLK is generated by either an internal crystal oscillator or an external source as selected by the  $F/\overline{C}$  strapping option. When  $F/\overline{C}$  is LOW, the crystal oscillator drives the CLK output. When  $F/\overline{C}$  is HIGH, the EFI input drives the CLK output.

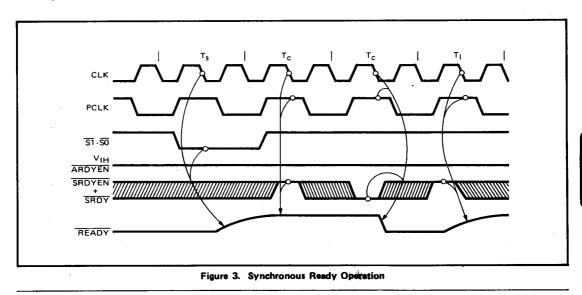

The UM82C284 provides a second clock output (PCLK) for peripheral devices. PCLK is CLK divided by two. PCLK has a duty cycle of 50% and TTL-output drive characteristics. PCLK is normally synchronized to the internal processor clock.

After reset, the PCLK signal may be out of phase with the internal processor clock. The  $\overline{S1}$  and  $\overline{S0}$  signals of the first bus cycle are used to synchronize PCLK to the internal processor clock. The phase of the PCLK output changes by extending its HIGH time beyond one system clock (see waveforms). PCLK is forced HIGH whenever either  $\overline{S0}$  or  $\overline{S1}$  were active (LOW) for the two previous CLK cycles. PCLK continues to oscillate when both  $\overline{S0}$  and  $\overline{S1}$  are HIGH.

Since the phase of the internal processor clock will not change, except during reset, the phase of PCLK will not change, except during the first bus cycle after reset.

#### Oscillator

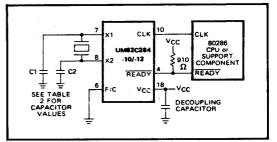

The oscillator circuit of the UM82C284 is a linear Pierce oscillator which requires an external parallel resonant, fundamental mode, crystal. The output of the oscillator is internally buffered. The crystal frequency chosen should be twice the required internal processor clock frequency. The crystal should have a typical load capacitance of 32 pF

X1 and X2 are the oscillator crystal connections. For stable operation of the oscillator, two loading capacitors are recommended, as shown in Table 2. The sum of the board capacitance and loading capacitance should equal the values shown. It is advisable to limit stray board capacitances (not including the effect of the loading capacitors or crystal capacitance) to less than 10 pF between the X1 and X2 pins. Decouple  $V_{DD}$  and  $V_{SS}$  as close

to the UM82C284 as possible.

Figure 1. Recommended Crystal and READY Connections

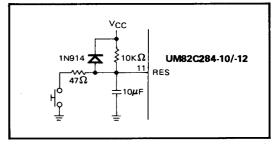

### **Reset Operation**

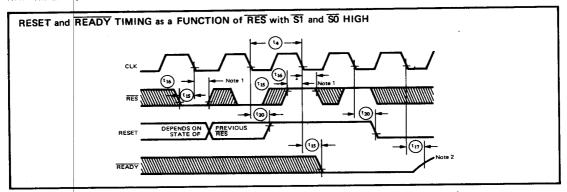

The reset logic provides the RESET output to force the system into a known, initial state. When the  $\overline{\text{RES}}$  input is active (LOW), the RESET output becomes active (HIGH).  $\overline{\text{RES}}$  is synchronized internally at the falling edge of CLK before generating the RESET output (see waveforms). Synchronization of the RES input introduces a one or two CLK delay before affecting the RESET output.

At power up, a system does not have a stable  $V_{DD}$  and CLK. To prevent spurious activity, RES should be asserted until  $V_{CC}$  and CLK stabilize at their operating values. 80286 processors and support components also require their RESET Inputs to be HIGH a minimum of 16 CLK cycles. An RC network, as shown in Figure 4, will keep RES LOW long enough to satisfy both needs.

Figure 2. Typical RC RES Timing Circuit

A Schmitt trigger input with hysteresis on  $\overline{\text{RES}}$  assures a single transition of RESET with an RC circuit on  $\overline{\text{RES}}$ . The hysteresis separates the input voltage level at which the circuit output switches from HIGH to LOW from the input voltage level at which the circuit output switches from LOW to HIGH. The  $\overline{\text{RES}}$  HIGH to LOW input transition voltage is lower than the  $\overline{\text{RES}}$  LOW to HIGH input transition voltage. As long as the slope of the  $\overline{\text{RES}}$

7-202

# UM82C284-10/-12

input voltage remains in the same direction (increasing or decreasing) around the  $\overline{\text{RES}}$  input transition voltage, the RESET output will make a single transition.

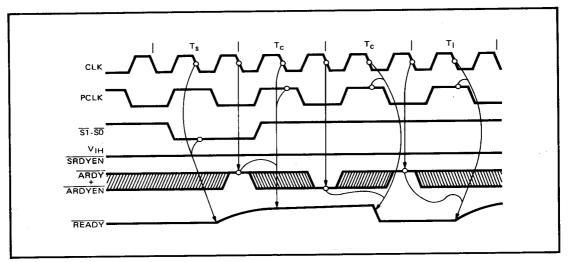

### **Ready Operation**

The UM82C284 accepts two ready sources for the system ready signal which terminates the current bus cycle. Either a synchronous (SRDY) or asynchronous ready (ARDY) source may be used. Each ready input has an enable (SRDYEN and ARDYEN) for selecting the type of ready source required to terminate the current bus cycle. An address decoder would normally select one of the enable inputs.

**READY** is enabled (LOW), if either **SRDY** + **SRDYEN** = "0" or  $\overline{\text{ARDY}} + \overline{\text{ARDYEN}} =$  "0" when sampled by the UM82C284 READY generation logic. **READY** will remain active for at least two CLK cycles.

The READY output has an open-collector driver allowing other ready circuits to be wire or'ed with it, as shown in Figure 3. The READY signal of an 80286 system requires an external 910 ohm  $\pm$  5% pull-up resistor. To

force the READY signal inactive (HIGH) at the start of a bus cycle, the READY output floats when either  $\overline{S1}$ or  $\overline{S0}$  are sampled LOW at the falling edge of CLK. Two system clock periods are allowed for the pull-up resistor to pull the READY signal to V<sub>eH</sub>. When RESET is active, READY is forced active one CLK later (see waveforms).

Figure 5 illustrates the operation of SRDY and SRDYEN. These inputs are sampled on the falling edge of CLK when S1 and S0 are inactive and PCLK is HIGH. READY is forced active when both SRDY and SRDYEN are sampled as LOW.

Figure 6 shows the operation of  $\overline{ARDY}$  and  $\overline{ARDYEN}$ . These inputs are sampled by an internal synchronizer at each falling edge of CLK. The output of the synchronizer is then sampled when PCLK is HIGH. If the synchronizer finds both the  $\overline{ARDY}$  and  $\overline{ARDYEN}$  have been resolved as active, the  $\overline{SRDY}$  and  $\overline{SRDYEN}$  inputs are ignored. Either  $\overline{ARDY}$  or  $\overline{ARDYEN}$  must be HIGH at the end of T<sub>s</sub> (see figure 6).

READY remains active until either  $\overline{S1}$  or  $\overline{S0}$  are sampled LOW, or the ready inputs are sampled as inactive.

### Table 2. UM82C284 Crystal Loading Capacitance Values

| Crystal Frequency | C1 Capacitance<br>(pin 7) | C2 Capacitance<br>(pin 8) |

|-------------------|---------------------------|---------------------------|

| 1 to 8 MHz        | 60 pF                     | 40 pF                     |

| 8 to 25 MHz       | 25 pF                     | 15 pF                     |

Note: Capacitance values must include stray board capacitance.

7-203

$s \ge r s_{1,2}$

Figure 4. Asynchronous Ready Operation

# **D.C. Characteristics**

$(T_A = 0^{\circ}C \text{ to } 70^{\circ}C, V_{DD} = 5V, \pm 10\%)$

|                  |                                 |             | AHz         | 12.5 MHz |       |      |                                    |

|------------------|---------------------------------|-------------|-------------|----------|-------|------|------------------------------------|

| Symbol           | Parameter                       | —10<br>Min. | —10<br>Max. | Min.     | Max.  | Unit | Test Condition                     |

| VIL              | Input LOW Voltage               |             | 0.8         |          | 0.8   | V    |                                    |

| VIH              | Input HIGH Voltage              | 2.0         |             | 2.0      |       | V    |                                    |

| V <sub>IHR</sub> | RES and EFI Input HIGH Voltage  | 2.6         |             | 2.6      |       | V    | ·                                  |

| V <sub>HYS</sub> | RES Input Hysteresis            | 0.25        |             | 0.25     |       | V    |                                    |

| VOL              | RESET, PCLK Output LOW Voltage  |             | 0.45        |          | 0.45  | v    | I <sub>OL</sub> = 5 mA             |

| V <sub>он</sub>  | RESET, PCLK Output HIGH Voltage | 2.4         |             | 2.4      |       | V    | l <sub>OH</sub> = −1 mA            |

| V <sub>OLR</sub> | READY, Output LOW Voltage       |             | 0.45        |          | 0.45  | v    | I <sub>OL</sub> = 9 mA             |

| V <sub>OLC</sub> | CLK Output LOW Voltage          |             | 0.45        |          | 0.45  | V    | I <sub>OL</sub> = 5 mA             |

| v <sub>онс</sub> | CLK Output HIGH Voltage         | 4.0         |             | 4.0      |       | V    | $I_{OH} = -800 \mu A$              |

| lcc              | Power Supply Current            |             | 75.0        |          | 75.0  | mA   | at 25 MHz Output<br>CLK Frequency  |

| 1,1              | Input Leakage Current           |             | ±10.0       |          | ±10.0 | μA   | 0≤V <sub>IN</sub> ≤V <sub>CC</sub> |

| CI               | Input Capacitance               |             | .10.0       |          | 10.0  | pF   | F <sub>c</sub> = 1 MHz             |

# 7-204

# A.C. Characteristics

# $(T_A = 0^{\circ}C \text{ to } 70^{\circ}C, V_{DD} = 5V, \pm 10\%)$

AC timings are referenced to 0.8V and 2.0V points of signals as illustrated in datasheet waveforms, unless otherwise noted.

|        | Parameter                                      | 10 MHz     |             | 12.5 MHz |      |      |                        |

|--------|------------------------------------------------|------------|-------------|----------|------|------|------------------------|

| Symbol |                                                | 10<br>Min. | —10<br>Max, | Min.     | Max. | Unit | Test Condition         |

| 1      | EFI to CLK Delay                               |            | 25          |          | 25   | ns   | at 1.5V Note 1         |

| 2      | EFI LOW Time                                   | 22.5       |             | 14       |      | ns   | at 0.8V Note 1         |

| 3      | EFI HIGH Time                                  | 22.5       |             | 22       |      | ns   | at 2.0V Note 1         |

| 4      | CLK Period                                     | 50         | 500         | 40       | 500  | ns   |                        |

| 5      | CLK LOW Time                                   | 12         |             | 11       |      | ns   | at 0.6V Note 1, Note 2 |

| 6      | CLK HIGH Time                                  | 16         |             | 13       |      | ns   | at 3.8V Note 1, Note 2 |

| 7      | CLK Rise Time                                  |            | 8           |          | 8    | ns   | 1.0V to 3.5V Note 1    |

| 8      | CLK Fall Time                                  |            | 8           |          | 8    | ns   | 3.5 V to 1.0V Note 1   |

|        | Status Setup Time for Status Going<br>Active   | 20         |             | 22       |      |      |                        |

| 9      | Status Setup Time for Status Going<br>Inactive | 20         |             | 20       |      | ns   | Note 1                 |

| 10     | Status Hold Time                               | 1          |             | 3        |      | ns   | Note 1                 |

| 11     | SRDY or SRDYEN Setup Time                      | 15         |             | 15       |      | ns   | Note 1                 |

| 12     | SRDY or SRDYEN Hold Time                       | 2          |             | 2        |      | ns   | Note 1                 |

| 13     | ARDY or ARDYEN Setup Time                      | 0          |             | 0        |      | ns   | Note 1, Note 3         |

| 14     | ARDY or ARDYEN Hold Time                       | 30         |             | 25       |      | ns   | Note 1, Note 3         |

| 15     | RES Setup Time                                 | 20         |             | 18       |      | ns   | Note 1, Note 3         |

| 16     | RES Hold Time                                  | 10         |             | 8        | i    | ns   | Note 1, Note 3         |

| 17     | READY Active Delay                             | 5          |             | 5        |      | ns   | at 0.8V Note 4         |

| .18    | READY Active Delay                             | 0          | 24          | 0        | -18  | ns   | at 0.8V Note 4         |

| 19     | PCLK Delay                                     | 0 ·        | 35          | 0        | 23   | ns   | Note 5                 |

| 20     | RESET Delay                                    | 5          | 27          | 3        | 22   | ns   | Note 5                 |

| 21     | PCLK LOW Time                                  | t4-20      |             | t4-20    |      | ns   | Note 5, Note 6         |

| 22     | PCLK HIGH Time                                 |            |             | t4-20    |      | ns   | Note 5, Note 6         |

Note 1: CLK Loading: CL = 100pF.

- Note 2: With the internal crystal oscillator using recommended crystal and capacitive loading, or with the EFI input meeting specifications t2, and t3. Use a parallel-resonant, fundamental mode crystal. The recommended crystal loading for CLK frequencies of 8-25 MHz are 25pF from pin X<sub>1</sub> to ground, and 15pF from pin X<sub>2</sub> to ground. These recommended values are  $\pm$ 5pF and include all stray capacitance. Decouple V<sub>DD</sub> and V<sub>SS</sub> as close to the UM82C284 as possible.

- Note 3: This is an asynchronous input. This specification is given for testing purposes only, to assure recognition at specific CLK edge.

Note 4: READY loading: I<sub>OL</sub> = 7 mA, C<sub>L</sub> = 150pF. In system application, use 910 ohm ±5% pullup resistor to meet 80286, 80286-6 and 80286-4 timing requirements.

Note 5: PCLK and RESET loading: C<sub>L</sub> = 75pF.

| Note b. (4 refers to any | anowable CER period. |

|--------------------------|----------------------|

|                          |                      |

| REAY loading: | CPU Frequency   | 10 MHz | 12.5 MHz |

|---------------|-----------------|--------|----------|

| -             | Resistor        | 700 Ω  | 600 Ω    |

|               | CL              | 150 pF | 150 pF   |

|               | <sup>I</sup> OL | 7 mA   | 9 mA     |

7---205

### Waveforms

Note: The EFI input LOW and HIGH times as shown are required to guarentee the CLK LOW and HIGH times shown.

Note 1: This is an asynchronous input. The setup and hold times shown are required to guarantee the response shown. Note 2: Tie 700 ohm  $\pm 5\%$  pullup resistor to the READY output.

Note 1: This is an asynchronous input. The setup and hold times shown are required to guarantee the response shown. Note 2: Tie 700 ohm  $\pm 5\%$  pullup resistor to the READY output.

### Ordering Information

| Product     | Frequency |

|-------------|-----------|

| UM82C284-10 | 10 MHZ    |

| UM82C284-12 | 12.5 MHz  |

### 7-206