### INTEGRATED CIRCUITS

### DATA SHEET

### **TDA3842**

Multistandard TV IF amplifier and demodulator with TV signal identification

Preliminary specification

File under Integrated Circuits, IC02

**April 1991**

**TDA3842**

#### **FEATURES**

- Low supply voltage range, from 5.0 V to 8.0 V

- Low power dissipation, 200 mW at 5 V

- High supply ripple rejection

- Wide IF bandwidth of 80 MHz

- Synchronous demodulator with low differential phase and gain

- Additional video buffer with a wide bandwidth of 10 MHz

- · Video off switch

- Peak sync AGC for negative modulation, e.g. B/G

- Peak white AGC for positive modulation, e.g. L

- Adjustable take-over point (TOP); positive AGC slope

- Switching to fast AGC dependent on TV identification

- · Alignment free AFC detector with integrated phase shift

- ESD protection

- TV signal identification

- Options: tracking of reference circuit, suitable for MAC-on-cable

### **GENERAL DESCRIPTION**

The TDA3842 is a bipolar integrated circuit for vision IF-signal processing in multistandard TV and VTRs, designed for a supply voltage range from 5.0 V to 8.0 V.

### **QUICK REFERENCE DATA**

| SYMBOL                 | PARAMETER                                                                 | CONDITIONS                 | MIN. | TYP. | MAX. | UNIT   |

|------------------------|---------------------------------------------------------------------------|----------------------------|------|------|------|--------|

| V <sub>P</sub>         | supply voltage range (pin 15)                                             |                            | 4.75 | 5.0  | 8.8  | V      |

| I <sub>P</sub>         | supply current (pin 15)                                                   | V <sub>P</sub> = 5.0 V     | _    | 42   | _    | mA     |

| V <sub>1-20(rms)</sub> | IF input signal for nominal video output voltage at pin 14 (RMS value)    | f = 38.9 MHz               | _    | 70   | _    | μV     |

|                        | minimum IF input signal for TV signal identification at pin 6 (RMS value) | maximum G <sub>v</sub>     | _    | 20   | 40   | μV     |

| Vo                     | video output signal (pin 12)                                              | buffered                   | _    | 2.0  | _    | V      |

| G <sub>v</sub>         | IF voltage gain control range                                             |                            | _    | 66   | _    | dB     |

| S/N                    | signal-to-noise ratio                                                     | $V_{1-20} = 10 \text{ mV}$ | 55   | 60   | _    | dB     |

| V <sub>8</sub>         | AFC output voltage swing                                                  |                            | _    | 4.0  | _    | V      |

| S <sub>AFC</sub>       | AFC steepness (pin 8)                                                     |                            | _    | 2    | _    | μΑ/kHz |

| RR                     | supply voltage ripple rejection (pin 12)                                  |                            | 30   | 35   | _    | dB     |

### ORDERING INFORMATION

| EXTENDED    | PACKAGE |              |          |                       |  |  |  |  |

|-------------|---------|--------------|----------|-----------------------|--|--|--|--|

| TYPE NUMBER | PINS    | PIN POSITION | MATERIAL | CODE                  |  |  |  |  |

| TDA3842     | 20      | DIL          | plastic  | SOT146 <sup>(1)</sup> |  |  |  |  |

| TDA3842T    | 20      | mini-pack    | plastic  | SO20L; SOT163A (2)    |  |  |  |  |

#### Notes

SOT146-1; 1997 January 08.

SOT163-1; 1997 January 08

TDA3842

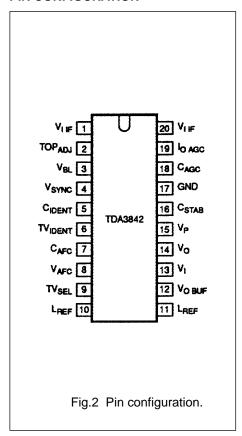

### **PIN CONFIGURATION**

### **PINNING**

| SYMBOL              | PIN | DESCRIPTION                                  |

|---------------------|-----|----------------------------------------------|

| VIIF                | 1   | IF input (balanced)                          |

| TOP <sub>ADJ</sub>  | 2   | tuner AGC take-over point adjustment         |

| V <sub>BL</sub>     | 3   | black level voltage                          |

| V <sub>SYNC</sub>   | 4   | sync pulse amplitude voltage                 |

| C <sub>IDENT</sub>  | 5   | identification capacitor                     |

| TV <sub>IDENT</sub> | 6   | video identification output                  |

| C <sub>AFC</sub>    | 7   | AFC capacitor                                |

| V <sub>AFC</sub>    | 8   | AFC output signal                            |

| TV <sub>SEL</sub>   | 9   | video standard selection switch              |

| L <sub>REF</sub>    | 10  | LC reference tuned circuit                   |

| L <sub>REF</sub>    | 11  | LC reference tuned circuit                   |

| V <sub>O BUF</sub>  | 12  | buffered video output signal                 |

| VI                  | 13  | video input signal for buffer                |

| v <sub>O</sub>      | 14  | video output signal with intercarrier signal |

| V <sub>P</sub>      | 15  | supply voltage                               |

| C <sub>STAB</sub>   | 16  | supply voltage stabilization                 |

| GND                 | 17  | ground                                       |

| C <sub>AGC</sub>    | 18  | AGC capacitor                                |

| I <sub>O AGC</sub>  | 19  | tuner AGC output signal                      |

| VIIF                | 20  | IF input (balanced)                          |

### Multistandard TV IF amplifier and demodulator with TV signal identification

TDA3842

#### **FUNCTIONAL DESCRIPTION**

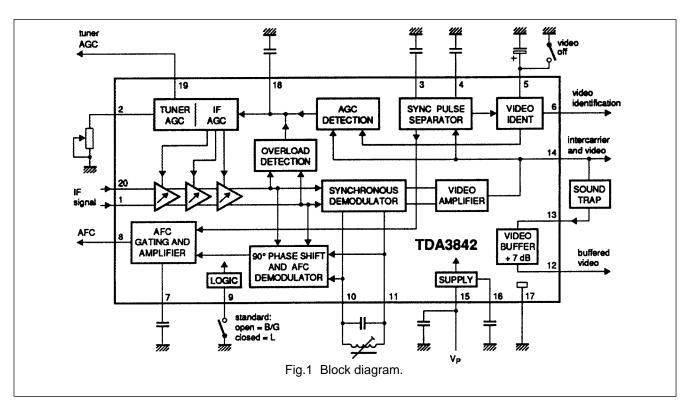

The complete circuit consists of the following functional blocks as shown in Fig.1:

- 3-stage gain controlled IF amplifier

- 2. Overload detector

- 3. Reference amplifier

- 4. Carrier signal reference limiter

- 5. Video demodulator

- 6. Video amplifier

- 7. Video buffer amplifier

- 8. AGC detector

- IF and tuner AGC (with adjustable TOP)

- 10. Sync pulse separator

- 11. Video identification

- 90° phase shift and AFC demodulator

- AFC gating, AFC amplifier and AFC switch

- 14. Voltage stabilizer

- 15. Standard switch

### 1. 3-stage gain controlled IF amplifier (pins 1 and 20)

The vision IF amplifier consists of three AC-coupled differential amplifier stages. Gain control is achieved by current divider stages. The emitter feedback resistors are optimized for low noise and signal handling capability.

#### 2. Overload detector

The overload detector is fed from the output of the third IF amplifier. As soon as the IF voltage exceeds the overload threshold in the detector, its output current reduces the IF amplification by discharging the AGC capacitor.

### 3. Reference amplifier

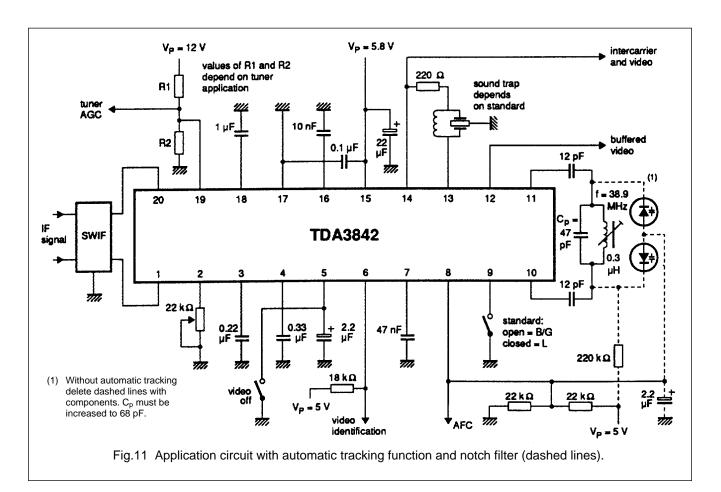

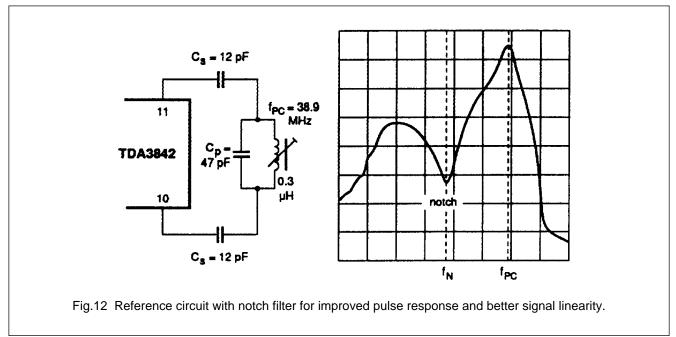

For passive video carrier regeneration an integrated differential amplifier with resistive load allows

capacitive coupling of the resonant circuit for notch and tracking functions.

### 4. Carrier signal reference limiter

A limiter stage after the reference amplifier eliminates amplitude modulation. Its output is fed to the video demodulator.

### 5. Video demodulator

The video demodulator receives both the limited reference carrier signal and the IF signal. The video signal polarity is switched according to the TV standard selected. The video signal can also be switched off.

### 6. Video amplifier

The video amplifier is an operational amplifier with internal feedback and wide bandwidth. The DC level is shifted according to the TV standard to provide the same sync level for positive and negative IF modulation.

### 7. Video buffer amplifier

The video buffer amplifier is an operational amplifier with internal feedback, wide bandwidth and frequency compensation; gain and input impedance are adapted to operate with a ceramic sound trap. The load for the sound trap is an integrated resistive divider.

#### 8. AGC detector

With negative modulation (B/G) a peak sync AGC detector generates a fast current pulse to discharge the AGC capacitor (gain reduction). This minimizes the video signal distortion. Positive modulation (L) uses a peak white AGC detector.

To filter out the sound carrier the video signal is fed through low pass filters. After the low pass filters the video signal with attenuated sound carrier, is fed to the AGC detector.

The charging current of the AGC capacitor is optimized for minimum distortion of the video signal. With positive modulation the charging current is very low and consequently the AGC time constant is large. When the video identification circuit does not detect a video signal, the charging current is increased.

#### 9. IF and tuner AGC

The voltage on the AGC capacitor is used to control the gain of the three IF amplifier stages and to supply the tuner AGC current (open-collector). The tuner AGC TOP potentiometer at pin 2 adjusts the IF signal level from the tuner. To stabilize the IF output voltage of the tuner, IF slip (= variation of IF gain over the total tuner range) is kept at a minimum.

### 10. Sync pulse separator

The sync pulse separator supplies two internally-used pulses using the bandwidth limited video signal. These are the composite sync for the AFC detector and the vertical sync for the video identification output. The bandwidth is limited to reduce the noise and increase the ident sensitivity.

### 11. Video identification

An analog integrator monitors the duty cycle of the vertical sync pulses to identify the video signal. The integrator output is fed to a window comparator which has an open collector output stage to provide the video ident signal. The complete circuit operates in combination with the sync separator and is optimized for high sensitivity.

### 12. 90° phase shift and AFC demodulator

The AFC demodulator needs a 90° phase-shifted carrier. The output of the carrier signal reference limiter is

### Multistandard TV IF amplifier and demodulator with TV signal identification

TDA3842

fed to an active 90° phase-shift circuit. The 90° (lead) phase-shifted carrier and the IF signal are fed to the AFC demodulator. The demodulated signal is fed to the AFC gating stage.

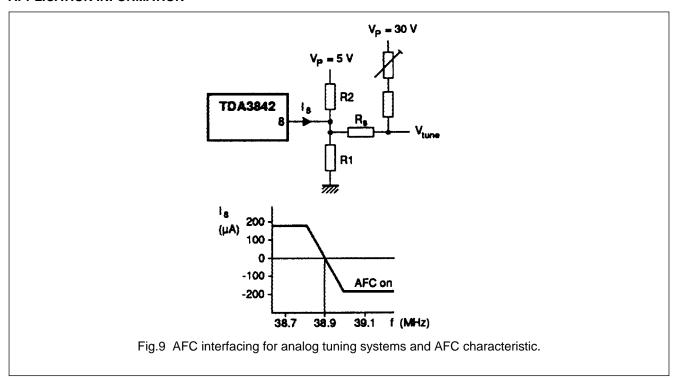

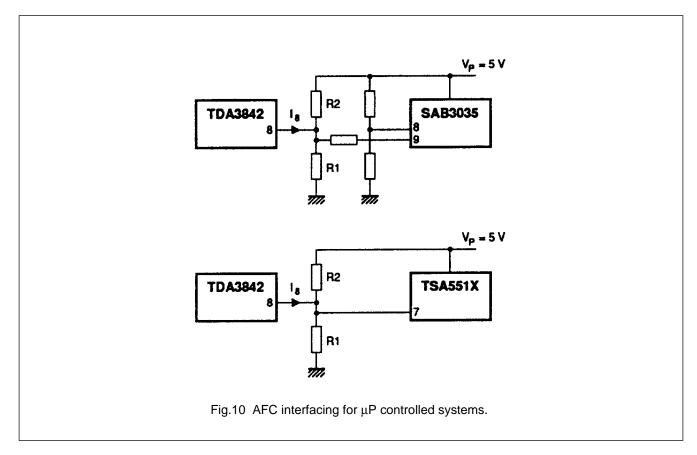

### 13. AFC gating, AFC amplifier and AFC switch

With negative modulated video IF signals the output of the AFC detector is gated by composite sync pulses to prevent video modulation on the AFC

output. The gated signal is integrated by an AFC capacitor. The AFC amplifier converts the capacitor voltage to an AFC current (open collector sink/source output). At positive modulation the AFC operates continuously.

AFC function can be externally switched off for test purposes. For high-performance signal handling the AFC signal can be used to track the resonant circuit as shown in Fig.11.

### 14. Voltage stabilizer

An integrated bandgap voltage stabilizer generates an internal supply voltage of 4 V. A decoupling capacitor reduces noise and supply voltage ripple.

#### 15. Standard switch

The operating mode of the AGC detector and video IF demodulator for positive and negative IF modulation is selected by the logic level on pin 9.

TDA3842

### **LIMITING VALUES**

In accordance with the Absolute Maximum System (IEC 134)

| SYMBOL           | PARAMET                        | ΓER                             | MIN. | MAX. | UNIT |

|------------------|--------------------------------|---------------------------------|------|------|------|

| v <sub>p</sub>   | supply voltage at pin 15:      | SOT146                          | _    | 8.8  | V    |

|                  |                                | SOT163A                         | _    | 6.0  | V    |

| V <sub>19</sub>  | tuner AGC voltage              |                                 | _    | 13.2 | V    |

| V <sub>8</sub>   | permissible voltage at AFC out | ible voltage at AFC output      |      |      | V    |

| I <sub>15</sub>  | supply current                 |                                 | _    | 55   | mA   |

| T <sub>stg</sub> | storage temperature range      | rage temperature range          |      |      | °C   |

| T <sub>amb</sub> | operating ambient temperature  | ating ambient temperature range |      |      | °C   |

| V <sub>ESD</sub> | ESD sensitivity                | sensitivity                     |      |      | V    |

### **CHARACTERISTICS**

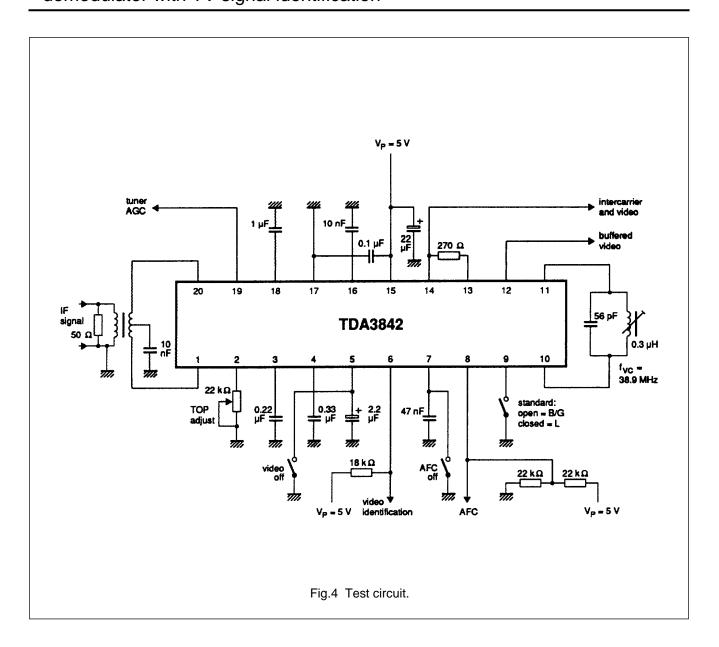

$V_P$  = 5 V and  $T_{amb}$  = 25 °C;  $f_{VC}$  = 38.9 MHz; all voltages are measured to GND (pin 17); measured in test circuit of Fig.4.; unless otherwise specified.

| SYMBOL                 | PARAMETER                          | CONDITIONS                      | MIN. | TYP. | MAX. | UNIT |

|------------------------|------------------------------------|---------------------------------|------|------|------|------|

| V <sub>P</sub>         | supply voltage range (pin 15)      | DIL-package                     | 4.75 | 5.0  | 8.8  | V    |

|                        |                                    | SO-package                      | 4.75 | 5.0  | 6.0  | V    |

| I <sub>P</sub>         | supply current (pin 15)            | V <sub>P</sub> = 5.0 V          | _    | 42   | _    | mA   |

| RR                     | ripple rejection (pin 12)          |                                 | 30   | 35   | _    | dB   |

| IF amplifier           |                                    |                                 |      | •    |      |      |

| В                      | bandwidth                          | -3 dB                           | _    | 80   | _    | MHz  |

| R <sub>I</sub>         | input resistance (pins 1 and 20)   |                                 | _    | 2    | _    | kΩ   |

| Cı                     | input capacitance (pins 1 and 20)  |                                 | _    | 1.5  | _    | pF   |

| V <sub>1-20(rms)</sub> | IF input signal (RMS value)        | video output -1 dB              | _    | 70   | _    | μV   |

|                        | maximum IF input signal            | minimum G <sub>v</sub> ; note 1 | 100  | Ī-   | _    | mV   |

| G <sub>v</sub>         | gain control range                 |                                 | 63   | 66   | _    | dB   |

| IF AGC: ne             | gative modulation                  | •                               |      | •    |      | •    |

| I <sub>18</sub>        | leakage current AGC capacitor      |                                 | _    | _    | 1    | μΑ   |

|                        | charging current AGC capacitor     | with video identification       | _    | 13   | _    | μΑ   |

|                        | charging current AGC capacitor     | without video identification    | _    | 35   | _    | μΑ   |

| I <sub>18M</sub>       | discharging peak current capacitor |                                 | _    | 2    | _    | mA   |

| t <sub>1</sub>         | response time of IF input signal   | 50 dB increasing step           | _    | 1    | _    | ms   |

|                        | change                             | 50 dB decreasing step           | _    | 150  | _    | ms   |

| IF AGC: sta            | indard L (note 2)                  |                                 |      |      | •    |      |

| I <sub>18</sub>        | leakage current AGC capacitor      |                                 | _    | _    | 20   | nA   |

|                        | charging current AGC capacitor     | with video identification       | _    | 280  | _    | nA   |

|                        |                                    | without video identification    | _    | 22   | _    | μΑ   |

| I <sub>18M</sub>       | discharging peak current capacitor |                                 | _    | 2    | _    | mA   |

| t <sub>2</sub>         | response time of IF input signal   | 50 dB increasing step           | _    | 1    | _    | ms   |

|                        | change                             | 50 dB decreasing step           | _    | 300  | _    | ms   |

TDA3842

| SYMBOL                 | PARAMETER                                                                          | CONDITIONS                        | MIN.     | TYP. | MAX.  | UNIT |

|------------------------|------------------------------------------------------------------------------------|-----------------------------------|----------|------|-------|------|

| Tuner AGC              | (note 3)                                                                           |                                   | <u>'</u> | •    | •     | •    |

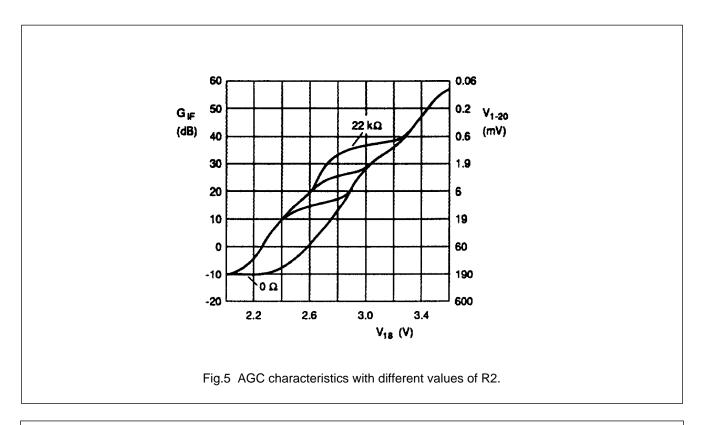

| V <sub>1-20(rms)</sub> | lower IF input signal for starting point of tuner take-over; see Fig.5 (RMS value) | R2 = 22 kΩ                        | _        | _    | 1     | mV   |

|                        | upper IF input signal for starting point of tuner take-over; see Fig.5 (RMS value) | R2 = 0 Ω                          | 50       | _    | -     | mV   |

|                        | TOP variation                                                                      | 60 K temperature range            | _        | 2    | 3     | dB   |

| I <sub>19</sub>        | tuner AGC output current                                                           | $V_{19} = 0.5 \text{ V}$          | 1        | 2    | _     | mA   |

| Sync demo              | odulator and video amplifier (note 4)                                              |                                   |          |      |       |      |

| V <sub>14</sub>        | composite video output signal                                                      |                                   | 0.9      | 1.0  | 1.1   | V    |

|                        | sync level voltage                                                                 | standard B/G                      | _        | 1.5  | _     | V    |

|                        | zero carrier level voltage                                                         | negative modulation               | _        | 2.6  | _     | V    |

|                        |                                                                                    | positive modulation               | _        | 1.47 | _     | V    |

| I <sub>14</sub>        | output current                                                                     | DC and AC                         | _        | _    | ± 1.0 | mA   |

| R <sub>14</sub>        | output resistance                                                                  |                                   | _        | 75   | _     | Ω    |

| В                      | video bandwidth at -1 dB (pin 14)                                                  | C <sub>load</sub> ≤ 20 pF         | 7        | 8    | _     | MHz  |

| V <sub>14</sub>        | upper video clipping level                                                         |                                   | _        | 3.6  | _     | V    |

|                        | lower video clipping level                                                         |                                   | _        | 0.3  | _     | V    |

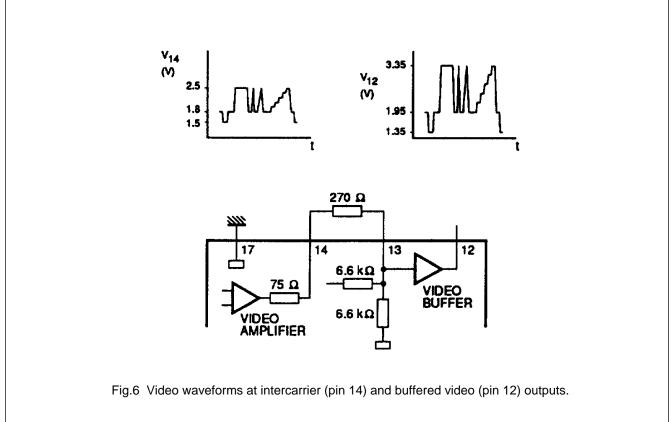

| Buffered vi            | ideo output signal (see Fig.6)                                                     |                                   |          |      |       |      |

| G                      | gain of video buffer                                                               |                                   | 6.5      | 7.0  | _     | dB   |

| V <sub>12</sub>        | sync level clamping voltage                                                        |                                   | _        | 1.35 | _     | V    |

|                        | upper video clipping level                                                         |                                   | _        | 4.25 | _     | V    |

|                        | lower video clipping level                                                         |                                   | _        | 0.3  | _     | V    |

| I <sub>12</sub>        | output current                                                                     | DC and AC                         | _        | _    | ± 1.0 | mA   |

| R <sub>12</sub>        | output resistance                                                                  |                                   | _        | _    | 10    | Ω    |

| В                      | video bandwidth at -1 dB (pin 12)                                                  | C <sub>load</sub> ≤ 20 pF         | _        | 10   | _     | MHz  |

| $R_I$                  | input resistance (pin 13)                                                          |                                   | _        | 3.3  | _     | kΩ   |

| C <sub>I</sub>         | input capacitance (pin 13)                                                         |                                   | _        | 2    | _     | pF   |

| Overall vid            | eo performance (see Fig.6)                                                         |                                   |          |      |       |      |

| Vo                     | video output signal (pin 12)                                                       | negative modulation               | _        | 2    | _     | V    |

|                        |                                                                                    | positive modulation;<br>note 4    | _        | 2    | _     | V    |

| В                      | video bandwidth at -2 dB (pin 12)                                                  | C <sub>load</sub> ≤ 20 F          | 7        | 8    | _     | MHz  |

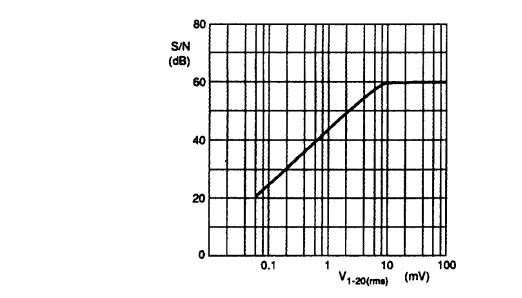

| S/N                    | signal to noise ratio (see Fig.7)                                                  | V <sub>1-20</sub> = 10 mV; note 5 | 55       | 60   | _     | dB   |

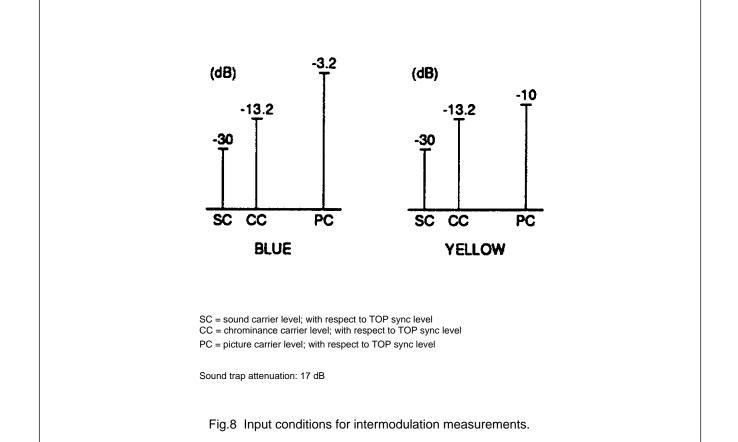

| $\alpha_1$             | intermodulation for blue (note 6)                                                  | f = 1.1 MHz                       | 56       | 58   | _     | dB   |

|                        |                                                                                    | f = 3.3 MHz                       | 62       | -    | _     | dB   |

| $\alpha_2$             | intermodulation for yellow (note 6)                                                | f = 1.1 MHz                       | 53       | 56   | _     | dB   |

|                        |                                                                                    | f = 3.3 MHz                       | 60       | _    | _     | dB   |

| α <sub>3</sub>         | signal harmonic suppression                                                        |                                   | _        | 26   | _     | dB   |

# Multistandard TV IF amplifier and demodulator with TV signal identification

TDA3842

| SYMBOL                                | PARAMETER                                                           | CONDITIONS                                                              | MIN. | TYP. | MAX.           | UNIT               |

|---------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|----------------|--------------------|

| V <sub>5</sub>                        | video switch off voltage                                            | note 7                                                                  | _    | -    | 1              | V                  |

| $\alpha_4$                            | attenuation of video signal (pin 14)                                | video signal switched off                                               | 50   | 60   | _              | dB                 |

| ΔG                                    | differential gain                                                   | EBU test line 330                                                       | _    | 2    | _              | %                  |

| ΔΦ                                    | differential phase                                                  | EBU test line 330                                                       | _    | 2    | _              | deg                |

| ΔV/V                                  | variation of video output signal (pin 14)                           | gain control 50 dB;<br>$V_{1-20(rms)} = 0.3 \text{ to } 100 \text{ mV}$ | -    | _    | 0.5            | dB                 |

| V <sub>res1</sub>                     | residual vision carrier (pin 12)                                    |                                                                         | _    | 1    | _              | mV                 |

| V <sub>res2</sub>                     | residual second harmonic of the vision carrier (pin 12)             |                                                                         | -    | 1    | _              | mV                 |

| Video ident                           | ification                                                           |                                                                         | •    |      |                |                    |

| V <sub>1-20(rms)</sub>                | minimum IF input signal for TV identification at pin 14 (RMS value) | maximum G <sub>v</sub>                                                  | _    | 20   | 40             | μV                 |

| V <sub>6</sub>                        | video identification voltage<br>(signal unidentified)               | $V_{1-20(rms)} = < 40 \ \mu V$<br>$I_6 = 0.5 \ mA$                      | -    | _    | 0.4            | V                  |

|                                       | video identification voltage (signal identified)                    | $V_{1-20(rms)} = \ge 40 \mu V$<br>$I_6 = -1 \mu A$                      | 4.5  | _    | _              | V                  |

| T <sub>sync</sub> /T <sub>field</sub> | vertical pulse duty cycle                                           |                                                                         | 4.5  | 8    | 16             | × 10 <sup>-3</sup> |

| C/N                                   | carrier-to-noise ratio (pin 1 and pin 20)                           | note 8                                                                  | -    | 8    | _              | dB                 |

| l <sub>5</sub>                        | allowed leakage current                                             |                                                                         | _    | _    | 3              | μΑ                 |

| α <sub>5</sub>                        | sync pulse suppression for correct TV signal identification         |                                                                         | -    | _    | 70             | %                  |

| t <sub>d</sub>                        | delay time of mute output signal                                    |                                                                         | _    | 100  | 150            | ms                 |

| AFC (see F                            | ig.9 and Fig.10); note 9                                            |                                                                         | •    | •    | •              | •                  |

| I <sub>8</sub>                        | AFC source current output                                           |                                                                         | 0.16 | 0.19 | 0.22           | mA                 |

|                                       | AFC sink current output                                             |                                                                         | 0.16 | 0.19 | 0.22           | mA                 |

| V <sub>8</sub>                        | upper output voltage                                                |                                                                         | 4.3  | _    | 4.7            | V                  |

|                                       | lower output voltage                                                |                                                                         | 0.3  | _    | 0.7            | V                  |

| S                                     | control steepness                                                   | Q <sub>B</sub> = 40;<br>V <sub>1-20(rms)</sub> = 10 mV                  | _    | 2    | _              | μA/kHz             |

| l <sub>7</sub>                        | leakage current at AFC gating                                       |                                                                         | _    | _    | ± 1            | μΑ                 |

| Standard s                            | witch                                                               |                                                                         |      |      |                |                    |

| V <sub>9</sub>                        | voltage for negative modulation                                     | standard switch open                                                    | 2.5  | n.c. | V <sub>P</sub> | V                  |

|                                       | voltage for positive modulation (L)                                 | standard switch closed                                                  | 0    | _    | 0.8            | V                  |

### Multistandard TV IF amplifier and demodulator with TV signal identification

TDA3842

#### Notes to the characteristics

- 1. The video signal is still gain-controlled,  $V_{14(p-p)} = 1 \text{ V}$ , but intermodulation figures are degraded.

- 2. In multi-standard applications the capacitor at pin 18 must be a low-leakage (foil) type.

- 3. The starting point of tuner AGC can be adjusted by the resistor at pin 2. Fig.5 shows the AGC characteristic.

- 4. IF input signals are RMS values measured at TOP sync (standard B/G) and with a vision carrier of 38.9 MHz (see Fig.4). The IF input signal is fed from 50  $\Omega$  via a 1:1 transformer, DSB, to pins 1 and 20. With a 10 mV<sub>RMS</sub> IF input signal, the residual vision carrier is: = 10% for white (standard B/G), = 3% for sync (standard L).

- 5. In the test circuit of Fig.4, measured and weighted according to CCIR Recommendation 567:

$$S/N = \frac{V_{14 \text{ (black to white)}}}{V_{14 \text{ noise}} \text{ (RMS, black)}}$$

6. Intermodulation figures are defined as follows:  $\alpha_1 = 20 \times log \frac{V_o}{V_o} \text{ at 4.4 MHz} + 3.6 \text{ dB}$

and

$$\alpha_2 = 20 \times log \frac{V_o \text{ at } 4.4 \text{ MHz}}{V_o \text{ at } 3.3 \text{ MHz}}$$

- 7. When  $V_5 < 1$  V (short-circuited identification capacitor at pin 5) the video output signal at pin 14 is switched off.  $V_{14}$  shifts to "zero carrier level" ("ultra white" (2.6V) for negative modulation or "top sync" (1.5 V) for positive modulation). During normal operation the capacitor at pin 5 should not be loaded ( $I_5 \le 3 \mu A$ ).

- 8. The C/N at the IF input (pins 1 and 20) for TV identification is defined as the RMS sync level of the vision IF signal input, relative to the RMS value of a superimposed white noise signal, with a bandwidth limited to 5 MHz.

- 9. The values for the AFC measurements depend on the  $Q_B$  of the reference circuit at pins 10 and 11. The internal phase shift is matched to a vision carrier of 38.9 MHz. The AFC function can be switched off for test purposes when pin 7 is connected to ground ( $V_7 = 0 \text{ V}$ ).

9

April 1991

TDA3842

TDA3842

## Multistandard TV IF amplifier and demodulator with TV signal identification

TDA3842

Fig.7 Signal-to-noise ratio as a function of IF input voltage (RMS value) at pins 1 and 20.

TDA3842

### **APPLICATION INFORMATION**

TDA3842

### Multistandard TV IF amplifier and demodulator with TV signal identification

TDA3842

### Note to Fig.12

Recommended for reception of data signals e.g. in Teletext and D2-MAC. Values in combination with SAW filter OFW G 1956 (Siemens). Curve shows combined frequency response of SAW filter and reference circuit.

For different standards  $C_s$  and  $C_p$  are calculated as follows:  $C_s = 2 C_p \left\{ \frac{f_P C^2}{f_N^2} - 1 \right\}$

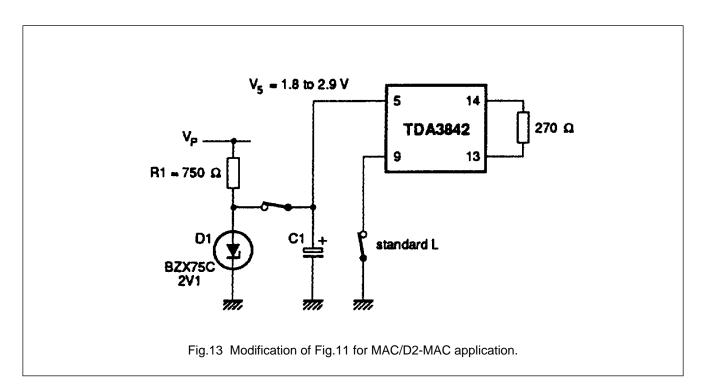

### Note to Fig.13

When the TDA3842 is used in a MAC/D2-MAC receiver the voltage at pin 5 must be stabilized between 1.8 and 2.9 V by zener diode D1 and resistor R1. Standard switch at pin 9 must be in position 'standard L' to activate the peak-related slow AGC mode.

TDA3842

### **PACKAGE OUTLINES**

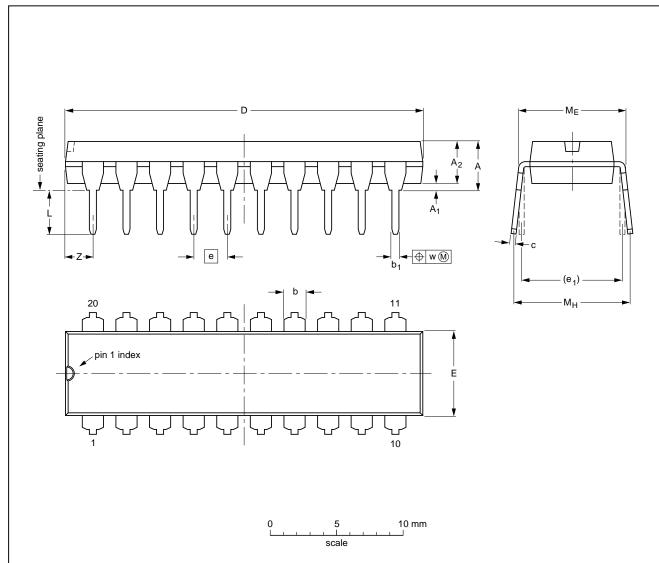

DIP20: plastic dual in-line package; 20 leads (300 mil)

SOT146-1

### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | M <sub>E</sub> | Мн           | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|--------------|-------|--------------------------|

| mm     | 4.2       | 0.51                   | 3.2                    | 1.73<br>1.30   | 0.53<br>0.38   | 0.36<br>0.23   | 26.92<br>26.54   | 6.40<br>6.22     | 2.54 | 7.62           | 3.60<br>3.05 | 8.25<br>7.80   | 10.0<br>8.3  | 0.254 | 2.0                      |

| inches | 0.17      | 0.020                  | 0.13                   | 0.068<br>0.051 | 0.021<br>0.015 | 0.014<br>0.009 | 1.060<br>1.045   | 0.25<br>0.24     | 0.10 | 0.30           | 0.14<br>0.12 | 0.32<br>0.31   | 0.39<br>0.33 | 0.01  | 0.078                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER | EUROPEAN | ISSUE DATE |            |                                 |

|----------|-----|-------|----------|------------|------------|---------------------------------|

| VERSION  | IEC | JEDEC | EIAJ     |            | PROJECTION | 1330E DATE                      |

| SOT146-1 |     |       | SC603    |            |            | <del>92-11-17</del><br>95-05-24 |

TDA3842

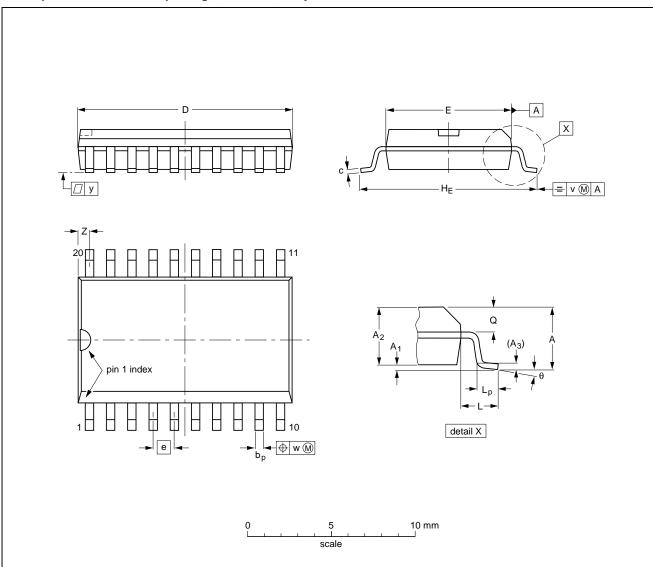

### SO20: plastic small outline package; 20 leads; body width 7.5 mm

SOT163-1

### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | Α3   | bp             | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE             | L     | Lp             | Q              | v    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|------|----------------|----------------|------------------|------------------|-------|----------------|-------|----------------|----------------|------|------|-------|------------------|----|

| mm     | 2.65      | 0.30<br>0.10   | 2.45<br>2.25   | 0.25 | 0.49<br>0.36   | 0.32<br>0.23   | 13.0<br>12.6     | 7.6<br>7.4       | 1.27  | 10.65<br>10.00 | 1.4   | 1.1<br>0.4     | 1.1<br>1.0     | 0.25 | 0.25 | 0.1   | 0.9<br>0.4       | 8° |

| inches | 0.10      | 0.012<br>0.004 | 0.096<br>0.089 | 0.01 | 0.019<br>0.014 | 0.013<br>0.009 | 0.51<br>0.49     | 0.30<br>0.29     | 0.050 | 0.42<br>0.39   | 0.055 | 0.043<br>0.016 | 0.043<br>0.039 | 0.01 | 0.01 | 0.004 | 0.035<br>0.016   | 0° |

#### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  |        | REFER    | EUROPEAN | ISSUE DATE |                                  |

|----------|--------|----------|----------|------------|----------------------------------|

| VERSION  | IEC    | JEDEC    | EIAJ     | PROJECTION | ISSUE DATE                       |

| SOT163-1 | 075E04 | MS-013AC |          |            | <del>-92-11-17</del><br>95-01-24 |

### Multistandard TV IF amplifier and demodulator with TV signal identification

TDA3842

#### **SOLDERING**

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

### Soldering by dipping or by wave

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature (T<sub>stg max</sub>). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

### Repairing soldered joints

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

### **DEFINITIONS**

| Data sheet status         |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification     | This data sheet contains final product specifications.                                |

| Limiting values           |                                                                                       |

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.