8,192 WORD×9 BIT CMOS STATIC RAM

# TC5589P/J-20, TC5589P/J-25, TC5589P/J-35

#### DESCRIPTION

The TC5589P/J is a 65,536 bit high speed static random access memory organized as 8,192 words by 9bits

## DESCRIPTION

The TC5589P/J is a 65,536 bit high speed static random access memory organized as 8,192 words by 9bits using CMOS technology, and operated from a single 5-volt supply. Toshiba's high performance device technology provides both high speed and low power features with a maximum access time of 20ns/25ns/35ns and maximum operating current of 120mA at maximum cycle time. The TC5589P/J also features an automatic

stand-by mode. The TC5589P/J is suitable for use ir cache memory and high speed storage, where high speed/high density are required. The TC5589P/J is moulded in a 28 pin standard plastic DIP and a 28 pin plastic SOJ, with 0.3 inch width for high density assembly. The TC5589P/J is fabricated with ion implanted CMOS silicon gate MOS technology for high performance and high reliability.

### **FEATURES**

• Fast access time:

TC5589P/J-20 20ns (MAX.) TC5589P/J-25 25ns (MAX.) TC5589P/J-35 35ns (MAX.)

Power dissipation: Operation 120mA (MAX.)

Stand by 20mA (MAX.)

5V single power supply

• Full static operation

• Directly TTL compatible: All input and output

Package: 28 pin plastic 300 mil DIP (TC5589P)

28 pin plastic 300 mil SOJ (TC5589J)

## PIN CONNECTION

| A8 d 1                 | √ 28 v <sub>DD</sub> | A8 - 1    | 28 b v <sub>DD</sub> |

|------------------------|----------------------|-----------|----------------------|

| A7 1 2                 | 27 DWE               | A7 L 2    | 27 DWE               |

| A6 D 3                 | 26 D CE2             | A6 E 3    | 26 D CE2             |

|                        | . 25 DA9             | A5 🖸 4    | 25 A9                |

|                        |                      | A4 E 5    | 24 DA10              |

| A4 5                   | 24 DA10              | A3 C 6    | 23 DA11              |

| A3 G 6                 | 23 DA11<br>22 DOE    | A2 E 7    | 22 D OE              |

| A2 G 7<br>A1 G 8       |                      | Al E 8    | 21 PA12              |

|                        | 21 PA12              | A0 C 9    | 20 FCE1              |

|                        | 20 CE1               | I/01 C 10 | 19 1/09              |

|                        | 19 1/09              | 1/02 5 11 | 18 1 08              |

| 1/02 911               | 18 71/08             | L/03 C 12 | 17 51/07             |

| 1/03   12<br>1/04   13 | 17 1/07              | 1/04 513  | 1651/06              |

| GND CLA                | 16 PI/06<br>15 PI/05 | GND C 14  | 15 1 1 05            |

| GMD -114               | 15/1/05              | J 1       |                      |

| (DIP)                  |                      | (SOJ)     |                      |

#### PIN NAMES

| A0 ~ A13    | Address Inputs      |  |

|-------------|---------------------|--|

| 1/01 ~ 1/04 | Data Input/Output   |  |

| CE1, CE2    | Chip Enable Input   |  |

| WE          | Write Enable Input  |  |

| OE          | Output Enable Input |  |

| $V_{DD}$    | Power (+5V)         |  |

| GND         | Ground              |  |

|             |                     |  |

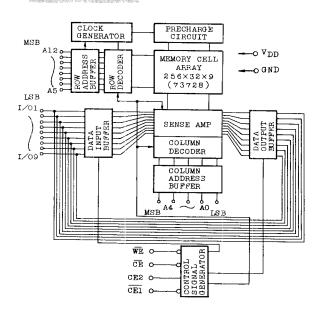

## **BLOCK DIAGRAM**