# SIEMENS

# ASIC Product Description SH100E

ECL/CML Gate Array Family

#### **FEATURES**

- Gate complexities from 1,500 to 16,000 gates

- 120 ps gate delay, 90 ps differential

- 1.5 GHz D flip-flop, 1.7 GHz differential

- Both ECL and CML macro families

- TTL I/O available

- ECL 10KH/100K compatible

- Up to 256 signal pins available

- 3 levels of series gating

- PGA, LCC and LLCC packaging

- Daisy, Mentor, and Valid workstation support

- CML and ECL is speed/power programmable

#### PRODUCT DESCRIPTION

Siemens utilizes a third generation bipolar ECL process to produce a family of high speed, high density ECL/CML gate arrays. The family of gate arrays ranges in density from 1,500 gates for the smallest member and up to 16,000 for the largest member. These gate arrays operate with a cut-off frequency (f<sub>T</sub>) of 7 GHz and obtain their high density and design flexibility by allowing the design engineer to mix ECL and CML macros on the same chip. This feature allows the designer to utilize maximum speed ECL technology for critical paths and CML elsewhere for power conservation. In addition, ECL 10KH/100K or TTL on the smaller family members allow the designer added flexibility. Power management also is easier using the wide range of speed/ power programming options with this gate array family. Siemens allows you not only to program the current sources. but also the emitter followers independently, thus allowing optimal speed/power combinations.

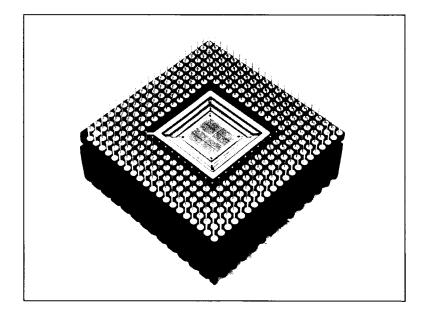

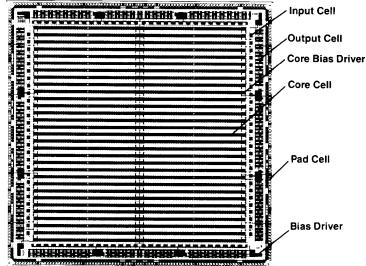

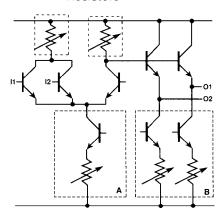

Figure 1. Array Architecture

Array Architecture

The row based architecture shown in Figure 1 above for the 10K/16K gate array is characteristic of all SH100E array masters. The array cores of each master are designed with rows of cells separated by routing channels allowing 25 tracks or metal lines each. The bias drivers are located at the ends of each row and also in the center of the rows in the larger arrays.

### **Product Family Members**

Table 1 shows the relative gate counts, core cell counts, and I/O counts of all four SH100E family members. The maximum ECL complexity which can be accommodated is indicated by the gate count for each master.

Since CML type macros do not require the output emitter followers, they are smaller in cell area than their ECL counterparts. Thus, a larger number of CML macros can be placed on a given master array. For example, if CML macros are used in entirety, the SH100E7 gate counts will be about 16,000.

Table 1. Key Architecture Data for SH100E Gate Array Family

| Option                 | SH100E4 | SH100E5 | SH100E6 | SH100E7 |

|------------------------|---------|---------|---------|---------|

| Complexity             | 1,500   | 2,500   | 5,000   | 10,000  |

| Number of Rows         | 12      | 16      | 22      | 31      |

| Cells/Row              | 32      | 40      | 54      | 84      |

| Core Cell Number       | 384     | 640     | 1,188   | 2,604   |

| ECL Gate Number        | 1,818   | 2,950   | 5,000   | 10,780  |

| CML Gate Number        | 2,727   | 4,425   | 7,500   | 16,170  |

| I/O Number             | 84      | 120     | 160     | 256     |

| Maximum TTL I/O Number | 84      | 120     | 160     | N/A     |

| Pad Count              | 132     | 172     | 224     | 360     |

| Power Pads             | 48      | 52      | 64      | 104     |

#### Core Cell

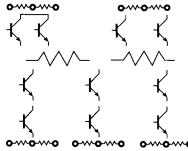

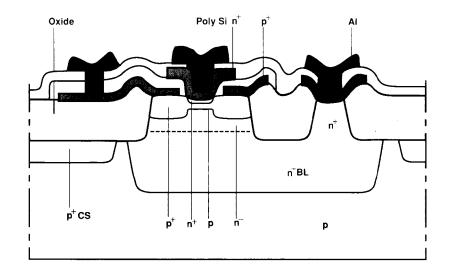

The internal core cell structure is shown in Figure 2. It contains 10 transistors, 6 current source resistors, 4 load resistors, 1 pinch resistor and 1 level shift resistor for a total device count of 22. Eight of the 10 transistors can be used universally as switching, level shifting, or current source transistors.

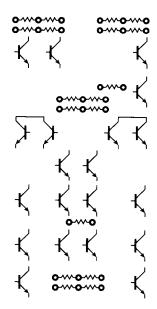

#### I/O Cells

The I/O cells shown in Figures 3 and 4 illustrate the transistor/resistor arrangements and counts necessary to construct input receivers, level shifters, and output transmitters. These cells also can be used to construct complex macros such as multiplexers which then can drive the output pads. This allows for a more efficient use of silicon area.

In the case of the SH100E7, there are 224 input cells and a maximum of 200 output cells.

Additional design flexibility is afforded the design engineer with the use of 10KH ECL or 100K ECL I/Os.

Also available are TTL I/Os where required on the E4, E5, and E6 family members. Inputs and outputs can be mixed at any I/O location without restriction.

In addition, ECL outputs are available with on chip series termination resistors programmable to 0, 20, or 40 ohms.

Figure 2. Core Cell

√ √ | ½ ½ | ½

Figure 3. Input Cell

Figure 4. Output Cell Logic Section

#### Transmitter Section

#### Speed/Power Programming

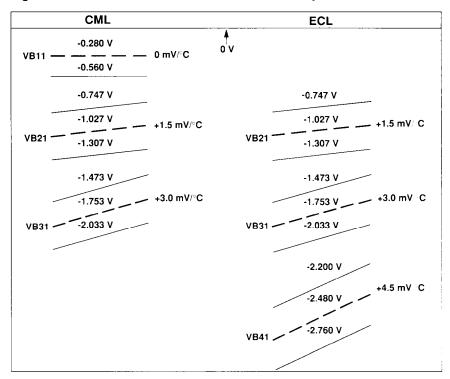

As suggested in Table 2, speed/power trade-off flexibility is provided through many options. With CML, 4 power levels are possible. With ECL, there are 3 intra-macro power levels and 6 independently adjustable emitter follower power levels. Three examples at middle speed/power and both extremes are shown in Table 2. The resistor network used to control the speed/power programming is suggested in Figure 5, with Table 3 describing the different current levels available at each point.

Figure 5. Speed-Power Programming Resistors

Mixing ECL and CML

A main innovation of the SH100E family lies in its capability of accepting both ECL and CML macros on the same chip. The resulting 4 bias voltages for 3 levels of series gating are shown in Figure 6.

Table 2. Speed/Power Programming Trade-Off for OR/NOR Gate Loaded with F.O. = 3, and 2 mm each of 1st and 2nd Metal as Lumped Capacitance

| Macro Circuit Type          | CML   |      | L   |     | ECL  |     |     |

|-----------------------------|-------|------|-----|-----|------|-----|-----|

| Speed/Power Program         | L     | S    | Н   | нн  | LL   | SS  | ннн |

| Macro Size (in core cells)  | 1 2   |      |     |     |      |     |     |

| Avg. Delay from I to O [ps] | 1,839 | 959  | 517 | 260 | 802  | 455 | 239 |

| Avg. Drive Factor [ps/pF]   | 1,390 | 685  | 330 | 165 | 550  | 260 | 80  |

| Total Current [mA]          | 0.275 | 0.55 | 1.1 | 2.2 | 0.55 | 1.1 | 3.3 |

**Table 3. Cascode Current Source Alternatives**

| Туре | Current Source                   | Low      | Medium   | High     |

|------|----------------------------------|----------|----------|----------|

| Α    | Cascode I <sub>SW</sub>          | 0.275 mA | 0.55 mA  | 1.1 mA   |

|      |                                  | 0.275 mA | 0.275 mA | 0.275 mA |

|      |                                  | 0.55 mA  | 0.55 mA  | 0.55 mA  |

| В    | Emitter Follower I <sub>SW</sub> |          | 1.1 mA   | 1.1 mA   |

|      |                                  |          |          | 1.375 mA |

|      |                                  |          |          | 1.65 mA  |

|      |                                  |          |          | 2.2 mA   |

CML = Type A only.

Figure 6. ECL/CML Bias Levels of the SH100E Family

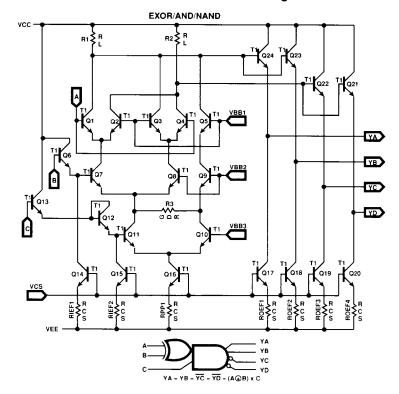

#### **Series Gating**

An EXOR/AND/NAND macro circuit diagram is shown in Figure 7 to illustrate the application of three levels of series gating. Up to three levels of series gating can be used in a 10KH or 100K I/O levels with VEE=-5.2 V, nominal. If VEE=-4.5 V, nominal, then only 2-levels of series gating can be used for operation over the full temperature range.

Figure 7. An Example of 3 Levels of Series Gating

#### **Macro Libraries**

To support both the ECL and CML circuits, Siemens offers two distinct macro libraries.

Presently there are over 200 ECL and CML macros in the library. This number will grow with time as customers desire different macro logic functions. The macros range in complexity from simple OR/AND functions to the more complex multiplexers, adders, and decoders. A listing of currently available macros is provided in Table 4.

Table 4. ECL and CML Macros

| Name     | Function                         |

|----------|----------------------------------|

| Single S | tage Gates                       |

| ELOR1    | Dual 2 Input OR                  |

| ELOR6    | 5 x 2 Input OR                   |

| ELOR2    | 2 Input OR (4 Outputs)           |

| ELOR3    | 4 Input OR Gate (Twin Outputs)   |

| ELOR4    | Dual 4 Input OR                  |

| ELOR5    | 12 Input OR                      |

| ELNR1    | Dual 2 Input NOR                 |

| ELNR5    | 2 Input NOR                      |

| ELNR2    | Dual 4 Input NOR                 |

| ELNR3    | 4 Input NOR (Twin Outputs)       |

| ELNR4    | 12 Input NOR                     |

| ELONR1   | 2 Input OR/NOR (Twin TRUE)       |

| ELONR2   | 2 Input OR/NOR (Twin Complement) |

| ELONR3   | 2 Input OR/NOR                   |

| ELONR15  | 2 Input OR plus 2 Input NOR      |

| ELONR12  | 2 Input OR/NOR 3 Input OR/NOR    |

| ELONR4   | 4 Input OR/NOR (Single Outputs)  |

| Name                                                                                                                                                                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single St                                                                                                                                                                     | age Gates (Cont.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ELONR5 ELONR13 ELONR14 ELONR6 ELONR7 ELONR8 ELONR10 ELONR10 ELONR11 ELNR01 ELAN1 ELAN2 ELAND1 ELND1 ELND1 ELND2 CLOR1 CLONR1 CLONR2 CLONR3 CLONR3 CLONR4 CLONR5 CLONR6 CLONR6 | 4 Input OR/NOR 4 Input OR plus 4 Input NOR 4 Input OR plus 4 Input OR 5 Input OR/NOR 8 Input OR/NOR 12 Input OR/NOR 12 Input OR/NOR 12 Input OR/NOR 12 Input NOR plus 2 Input OR 2 Input NOR plus 2 Input OR 2 Input NAND Gate (Single Output) Dual 2 Input AND 2 Input AND plus 2 Input AND 2 Input NAND plus 2 Input AND 2 Input NAND AND 2 Input NAND Gate (Single Output) Dual 2 Input NAND 2 Input NAND Gate (Single Output) Dual 2 Input NAND 2 Input NAND Gate (Single Output) Dual 2 Input NAND 1 Input OR/NOR 4 Input OR/NOR 1 Input OR/NOR 1 Input OR/NOR 1 Input OR/NOR W/Inhibit 1 Input OR/NOR W/Inhibit 1 Input OR/NOR W/Inhibit 1 Input OR/NOR W/Inhibit 8 Input OR/NOR |

| Output M                                                                                                                                                                      | lacros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| EOEONR1<br>EOEOR1<br>EOEOR2<br>EOEONR2<br>EOEONR3<br>EOEONR4<br>EOEONR5<br>EOEOA1<br>EOEAO1<br>EOEAO2<br>EOEOXR1<br>EOEMX1<br>EOEMX2                                          | 2 Input OR/NOR 2-2 OR Gate 2-2 OR Gate 2-5 ohm OR/NOR Driver 4 Input OR/NOR 5 Input OR/NOR 8 Input OR/NOR 2-2 OR/AND Dual AND/OR Dual AND/OR 2-2 OR/EXOR 2-1 MUX Dual 2:MUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Name                                                                                                                                                                                                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output M                                                                                                                                                                                                        | acros (Cont.)                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EOEMX3 EOEMX4 EOEBF1 EOTBF1 EOTBF2 EOLA1 EOLA2 EOFFD1 EOFFD2                                                                                                                                                    | 2:1 MUX w/Enable (Low) 4:1 MUX Differential Buffer TTL Output Converter (ECL to TTL) TTL Tristate Output Converter D Latch with Reset D Latch with Reset D Flip-Flop w/Reset D Flip-Flop w/Reset                                                                                                                                                                                                                                                                     |

| Two-Stag                                                                                                                                                                                                        | je Gates                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ELGA1 ELOA1 ELOA2 ELOA3 ELOA29 ELOA4 ELOA22 ELOA21 ELOA25 ELOA6 ELOA6 ELOA7 ELOA8 ELOA28 ELOA11 ELOA12 ELOA12 ELOA12 ELOA11 ELOA12 ELOA12 ELOA11 ELOA12 ELOA16 ELOA13 ELOA13 ELOA15 ELOA15 ELOA15 ELOA16 ELOA17 | 2-2 OR/AND. Gated 2-2 OR/AND 2-2-1-1 OR/AND 2-2-1-1 OR/AND 3-3 OR/AND 3-3-3 OR/AND 3-3-3 OR/AND 3-3-3 OR/AND 3-3-3 OR/AND 3-2-2-2 OR/AND 4-2-3-2-3 OR/AND 4-2-3-2-3 OR/AND 4-2-3-2-3 OR/AND 4-3-3-3 OR/AND 5-4-3-2-3-3 OR/AND 5-4-3-2-3-3 OR/AND 5-4-3-2-3-3 OR/AND 5-4-3-2-1 OR/AND 5-4-3-2-1 OR/AND 4-2-4-2-4-2-4-2 OR/AND 4-2-4-2-4-2-4-2 OR/AND 4-2-4-2-4-2-4-2 OR/AND |

Continued

| Name     | Function                  |

|----------|---------------------------|

| Two Stag | e Gates (Cont.)           |

| ELOA24   | 6-5-4-3-2-1 OR/AND        |

| ELOA30   | 2 Input OR, 2 Input AND   |

| ELAO1    | 3-3 AND/OR                |

| ELAO11   | 3-3 AND/OR                |

| ELAO2    | 2-3-4-4 AND / OR w/Enable |

| ELAO13   | 2-3-4-4 AND / OR w/Enable |

| ELAO6    | 3-2-2 AND / OR            |

| ELAO3    | 3-3-3 AND / OR            |

| ELAO10   | 3-3-3 AND / OR            |

| ELAO4    | 3-3-2-1 AND/OR            |

| ELA012   | 3-3-2-1 AND/OR            |

| ELAO5    | 3-3-3-3 AND / OR          |

| ELAO9    | 3-3-3-3 AND / OR          |

| ELA07    | 3-2-2-2-3 AND/OR          |

| ELA014   | 3-2-2-2-3 AND/OR          |

| ELAO15   | 4-3-3-3-2 AND/OR          |

| ELAO8    | 5-5-5-5 AND / OR          |

| ELGO1    | Gated OR                  |

| CLOA1    | OR-AND Gate (2 OR, 1 AND) |

| CLOA3    | 3-3-3 AND / OR            |

| CLOAND1  | OR-AND / NAND Gate (2×4)  |

| CLOAND2  | OR-AND/NAND Gate (2×4)    |

| Evoluciu | OP Functions              |

| Fxc | lusive | OR | Func | tions |

|-----|--------|----|------|-------|

| ELXR1    | 3 Input EXOR/EXNOR        |

|----------|---------------------------|

| ELXR4    | 3 Input EXOR/EXNOR        |

| ELXR2    | 4 Input EXOR              |

| ELXR3    | 6 Input EXOR              |

| ELOXR1   | 2-2 OR/EXOR               |

| ELAXNR1  | 2-1-1-2 OR / AND / XNOR   |

| ELAXNR2  | Dual 2-2 OR / AND / EXNOR |

| ELAXNR3  | Dual 2-2 OR / AND / EXNOR |

| ELXNR1   | 4 Input EXNOR             |

| ELXNR2   | 6 Input EXNOR             |

| ELOAXR1  | 2-1-1-2 OR / AND / XOR    |

| ELXRA1   | 2-1 XOR/AND/NAND          |

| ELXRA2   | 2-1 XOR/AND/NAND          |

| ELAXR1   | 2-1 AND/EXOR              |

| CLXR1    | 2 Input EXOR              |

| CLXRXR1  | 2-2 OR/EXOR               |

| CLONRXR1 | 8 Input OR / NOR / EXOR   |

# Multiplexers

| ELMX1  | 2:1 MUX                        |

|--------|--------------------------------|

| ELMX2  | 2:1 MUX w/Active Low Enable    |

| ELMX10 | 2:1 MUX w/Enable (Low)         |

| ELMX11 | 2:1 MUX w/Enable (High)        |

| FLMX3  | 2:1 MUX w/Gated Inputs         |

| ELMX4  | 2:1 MUX w/Different Inputs and |

|        | Different MUX Control          |

| ELMX5  | Dual 2:1 MUX w/Common Select   |

| ELMX6  | Dual 2:1 MUX w/Common Select   |

| ELMX13 | Dual 2:1 MUX w/Enable (Low)    |

| ELMX7  | Dual Differential 2:1 MUX      |

| ELMX15 | Expandable 2:1 MUX             |

| ELMX16 | Expandable 2:1 MUX             |

| ELMX17 | Expandable 2:1 MUX             |

| ELMX18 | Expandable 2:1 MUX (Coder) and |

|        | Ďual 2:1 MUX                   |

| ELMX14 | Triple 2:1 MUX w/Common Select |

| ELMX12 | Triple 2:1 MUX                 |

| ELMX8  | Quad 2:1 MUX                   |

| ELMX9  | Quad 2:1 MUX                   |

| ELMX20 | 4:1 MUX                        |

| ELMX21 | 4:1 MUX w/Enable (Low)         |

| ELMX22 | 4:1 MUX w/Enable (Low)         |

| ELMX23 | 4:1 MUX w/Enable (High)        |

| ELMX26 | 4:1 MUX w/Enable (High)        |

| ELMX24 | 4:1 MUX w/Differential Select  |

| ELMX25 | Dual 4:1 MUX                   |

| ELMX27 | Expandable 4:1 MUX             |

| ELMX28 | Expandable 4:1 MUX             |

| ELMX29 | Expandable 4:1 MUX             |

| ELMX40 | 8:1 MUX w/Enable (High)        |

| ELMX41 | 8:1 MUX w/Enable (High)        |

| ELMX42 | Expandable 8:1 MUX             |

| ELMX43 | Expandable 8:1 MUX             |

| L.     | 1                              |

| Name               | Function                                                                  |

|--------------------|---------------------------------------------------------------------------|

|                    | ers (Cont.)                                                               |

| ELMX44             | Expandable 8:1 MUX                                                        |

| CLMX1<br>CLMX2     | 2-Bit MUX<br>2-Bit MUX (Diff. Addrs.)                                     |

| CLMX3<br>CLMX21    | 2-Bit MUX (Diff. Data)<br>4-Bit MUX                                       |

| CLMX22             | 4-Bit MUX (Diff. Data)                                                    |

| CLMX23<br>CLMX41   | 2×4-Bit MUX<br>8-Bit MUX (Inverted O / P)                                 |

| CLMX42             | 8-Bit MUX (Diff. I/P)                                                     |

| Decoders<br>ELDC1  | 1-of-4 Decoder w/Enable (Low)                                             |

| ELDC5              | 1-of-4 Decoder w/Enable (Low)                                             |

| ELDC2<br>ELDC4     | 1-of-4 Decoder w/Enable (High)<br>1-of-4 Decoder w/Enable (High)          |

| ELDC3<br>ELDC6     | 1-of-4 Decoder (High)<br>1-of-4 Decoder w/Enable (Low)                    |

| ELDC7              | 1-of-4 Decoder w/Enable (High)                                            |

| ELDC8<br>ELDC9     | Expandable 4-1 MUX (Coder) w/Enable<br>8-3 Encoder                        |

| ELDC10<br>CLDMX1   | Expandable 8:1 MUX (Coder) Demultiplexer 1-of-4 w/2 I / Ps                |

| CLDMX2             | Demultiplexer 1-of-2 w/Inhibit                                            |

| Latches            |                                                                           |

| ELLA1<br>ELLA2     | D Latch w/Reset D Latch w/Clk Enable and Reset                            |

| ELLA3              | 3 Data Input D Latch                                                      |

| ELLA4<br>ELLA14    | D Latch w/Data MUX and Reset<br>D Latch w/MUX                             |

| ELLA5<br>ELLA12    | D Latch w/Gated Data and Reset D Latch w/ASYN Set                         |

| ELLA6              | D Latch w/Reset                                                           |

| ELLA7<br>ELLA8     | Gated 4-Way D Latch Dual D Latch, Common Clock,                           |

| ELLA9              | Transparent High Dual D Latch, Common Clock,                              |

| ELLA10             | Transparent Low Dual D Latch w/Reset                                      |

| ELLA13<br>ELLA15   | 3 D Latches, w/Common Clk and Reset<br>3 D Latches, w/Common Clk and Set  |

| ELLA11<br>ELSR1    | Scan D Latch w/ASYNC Set<br>NOR Latch                                     |

| CLLA1              | D Latch-Positive Clock Cntl                                               |

| CLLA2<br>CLLA3     | D Latch-Negative Clock Cntl 2 Bit D Latch-Positive Clock Cntl             |

| CLLA4              | 2 Bit D Latch-Positive Clock Cntl<br>w/Inverted Outputs and Reset         |

| CLLA5<br>CLLA6     | 2 Bit D Latch-Negative Clock Cntl<br>2 Bit D Latch-Negative Clock Cntl    |

|                    | w/Inverted Outputs and Reset                                              |

| CLLA7<br>CLLA8     | 4 Bit D Latch-Positive Clock Cntl 4 Bit D Latch-Negative Clock Cntl       |

| CLLA9<br>CLLA10    | 8 Bit D Latch-Positive Clock Cntl<br>8 Bit D Latch-Negative Clock Cntl    |

| CLLA11             | 2 Bit D Latch with Reset                                                  |

| CLLA12<br>CLSR1    | 2 Bit D Latch w/Set<br>Unclocked RS Latch                                 |

| Flip-Flop          | S                                                                         |

| ELFFD1<br>ELFFD2   | D Flip-Flop, Positive Edge Triggered D Flip-Flop, Negative Edge Triggered |

| ELFFD16            | D Flip-Flop w/Set                                                         |

| ELFFD17<br>ELFFD18 | D Flip-Flop w/Set D Flip-Flop w/Set                                       |

| ELFFD3<br>ELFFD4   | D Flip-Flop w/Set and Reset D Flip-Flop w/MUX                             |

| ELFFD5             | D Flip-Flop w/EXOR                                                        |

| ELFFD6<br>ELFFD7   | D Flip-Flop w/Set and Reset D Flip-Flop w/Reset                           |

| ELFFD8<br>ELFFD9   | D Flip-Flop w/MUX<br>D Flip-Flop, Neg. Edge Trig. w/Reset                 |

| ELFFD19            | D Flip-Flop w/Reset                                                       |

| ELFFD10            | D Flip-Flop, Neg. Edge Trig.<br>w/Data MUX and Reset                      |

| ELFFD20            | D Flip-Flop w/MUX                                                         |

| Name      | Function                                                              |

|-----------|-----------------------------------------------------------------------|

| Flip-Flop | s (Cont.)                                                             |

| ELFFD11   | Scan D Flip-Flop                                                      |

| ELFFD12   | D Flip-Flop w/ASYN Set and Enable                                     |

| ELFFD13   | D Flip-Flop w/Diff. Clock                                             |

| ELFFD14   | D Flip-Flop w/Diff. Clock                                             |

| ELFFD15   | D Flip-Flop w/Diff. Clock and Data                                    |

| CLFFD1    | D M-S Flip-Flop w/Reset Input                                         |

| CLFFD2    | D M-S Flip-Flop w/2-Bit MUX, Set                                      |

| CLFFD3    | 2 D M-S Flip-Flops w/Separate Set and<br>Common Clock                 |

| CLFFD4    | Positive Edge Trig. 2 D M-S Flip-Flop w/Separate Set and Common Clock |

| CLFFD6    | 4 Bit Neg. Edge Trig. M-S Flip-Flop                                   |

| CLFFD5    | 4 Bit Neg. Edge Trig. M-S Flip-Flop                                   |

| CLFFD8    | 8 Bit Neg. Edge Trig. M-S Flip-Flop                                   |

| CLFFD7    | 8 Bit Neg. Edge Trig. M-S Flip-Flop                                   |

| CLFFD9    | Differential D - M-S Flip-Flop w/Reset                                |

| CLFFD10   | Differential MUX - D - M-S Flip-Flop<br>w/Reset and Set Inputs        |

| ELFFD11   | D Flip-Flop w/Reset and Diff. Clock                                   |

| ELFFD12   | D Flip-Flop w/Set and Diff. Clock                                     |

| Adders and | Carry | Look Ahead |

|------------|-------|------------|

|------------|-------|------------|

| ELAD1 | Full Adder                         |

|-------|------------------------------------|

| ELAD2 | Full Adder, Gated Inputs           |

| ELAD3 | Half Adder, Gated Inputs           |

| ELAD4 | 3-Bit Adder, Gated Inputs          |

| ELAD8 | 3-Bit Adder                        |

| ELAD5 | 3-Bit Adder, Gated Inputs          |

| ELAD6 | Gated Adder                        |

| ELAD7 | Triple Full Adder                  |

| ELCL1 | 2 Bit Look Ahead Carry             |

| CLAD1 | Full Adder                         |

| CLAD2 | 2×2-Bit Full Adder                 |

| CLAD3 | Half-Sum Generator, Dual Propagate |

| CLAD4 | 2-Bit Sum Generator                |

| CLCL1 | 4-Bit Carry Look Ahead             |

| CLCL2 | 8-Bit Carry Look Ahead             |

# **Buffers/Drivers**

| ELBF1 | Driver Buffer, 6 Outputs                             |

|-------|------------------------------------------------------|

| ELBF2 | Differential Drvr Buffer, 3 Diff. Outputs            |

| ELBF3 | Differential Line Rovr                               |

| ELBF4 | Differential Line Rovr, Clk Pulse<br>Generators      |

| ELBF5 | Differential Clk Generator (5 Gates)                 |

| ELBF6 | Differential Clk Generator (6 Gates)                 |

| ELBF7 | Differential Clk Generator (6 Gates plus Ext. Gates) |

| CLBF1 | 3-Input Buffered OR / NOR                            |

| CLBF2 | Differential Buffer                                  |

| CLBF3 | Differential Amplifier                               |

| ELEC1 | Dual ECL-CML Converter                               |

| CLCE1 | Triple CML-ECL Converter                             |

|       |                                                      |

## Low Power 25 ohm Cutoff Drivers

|   | E0E0R3                                              | 2 Input OR                                           |  |

|---|-----------------------------------------------------|------------------------------------------------------|--|

| ı | EOEOR4                                              | 4 Input OR                                           |  |

|   | EOEOR5                                              | 2-2 OR Gate                                          |  |

|   | EOEOR6                                              | 2-2 OR Gate                                          |  |

|   | EOEOR7                                              | 5 Input OR                                           |  |

| İ | EOEOR8                                              | 8 Input OR                                           |  |

|   | E0E0A2                                              | 2-2 OR / AND                                         |  |

|   | EOEAO3                                              | Dual AND / OR                                        |  |

|   | EOEMX5                                              | 2:1 MUX                                              |  |

|   | EOEMX6                                              | Dual 2:MUX                                           |  |

|   | EOEMX7                                              | 4:1 MUX                                              |  |

|   | EOEBF2                                              | Differential Buffer                                  |  |

|   | COEOR1 50 ohms OR / NOR - 0 / P Converte w/4 I / Ps |                                                      |  |

|   | COEOR2                                              | 25 ohms OR / NOR = 0 / P Converter w/4 I / Ps        |  |

| į | COEOR3                                              | 50 ohms 4 Input OR / NOR                             |  |

| ĺ | COEOR4                                              | 50 ohms 4 Input OR / NOR                             |  |

|   | COEMX1                                              | COEMX1 2-Bit MUX with Additional<br>Output Converter |  |

|   | COEONR1                                             | OR/NOR w/4 Inputs and Additional O/P Converter       |  |

Continued

| Name                                  | Function                                                                |  |  |

|---------------------------------------|-------------------------------------------------------------------------|--|--|

| Low Power 25 ohm Cutoff Drvrs (Cont.) |                                                                         |  |  |

| COEMX2                                | Diff. MUX w/ O / P Converter                                            |  |  |

| COTBF1<br>COTBF2                      | CML to TTL O/P Converter TTL Tristate O/P Converter                     |  |  |

|                                       |                                                                         |  |  |

| Input Ma                              | cros                                                                    |  |  |

| EIEO1<br>EIENR1                       | 2-Input OR<br>2-Input NOR                                               |  |  |

| EIEONR1                               | 2-Input OR/NOR                                                          |  |  |

| EIEBF1                                | Input Buffer                                                            |  |  |

| EIEBF2                                | Input Buffer                                                            |  |  |

| EIEBF3                                | Differential Buffer                                                     |  |  |

| EIEBF4                                | Differential Buffer                                                     |  |  |

| EIEBF5<br>EIEBF6                      | Differential Buffer Input Buffer                                        |  |  |

| EITBF1                                | TTL Input Converter (TTL to ECL)                                        |  |  |

| CIEBF1                                | ECL 100k/ECL 10 kH Input Converter                                      |  |  |

| CIEBF2                                | Input Differential Amplifier                                            |  |  |

| CIEONR1                               | ECL 100k/ECL 10 kH Input Converter<br>w/2-Input OR / NOR                |  |  |

| CITBF1                                | TTL Input Converter (TTL to CML)                                        |  |  |

| Pad Mac                               | ros, Output                                                             |  |  |

| EPEOT1                                | 25 ohm Pad Macro                                                        |  |  |

| EPEOT2                                | 50 ohm Pad Macro                                                        |  |  |

| EPEBI3                                | 50 ohm Bidirectional Pad Macro                                          |  |  |

| EPEBI4<br>EPEOT5                      | 25 ohm Bidirectional Pad Macro<br>STECL Pad Macro – 0 ohms Series       |  |  |

| EPEOT6                                | STECL Pad Macro - 20 ohms Series                                        |  |  |

| EPEOT7                                | STECL Pad Macro - 40 ohms Series                                        |  |  |

| EPTOT1                                | TTL Output Pad Macro                                                    |  |  |

| EPTOT2                                | TTL Open Collector Output Pad Macro                                     |  |  |

| EPTBI1<br>CPEOT1                      | TTL Bidirectional Pad Macro<br>ECL 10 kH/100 k - 50 ohms                |  |  |

| CPEOT2                                | Pad Macro<br>ECL 10 kH/100 k - 50 ohms                                  |  |  |

| СРЕОТЗ                                | Pad Macro w/additional Delay<br>ECL 10 kH/100 k - 25 ohms               |  |  |

|                                       | Pad Macro  ECL 10 kH/100 k - 25 ohms                                    |  |  |

| CPEOT4                                | Pad Macro w/additional Delay                                            |  |  |

| CPEOT5                                | Source Terminated ECL 10 kH/100 k – 50 ohm Pad Macro                    |  |  |

| CPEOT6                                | Edge Delayed ECL 10 kH/100 k –<br>50 ohm Source Terminated<br>Pad Macro |  |  |

| CPEBI1                                | ECL 10 kH/100 k Bidirectional –<br>50 ohm Pad Macro                     |  |  |

| CPEBI2                                | Edge Delayed ECL 10 kH/100 k –<br>50 ohm Bidirectional                  |  |  |

| CPTOT1                                | TTL Output Pad Macro                                                    |  |  |

| CPTOT2<br>CPTBI1                      | TTL Open Collector Output Pad Macro TTL Bidirectional Pad Macro         |  |  |

| Pad Macros, Input                     |                                                                         |  |  |

| EPEIN1                                | ECL 10 kH/100 k Input Pad Macro                                         |  |  |

| EPEIN2                                | ECL 10 kH/100 k Input Pad Macro                                         |  |  |

|                                       | used for Diff. Structures                                               |  |  |

| EPEIN3                                | ECL 10 kH/100 k Input Pad Macro<br>with High ESD Protection             |  |  |

| EPEIN4                                | ECL 10 kH/100 k Differential Input Pad<br>Macro w/High ESD Protection   |  |  |

| EPTIN1                                | TTL Input Pad Macro                                                     |  |  |

| CPEIN1                                | ECL 10 kH/100 k Input Pad Macro<br>ECL 10 kH/100 k Input Pad Macro for  |  |  |

| CPEIN2                                | ECL 10 kH/100 k Input Pad Macro for                                     |  |  |

Diff. Structures

TTL Input Pad Macro

ECL 10 kH/100 k Input Pad Macro

Macro w/High ESD Protection

ECL 10 kH/100 k Differential Input Pad

w/High ESD Protection

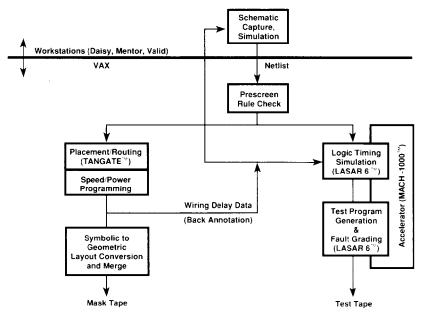

#### CAD

Siemens offers a comprehensive CAD system resident on an internal VAX8700/8550 mainframe cluster.

The interface to the system can be either a captured schematic or a fully simulated netlist generated from a Daisy, Mentor or Valid workstation. As shown in Figure 8, the CAD system supports the following design activities.

- 1. Schematic Capture

- 2. Logic Simulation, including Timing Verification

- 3. Placement and Routing

- 4. Fault Simulation

- Speed/Power Programming

- 6. Test Program generation

- 7. Back Annotation of actual wiring delays

- 8. Mask tape generation

Upon receipt of your captured schematic or simulated netlist, a prescreen rule check is performed to insure that the design adheres to all logic rules surrounding fanout, I/O usage and similar items. Next logic/timing simulation is performed and/or verified depending upon your input using the LASAR 6 reference simulator.

Subsequently, test patterns are created, fault grading performed, and a test program is generated in the

manner indicated in Figure 8. Depending upon the projected run times to accomplish the simulation and fault grading tasks, Siemens also may use the MACH 1000 hardware accelertor tied to the VAX computers in the CAD system. This dedicated accelerator realizes run time improvements of up to 1000X, greatly reducing the time required for such computer intensive activities as fault grading.

Once the logic has been verified and critical path analysis completed, the layout program accesses the models for the macros contained in your schematic first placing each macro and then routing the interconnect wiring. The resistor network used for desired speed/power management is then implemented. At this point, the actual delays due to the interconnect wiring are known, and this data is back annotated into either the LASAR 6 simulator or your workstation for further confirmation that all critical speed paths have been met.

Beyond this point, all that remains is the conversion of the layout to actual geometric data and the creation of a mask tape used for the creation of your personalized set of masks for wafer fabrication. Also a test program is generated using simulation and I/O data of the design.

Figure 8. Siemens ECL CAD System

LASAR 6 is a trademark of the Teradyne Corporation.

TANGATE is a trademark of the Cadence Design Systems, Inc.

MACH 1000 is a trademark of the Zycad Corporation.

CPEIN3

CPEIN4

CPTIN1

#### **Design Interface**

Customer engineers can interface with Siemens in three basic modes. These three modes, as illustrated in Figure 9, are:

- A customer may wish limited design involvement and provide us with a product idea and/or logic diagram with test vectors but no EWS captured schematic simulation results.

- Alternatively, the customer may provide the above (1) plus a netlist capturing his logic diagram using Siemens macros.

- Again alternatively, the customer may interface with us following his own schematic capture, logic/timing simulation, and perhaps fault grading.

Figure 9. Customer Interfaces to the Siemens Design Center

|                                                                                                                                                                                       | 1                                              | 11                        | III                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------|----------------------------------------|--|

| Development Sequence                                                                                                                                                                  | Customer with<br>limited design<br>involvement | Customer with workstation | Customer with workstation or reference |  |

| <ul><li>Product Idea/Logic<br/>Diagram/Test Patterns</li></ul>                                                                                                                        | <b></b>                                        |                           | simulator                              |  |

| <ul> <li>Conversion to Siemens<br/>macrocell family</li> </ul>                                                                                                                        |                                                | <b>\</b>                  |                                        |  |

| <ul> <li>Logic simulation</li> <li>Verification of simulation<br/>(design center and/or<br/>customer)</li> </ul>                                                                      |                                                |                           |                                        |  |

| <ul> <li>Automatic layout<br/>generation</li> <li>Logic simulation with<br/>wiring effects</li> <li>Test program generation</li> <li>Pattern tapes for mask<br/>generation</li> </ul> |                                                | Siemens<br>Design Center  |                                        |  |

| Wafer completion<br>Wafer testing<br>Assembly<br>Prototype delivery                                                                                                                   |                                                | Siemens<br>Sample Produ   | oduction                               |  |

#### **FAB Process**

The Siemens OXIS-IIIH device cross section is shown in Figure 10. OXIS IIIH is a third generation oxide isolated process featuring double poly, self-aligned transistors with polysilicon contacts for collector, base, and emitter regions. These features provide low base-collector region capacitance and low base resistance and together with a small emitter area contribute to a high gain band width product, f<sub>T</sub> of 7 GHz.

Figure 10. Cross Section of npn Transistor OXIS IIIH

#### **Packaging**

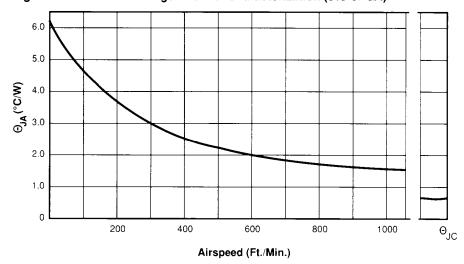

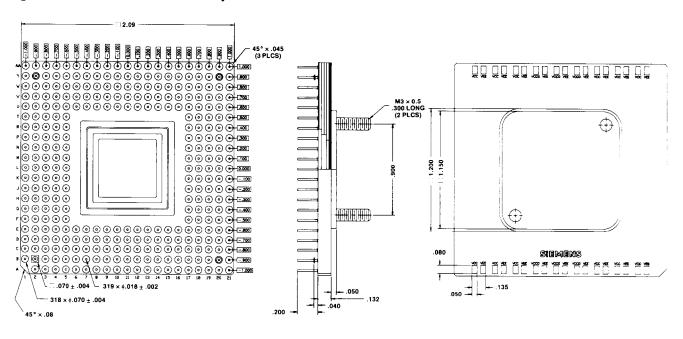

Siemens packaging allows for good thermal resistivity as shown in Figure 11, along with excellent electrical characteristics for pins (inductive, resistive, and capacitive coupling). Table 5 shows actual and planned packages for the SH100E family. An example diagram of the Siemens 319 CPGA (Ceramic Pin Grid Array) is shown in Figure 12.

# **Power Dissipation**

The power dissipation depends upon the selection of the master array, the mix of CML and ECL macros, their speed/power programming and the population of the chip. The relationships for detailed power calculations are provided in the Siemens ECL/CML Design Manual.

Table 5. Actual and Planned Packages for SH100E Family Members

| Complexity | 1,500 | 2,500 | 5,000 | 10,000 |

|------------|-------|-------|-------|--------|

| Pad Count  | 132   | 172   | 224   | 360    |

| PGA        | 88    | 144   | 224   | 319    |

| LCC        | X     | Х     |       |        |

| LLCC       | X     | Х     | Х     | ×      |

X = Planned

Figure 11. SH100E7 Package Thermal Characterization (319 CPGA)

Figure 12. 319 Ceramic Pin Grid Array

The information contained here has been carefully reviewed and is believed to be accurate. However, due to the possibility of unseen inaccuracies, no responsibility is assumed. This literature does not convey to the purchaser of electronic devices any license under the patent rights of the manufacturer.

Issued by Siemens ASIC Products 2191 Laurelwood Road, Santa Clara, CA 95054 (408) 980-4568

©1989 Siemens Components, Inc.