# RP56D, RP336D, and RP144D Low Voltage V.90/K56flex™/V.34/V.32bis Modem Data Pumps for Desktop Applications

# Introduction

The CONEXANT™ RP56D, RP336D, and RP144D Modem Data Pump (MDP) families support data/fax modem, voice coding/decoding, optional full-duplex speakerphone, and optional AudioSpan (Table 1). Low voltage and small size support desktop applications. Downloadable architecture allows upgrading of MDP code from the host/DTE.

In V.90/K56flex mode (RP56), the MDP can receive data at speeds up to 56 kbps from a digitally connected V.90-or K56flex-compatible central site modem. These MDPs take advantage of the PSTN which is primarily digital except for the client modem to central office local loop and are ideal for applications such as remote access to an Internet service provider (ISP), on-line service, or corporate site. The MDP can send upstream data at speeds up to V.34 rates.

In V.34 data mode (RP56 and RC336), the MDP can connect at the highest data rate the channel can support from 33.6 kbps to 2400 bps with auto-fallback to V.32 bis.

In V.32 bis mode, the MDP can connect at the highest data rate the channel can support from 14.4 kbps to 4800 bps with optional auto-fallback to lower rate modulations.

Internal HDLC support eliminates the need for an external serial input/output (SIO) device in the DTE for products incorporating error correction and T.30 protocols.

Voice mode includes an Adaptive Differential Pulse Code Modulation (ADPCM) voice coder and decoder (codec). The codec compresses and decompresses voice signals for efficient digital storage of voice messages. The codec operates at 28.8k, 21.6k, or 14.4k bps (4-bit, 3-bit, or 2-bit quantization, respectively) with a 7.2 kHz or 8.0 kHz sample rate.

A voice pass-through mode allows the host to transmit and receive uncompressed voice samples in 16-bit linear form at 7.2 kHz, 8.0 kHz, or 11.025 kHz sample rate, or in 8-bit A-Law/µ-Law PCM form at 8.0 kHz sample rate.

SP models support position-independent full-duplex speakerphone (FDSP) operation using a dual internal integrated analog circuit to interface with the telephone line and the audio input/out (i.e., a headset, handset, or a microphone with external speaker).

SP models also support AudioSpan (analog simultaneous audio/voice and data) operation at a data rate of 4.8 kbps.

The MDP operates over the public switched telephone network (PSTN) through the appropriate line termination.

## **Features**

- Downloadable MDP code from the host/DTE

- · 2-wire full-duplex

- V.90 and K56flex (RP56 models)

- V.34 (33.6 kbps) (RP56 and RP336 models)

- V.32 bis, V.32, V.22 bis, V.22, V.23, and V.21

- Bell 212 and 103

- 2-wire half-duplex

- V.34 fax, V.17, V.33, V.29, V.27 ter, and V.21 ch 2

- Bell 208

- Short train option in V.17 and V.27 ter

- Serial synchronous and asynchronous data

- Parallel synchronous and asynchronous data

- Parallel synchronous SDLC/HDLC support

- In-band secondary channel (V.34 and V.32 bis)

- Automatic mode selection (AMS)

- Automatic rate adaption (ARA)

- Digital near-end and far-end echo cancellation

- Bulk delay for satellite transmission

- ADPCM voice mode (7.2 kHz or 8.0 kHz)

- Voice pass-through mode (7.2 kHz, 8.0 kHz, or 11.025 kHz)

- Full-duplex speakerphone (SP models)

- Acoustic and line echo cancellation

- Programmable microphone AGC

- Microphone volume selection and muting

- Speaker volume control and muting; room monitor

- AudioSpan (SP models)

- ITU-T V.61 modulation (4.8 kbps data plus audio)

- Handset, headset, or half-duplex speakerphone

- TTL and CMOS compatible DTE interface

- ITU-T V.24 (EIA/TIA-232-E) (data/control)

- Microprocessor bus (data/configuration/control)

- Dynamic range: -9 dBm to -43 dBm

- Adjustable speaker output to monitor received signal

- DMA support interrupt lines

- Transmit and receive (16+128)-byte FIFO data buffers

- NRZI encoding/decoding

- 511 pattern generation/detection

- V.8 and V.8 bis signaling

- V.13 signaling

- Diagnostic capability

- V.54 inter-DCE signaling

- V.54 local analog and remote digital loopback

- +3.3V operation with +5V tolerant inputs

- +5V analog operation

- Power consumption:

- Normal Mode = 280 mW; Sleep Mode = 53 mW

- Low profile, small footprint package

- 100-pin PQFP

Data Sheet Order No. MD218

Rev. 2, December 17, 1998

Table 1. Modem Models and Functions

| Modem/Part Number <sup>1</sup> Packa |          |              | ge and Package         | Options                        | Supported Functions <sup>2</sup> |           |                                             |                    |                           |

|--------------------------------------|----------|--------------|------------------------|--------------------------------|----------------------------------|-----------|---------------------------------------------|--------------------|---------------------------|

| Model Number                         | Part No. | Package      | Clock/Crystal<br>Input | Analog<br>Interface<br>Voltage | V.90/K56flex<br>Data             | V.34 Data | V.32 bis Data,<br>V.34 Fax,<br>Remote Voice | FDSP,<br>AudioSpan | Voice Serial<br>Interface |

| RP56D/SP                             | R6764-61 | 100-Pin PQFP | Clock                  | <b>+</b> 5V                    | Υ                                | Υ         | Υ                                           | Υ                  | =                         |

| RP56D                                | R6764-63 | 100-Pin PQFP | Clock                  | +5V                            | Υ                                | Y         | Y                                           | _                  | -                         |

| RP336D/SP                            | R6764-65 | 100-Pin PQFP | Clock                  | +5V                            | -                                | Υ         | Υ                                           | Υ                  | =                         |

| RP336D                               | R6764-67 | 100-Pin PQFP | Clock                  | +5V                            | -                                | Υ         | Υ                                           | -                  | -                         |

| RP144D/SP                            | R6764-69 | 100-Pin PQFP | Clock                  | +5V                            | -                                | =         | Υ                                           | Υ                  | =                         |

| RP144D                               | R6764-68 | 100-Pin PQFP | Clock                  | +5V                            | -                                | -         | Υ                                           | -                  | -                         |

1. Model/part number options:

D Downloadable SP Speakerphone.

2. Supported functions (Y = Supported; - = Not supported):

FDSP Full-duplex speakerphone

Remote Voice Remote voice record and playback

AudioSpan Analog simultaneous voice and data.

Information provided by CONEXANT SYSTEMS, INC. (CONEXANT) is believed to be accurate and reliable. However, no responsibility is assumed by CONEXANT for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of CONEXANT other than for circuitry embodied in CONEXANT products. CONEXANT reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

K56flex is a trademark of CONEXANT SYSTEMS, INC. and Lucent Technologies. CONEXANT and "What's Next in Communications Technologies" are trademarks of CONEXANT SYSTEMS, INC.

©1998, CONEXANT SYSTEMS, INC. Printed in U.S.A. All Rights Reserved

# **Technical Description**

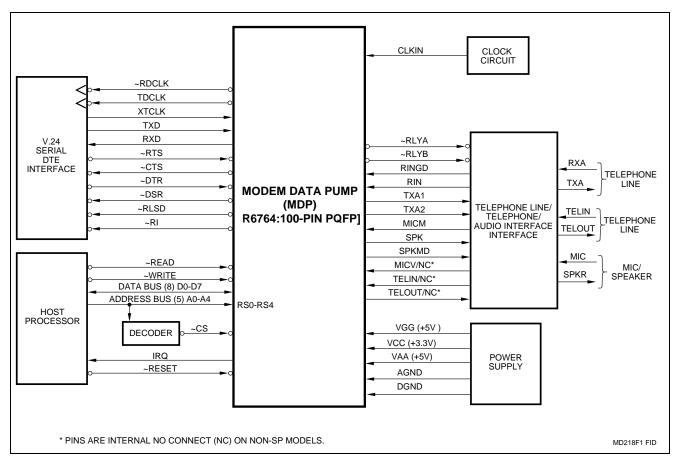

The MDP functional interface is illustrated in Figure 1.

# **Configurations and Rates**

The selectable MDP configurations, signaling rates, and data rates are listed in Table 2.

Figure 1. MDP Functional Interface

Table 2. Configurations, Signaling Rates, and Data Rates

| Configuration                    | Modulation | Carrier Frequency<br>(Hz) ±0.01% | Data Rate (bps)<br>±0.01%      | Symbol Rate<br>(Symbols/Sec.) | Bits/Symbol<br>- Data | Bits/Symbol<br>- TCM | Constellation<br>Points |

|----------------------------------|------------|----------------------------------|--------------------------------|-------------------------------|-----------------------|----------------------|-------------------------|

| V.90/K56flex PCM*                | PCM        | _                                | 56000R/V.34ratesT <sup>4</sup> | 8000                          | Dynamic               | -                    | _                       |

| V.34 33600 TCM**                 | TCM        | Note 2                           | 33600                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 31200 TCM**                 | TCM        | Note 2                           | 31200                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 28800 TCM**                 | TCM        | Note 2                           | 28800                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 26400 TCM**                 | TCM        | Note 2                           | 26400                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 24000 TCM**                 | TCM        | Note 2                           | 24000                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 21600 TCM**                 | TCM        | Note 2                           | 21600                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 19200 TCM**                 | TCM        | Note 2                           | 19200                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 16800 TCM**                 | TCM        | Note 2                           | 16800                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 14400 TCM**                 | TCM        | Note 2                           | 14400                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 12000 TCM**                 | TCM        | Note 2                           | 12000                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 9600 TCM**                  | TCM        | Note 2                           | 9600                           | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 7200 TCM**                  | TCM        | Note 2                           | 7200                           | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 4800 TCM**                  | TCM        | Note 2                           | 4800                           | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 2400 TCM**                  | TCM        | Note 2                           | 2400                           | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.32 bis 14400 TCM               | TCM        | 1800                             | 14400                          | 2400                          | 6                     | 1                    | 128                     |

| V.32 bis 12000 TCM               | TCM        | 1800                             | 12000                          | 2400                          | 5                     | 1                    | 64                      |

| V.32 bis 9600 TCM                | TCM        | 1800                             | 9600                           | 2400                          | 4                     | 1                    | 32                      |

| V.32 bis 7200 TCM                | TCM        | 1800                             | 7200                           | 2400                          | 3                     | 1                    | 16                      |

| V.32 bis 4800                    | QAM        | 1800                             | 4800                           | 2400                          | 2                     | 0                    | 4                       |

| V.32 9600 TCM                    | TCM        | 1800                             | 9600                           | 2400                          | 4                     | 1                    | 32                      |

| V.32 9600                        | QAM        | 1800                             | 9600                           | 2400                          | 4                     | 0                    | 16                      |

| V.32 4800                        | QAM        | 1800                             | 4800                           | 2400                          | 2                     | 0                    | 4                       |

| V.22 bis 2400                    | QAM        | 1200/2400                        | 2400                           | 600                           | 4                     | 0                    | 16                      |

| V.22 bis 1200                    | DPSK       | 1200/2400                        | 1200                           | 600                           | 2                     | 0                    | 4                       |

| V.22 1200                        | DPSK       | 1200/2400                        | 1200                           | 600                           | 2                     | 0                    | 4                       |

| V.22 600                         | DPSK       | 1200/2400                        | 600                            | 600                           | 1                     | 0                    | 4                       |

| V.23 1200/75                     | FSK        | 1700/420                         | 1200/75                        | 1200                          | 1                     | 0                    | -                       |

| V.21                             | FSK        | 1080/1750                        | 0–300                          | 300                           | 1                     | 0                    | -                       |

| Bell 208 4800                    | DPSK       | 1800                             | 4800                           | 1600                          | 3                     | 0                    | 8                       |

| Bell 212A                        | DPSK       | 1200/2400                        | 1200                           | 600                           | 2                     | 0                    | 4                       |

| Bell 103                         | FSK        | 1170/2125                        | 0–300                          | 300                           | 1                     | 0                    | -                       |

| V.23 1200/75                     | FSK        | 1700/420                         | 1200/75                        | 1200                          | 1                     | 0                    | -                       |

| V.21                             | FSK        | 1080/1750                        | 0–300                          | 300                           | 1                     | 0                    | -                       |

| V.17 14400 TCM/V.33 <sup>3</sup> | TCM        | 1800                             | 14400                          | 2400                          | 6                     | 1                    | 128                     |

| V.17 12000 TCM/V.33 <sup>3</sup> | TCM        | 1800                             | 12000                          | 2400                          | 5                     | 1                    | 64                      |

| V.17 9600 TCM <sup>3</sup>       | TCM        | 1800                             | 9600                           | 2400                          | 4                     | 1                    | 32                      |

| V.17 7200 TCM <sup>3</sup>       | TCM        | 1800                             | 7200                           | 2400                          | 3                     | 1                    | 16                      |

| V.29 9600 <sup>3</sup>           | QAM        | 1700                             | 9600                           | 2400                          | 4                     | 0                    | 16                      |

| V.29 7200 <sup>3</sup>           | QAM        | 1700                             | 7200                           | 2400                          | 3                     | 0                    | 8                       |

| V.29 4800 <sup>3</sup>           | QAM        | 1700                             | 4800                           | 2400                          | 2                     | 0                    | 4                       |

| V.27 4800 <sup>3</sup>           | DPSK       | 1800                             | 4800                           | 1600                          | 3                     | 0                    | 8                       |

| V.27 4800 <sup>3</sup>           | DPSK       | 1800                             | 2400                           | 1200                          | 2                     | 0                    | 4                       |

| V.21 Channel 2 <sup>3</sup>      | FSK        | 1750                             | 300                            | 300                           | 1                     | 0                    | _                       |

| Tone Transmit                    | _          | _                                | _                              | -                             | _                     | _                    | _                       |

|                                  | 1          | ı                                |                                |                               | 1                     | l .                  | l .                     |

1. Modulation legend: TCM: Trellis-Coded Modulation QAM: Quadrature Amplitude Modulation FSK: Frequency Shift Keying DPSK: Differential Phase Shift Keying

2. Adaptive; established during handshake:

# Carrier Frequency (Hz)

| Symbol Rate (Baud) | V.34 Low Carrier | V.34 High Carrier |

|--------------------|------------------|-------------------|

| 2400               | 1600             | 1800              |

| 2800               | 1680             | 1867              |

| 3000               | 1800             | 2000              |

| 3200               | 1829             | 1920              |

| 3429               | 1959             | 1959              |

- 3. Models with fax support only.

- 4. Maximum data rate.

- \* RP56 models only.

- \*\* RP56 and RP336 models only.

4 MD218

#### **Automatic Mode Selection**

When automatic mode selection (AMS) is enabled, the MDP configures itself to the highest compatible data rate supported by the remote modem (AUTO bit). Automode operation is supported in V.90, K56flex, V.34, V.32 bis, V.32 V.22 bis, V.22, V.21, V.23, Bell 212A, and Bell 103 modes.

#### **Automatic Rate Adaption (ARA)**

In V.90, K56flex, V.34, and V.32 bis modes, automatic rate adaption (ARA) can be enabled to select the highest data rate possible based on the measured eye quality monitor (EQM) (EARC bit). This selection occurs during handshake/retrain and rate renegotiation.

#### **Tone Generation**

The MDP can generate single or dual voice-band tones from 0 Hz to 3600 Hz with a resolution of 0.15 Hz and an accuracy of  $\pm$  0.01%. Tones over 3000 Hz are attenuated. DTMF tone generation allows the MDP to operate as a programmable DTMF dialer.

#### **Data Encoding**

The data encoding conforms to ITU-T recommendations V.90, V.34, V.32 bis, V.32, V.17, V.33, V.29, V.27 ter, V.22 bis, V.22, V.23, or V.21, and is compatible with Bell 208, 212A, or 103, depending on the model and selected configuration.

## **RTS - CTS Response Time**

The response times of CTS relative to a corresponding transition of RTS are listed in Table 3.

#### **Transmit Level**

The transmitter output level is selectable from 0 dBm to -15 dBm (VAA = +5V) in 1 dB steps and is accurate to ±0.5 dB when used with an external hybrid. The output level can also be fine tuned by changing a gain constant in MDP DSP RAM. The maximum V.34/V.32 bis/V.32 transmit level for acceptable receive performance should not exceed -9 dBm.

**Note:** In V.34 mode, the transmit level may be automatically changed during the handshake. This automatic adjustment of the transmit level may be disabled via a parameter in DSP RAM.

### **Transmitter Timing**

Transmitter timing is selectable between internal (±0.01%), external, or slave.

# Scrambler/Descrambler

A self-synchronizing scrambler/descrambler is used in accordance with the selected configuration.

#### **Answer Tone**

When the NV25 bit is a zero, the MDP generates a 2100 Hz answer tone at the beginning of the answer handshake for 5.0 seconds (V.8) or 3.6 seconds (V.32 bis, V.32, V.22 bis, V.22, V.23, and V.21). The answer tone has 180° phase reversals every 0.45 second to disable network echo cancellers (V.8, V.32 bis, V.32).

Table 3. RTS-CTS Response Times

| Configuration                          | RTS-CTS Constant Carrier | Response <sup>1</sup> Controlled Carrier | Turn-Off<br>Sequence <sup>3</sup> |

|----------------------------------------|--------------------------|------------------------------------------|-----------------------------------|

| V.90, K56flex, V.34,<br>V.32 bis, V.32 | ± 2 ms                   | N/A                                      | N/A                               |

| V.33/V.17 Long                         | N/A                      | 1393 ms <sup>2</sup>                     | 15 ms <sup>4</sup>                |

| V.33/V.17 Short                        | N/A                      | 142 ms <sup>2</sup>                      | 15 ms <sup>4</sup>                |

| V.29                                   | N/A                      | 253 ms <sup>2</sup>                      | 12 ms                             |

| V.27 4800 Long                         | N/A                      | 708 ms <sup>2</sup>                      | 7 ms <sup>4</sup>                 |

| V.27 4800 Short                        | N/A                      | 50 ms <sup>2</sup>                       | 7 ms <sup>4</sup>                 |

| V.27 2400 Long                         | N/A                      | 943 ms <sup>2</sup>                      | 10 ms <sup>4</sup>                |

| V.27 2400 Short                        | N/A                      | 67 ms <sup>2</sup>                       | 10 ms <sup>4</sup>                |

| V.22 bis, V.22,<br>Bell 212A           | ± 2 ms                   | 270 ms                                   | N/A                               |

| V.21                                   | 500 ms                   | 500 ms                                   | N/A                               |

| V.23, Bell 103                         | 210 ms                   | 210 ms                                   | N/A                               |

#### Notes:

- Times listed are CTS turn-on. The CTS OFF-to-ON response time is host programmable in DSP RAM. (Fullduplex modes only.)

- 2. Add echo protector tone duration plus 20 ms when echo protector tone is used during turn-on.

- Turn-off sequence consists of transmission of remaining data and scrambled ones for controlled carrier operation. CTS turn-off is less than 2 ms for all configurations.

- 4. Plus 20 ms of no transmitted energy.

- 5. N/A = not applicable.

### Receive Level

The MDP satisfies performance requirements for received line signal levels from –9 dBm to –43 dBm measured at the Receiver Analog (RXA) (TIP and RING) input (-15 dBm at RIN).

**Note:** A 6 dB pad is required between TIP and RING and the RIN input.

# **Receiver Timing**

The timing recovery circuit can track a frequency error in the associated transmit timing source of  $\pm 0.035\%$  (V.22 bis) or  $\pm 0.01\%$  (other configurations).

# **Carrier Recovery**

The carrier recovery circuit can track a ±7 Hz frequency offset in the received carrier.

# Clamping

Received Data (RXD) is clamped to a constant mark whenever the Received Line Signal Detector (~RLSD) is off. ~RLSD can be clamped off (RLSDE bit).

#### **Echo Canceller**

A data echo canceller with near-end and far-end echo cancellation is included for 2-wire full-duplex V.34/V.32 bis/V.32 operation. The combined echo span of near and far cancellers can be up to 40 ms. The proportion allotted to each end is automatically determined by the MDP. The delay between near-end and far-end echoes can be up to 1.2 seconds.

V.90 and K56flex echo cancellation is also provided.

#### **ADPCM Voice Mode**

The Adaptive Differential Pulse Code Modulation (ADPCM) voice coder and decoder (codec) compresses and decompresses voice signals for efficient digital storage of voice messages. The codec operates at 28.8k, 21.6k, or 14.4k bps (4-bit, 3-bit, or 2-bit quantization, respectively) with a 7.2 kHz or 8.0 kHz sample rate.

**Transmit Voice.** 16-bit compressed transmit voice can be sent to the MDP ADPCM codec for decompression then to the digital-to-analog converter (DAC) by the host.

**Receive Voice.** 16-bit received voice samples from the MDP analog-to-digital converter (ADC) can be sent to the ADPCM codec for compression, and then be read by the host.

# **Voice Pass-Through Mode**

Voice pass-through mode allows the host to transmit and receive uncompressed voice samples in 16-bit linear form at 7.2 kHz, 8.0 kHz, or 11.025 kHz sample rate, or in 8-bit A-Law/ $\mu$ -Law PCM form at 8.0 kHz sample rate.

**Transmit Voice.** Transmit voice samples can be sent to the MDP DAC from the host.

**Receive Voice.** Received voice samples from the MDP ADC can be read by the host.

### Speakerphone Voice/Audio Paths (SP Models)

The MDP incorporates a dual integrated analog interface. The voice/audio transmit and receive signals can be routed through several paths. The voice/audio paths are available in the speakerphone mode configuration and are selected through DSP RAM.

The voice/audio input can be taken from one of four different sources: telephone line input (RIN), handset (TELIN), microphone (MICM or MICV).

The speaker output (SPK) can originate from one of five different sources: RIN, TELIN, MICM or MICV or from the MDP's internal voice playback mode.

The voice/audio output may be routed to the telephone line output (TXA1 and TXA2) or handset (TELOUT).

The voice paths can be switched to allow an audio input to be routed to the telephone line output through a variable gain for applications such as music-on-hold.

The "room monitor" mode allows the MDP to receive audio from its surroundings and concurrently transmit the audio to a remote site.

#### AudioSpan Mode (SP Models)

AudioSpan provides full-duplex analog simultaneous audio/voice and data over a single telephone line at a data rate with audio of 4800 bps using V.61 modulation. AudioSpan can send any type of audio waveform, including music. Data can be sent with or without error correction. The audio/voice interface can be in the form of a headset, handset, or a microphone and speaker (half-duplex speakerphone). Handset echo cancellation is provided.

#### **Data Formats**

### **Serial Synchronous Data**

Data rate: 300-56000 bps (RP56), 300-33600 bps (RP56 and RP336), or 300-14400 bps.

±0.01%.

Selectable clock: Internal, external, or slave.

### **Serial Asynchronous Data**

Data rate: 300-56000 bps (RP56), 300-33600 bps

(RP56 and RP336), or 300-14400 bps,

+1% (or +2.3%), -2.5%;

0-300 bps (V.21 and Bell 103);

1200/75 bps (V.23).

Bits per character: 7, 8, 9, 10, or 11.

#### **Parallel Synchronous Data**

Normal sync: 8-bit data for transmit and receive

Data rate: 300-56000 bps (RP56), 300-33600 bps

(RP56 and RP336), or 300-14400 bps,

±0.01%.

SDLC/HDLC support:

Transmitter: Flag generation, 0 bit stuffing,

CRC-16 or CRC-32 generation.

Receiver: Flag detection, 0 bit deletion,

CRC-16 or CRC-32 checking.

# **Parallel Asynchronous Data**

Data rate: 300-56000 bps (RP56), 300-33600 bps

(RP56 and RP336), or 300-14400 bps,

+1% (or 2.3%), -2.5%;

1200, 300, or 75 bps (FSK).

Data bits per character: 5, 6, 7, or 8.

Parity generation/checking: Odd, even, or 9th data bit.

# Async/Sync and Sync/Async Conversion

An asynchronous-to-synchronous converter is provided in the transmitter and a synchronous-to-asynchronous converter is provided in the receiver. The converters operate in both serial and parallel modes. The asynchronous character format is 1 start bit, 5 to 8 data bits, an optional parity bit, and 1 or 2 stop bits. Valid character size, including all bits, is 7, 8, 9, 10, or 11 bits per character. Two ranges of signaling rates are provided:

MD218

- Basic range: +1% to −2.5%

- Extended overspeed range: +2.3% to −2.5%

When the transmitter's converter is operating at the basic signaling rate, no more than one stop bit will be deleted per 8 consecutive characters. When operating at the extended rate, no more than one stop bit will be deleted per 4 consecutive characters. Break handling is performed as described in V.14.

Asynchronous characters are accepted on the TXD serial input and are issued on the RXD serial output.

#### V.54 Inter-DCE Signaling

The MDP supports V.54 inter-DCE signaling procedures in synchronous and asynchronous configurations. Transmission and detection of the preparatory, acknowledgment, and termination phases as defined in V.54 are provided. Three control bits in the transmitter allow the host to send the appropriate bit patterns (V54T, V54A, and V54P bits). Three control bits in the receiver are used to enable one of three bit pattern detectors (V54TE, V54AE, and V54PE bits). A status bit indicates when the selected pattern detector has found the corresponding bit pattern (V54DT bit).

# V.13 Remote RTS Signaling

The MDP supports V.13 remote RTS signaling. Transmission and detection of signaling bit patterns in response to a change of state in the RTS bit or the ~RTS input signal are provided. The RRTSE bit enables V.13 signaling. The RTSDE bit enables detection of V.13 patterns. The RTSDT status bit indicates the state of the remote RTS signal. This feature may be used to clamp/unclamp the local ~RLSD and RXD signals in response to a change in the remote RTS signal in order to simulate controlled carrier operation in a constant carrier environment. The MDP automatically clamps and unclamps ~RLSD.

#### **Dialing and Answering**

The host can dial and answer using supported DTMF/pulse dialing and tone detection functions. The major parameters are host programmable.

# **Supervisory Tone Detection**

Three parallel tone detectors (A, B, and C) are provided for supervisory tone detection. The signal path to these detectors is separate from the main received signal path.

Each tone detector consists of two cascaded second order IIR biquad filters. The coefficients are host programmable. Each fourth order filter is followed by a level detector which has host programmable turn-on and turn-off thresholds allowing hysteresis. Tone detector C is preceded by a prefilter and squarer. This circuit is useful for detecting a tone with frequency equal to the difference between two tones that may be simultaneously present on the line. The squarer may be disabled by the SQDIS bit causing tone detector C to be an eighth order filter. The tone detectors are disabled in data mode.

The tone detection sample rate is 9600 Hz in V.8 and V.34 modes and is 7200 Hz in non-V.34 modes. The default call progress filter coefficients are based on a 7200 Hz sampling rate and apply to non-V.34 modes only.

The maximum detection bandwidth is equal to one-half the sample rate.

The default bandwidths and thresholds of the tone detectors are:

| Tone Detector | Bandwidth    | Turn-On<br>Threshold | Turn-Off<br>Threshold |

|---------------|--------------|----------------------|-----------------------|

| Α             | 245 – 650 Hz | –25 dBm              | –31 dBm               |

| В             | 360 – 440 Hz | –25 dBm              | –31 dBm               |

| C Prefilter   | 0 – 500 Hz   | N/A                  | N/A                   |

| С             | 50 – 110 Hz  | *                    | *                     |

<sup>\*</sup> Tone Detector C will detect a difference tone within its bandwidth when the two tones present are in the range –1 dBm to –26 dBm.

#### 511 Pattern Generation/Detection

In synchronous mode, a 511 pattern can be generated and detected (control bit S511). Use of this bit pattern during self-test eliminates the need for external test equipment.

### **In-Band Secondary Channel**

A full-duplex in-band secondary channel is provided in V.34 (all speeds) and V.32 bis/V.32 (7200 bps and above) modes. Control bit SECEN enables and disables the secondary channel operation. The secondary channel operates in parallel data mode with independent transmit and receive interrupts and data buffers. The main channel may operate in parallel or serial mode.

In V.34 modes, the secondary channel rate is 200 bps.

In V.32 bis/V.32 modes, the secondary channel rate is 150 bps. This rate is also host programmable in V.32 bis/V.32 modes.

# **Transmit and Receive FIFO Data Buffers**

Two (16+128)-byte first-in first-out (FIFO) data buffers allow the DTE/host to rapidly output up to 144 bytes of transmit data and input up to 144 bytes of accumulated received data. The receiver FIFO is always enabled. The transmitter FIFO is enabled by the FIFOEN control bit. TXHF and RXHF bits operate off the lower 16 bits and indicate the corresponding FIFO buffer half full (8 or more bytes loaded) status. TXFNF and RXFNE bits indicate the TXFIFO buffer not full and RXFIFO buffer not empty status, respectively. An interrupt mask register allows an interrupt request to be generated whenever the TXFNF, RXFNE, RXHF, or TXHF status bit changes state. The 128-byte FIFO extensions are enabled by default and can be disabled by clearing a bit in RAM.

# **DMA Support Interrupt Request Lines**

DMA support is available in synchronous, asynchronous, and HDLC parallel data modes. Control bit DMAE enables and disables DMA support. When DMA support is enabled, the MDP ~RI and ~DSR lines are assigned to Transmitter Request (TXRQ) and Receiver Request (RXRQ) hardware output interrupt request lines, respectively. The TXRQ and RXRQ signals follow the assertion of the TDBE and RDBF interrupt bits thus allowing the DTE/host to respond immediately to the

interrupt request without masking out status bits to determine the interrupt source.

## **NRZI** Encoding/Decoding

NRZI data encoding/decoding may be selected in synchronous and HDLC modes instead of the default NRZ (control bit NRZIEN). In NRZ encoding, a 1 is represented by a high level and a 0 is represented by a low level. In NRZI encoding, a 1 is represented by no change in level and a 0 is represented by a change in level.

# **ITU-T CRC-32 Support**

ITU-T CRC-32 generation/checking may be selected instead of the default ITU-T CRC-16 in HDLC mode using DSP RAM access.

#### **Caller ID Demodulation**

Caller ID information can be demodulated in V.23 1200 receive configuration and presented to the host/DTE in serial (RXD) and parallel (RBUFFER) form.

# **Telephone Line Interface**

Line Transformer Interface. V.90/K56flex/V.34/V.32 bis/V.32 places high requirements upon the Data Access Arrangement (DAA) to the telephone line. Any non-linear distortion generated by the DAA in the transmit direction cannot be canceled by the MDP's echo canceller and interferes with data reception. The designer must, therefore, ensure that the total harmonic distortion seen at the RXA input to the MDP be at least 65 dB below the minimum level of received signal. Due to the wider bandwidth requirements in V.90, K56flex, and V.34, the DAA must maintain linearity from 10 Hz to 4000 Hz.

**Relay Control.** Direct control of the off-hook and talk/data relays is provided. Internal relay drivers allow direct connection to the off-hook (RLYA) and talk/data (RLYB) relays. The talk/data relay output can optionally be used for pulse dial.

#### **Speaker Interface**

An analog speaker output (SPK) is provided with on/off and volume control logic incorporated in the MDP. An external amplifier is recommended if driving non-amplified speakers.

A digital speaker output (SPKMD) is provided which reflects the received analog input signal digitized to TTL high or low level by an internal comparator to create a PC Card (PCMCIA)-compatible signal.

### **Additional Information**

Additional information is provided in the RP56D, RP336D, and RP144D Modem Designer's Guide (Order No. 1155).

# **Hardware Interface Signals**

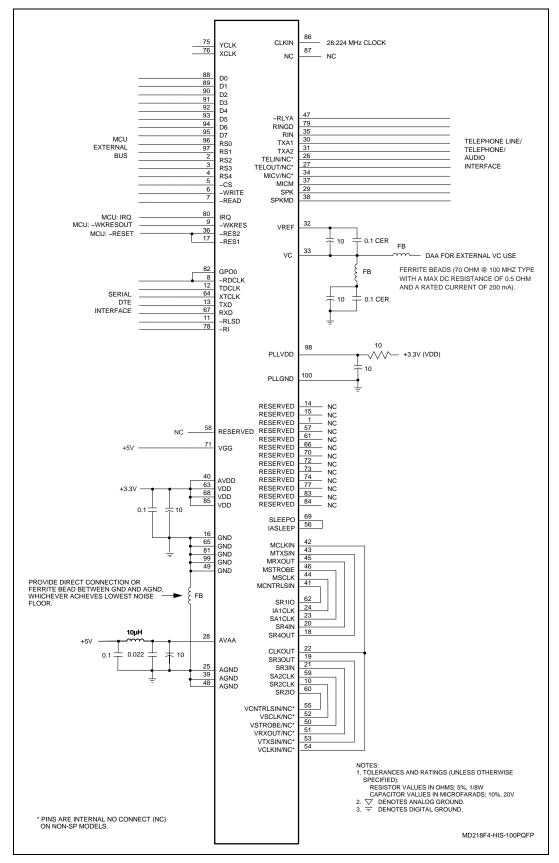

A functional interconnect diagram showing the typical MDP connection in a system is illustrated in Figure 2. Any point that is active low is represented by a small circle at the signal point.

Edge triggered inputs are denoted by a small triangle (e.g., TDCLK). An active low signal is indicated by a tilde preceding the signal name (e.g., ~RESET).

A clock intended to activate logic on its rising edge (low-to-high transition) is called active low (e.g., ~RDCLK), while a clock intended to activate logic on its falling edge (high-to-low transition) is called active high (e.g., TDCLK). When a clock input is associated with a small circle, the input activates on a falling edge. If no circle is shown, the input activates on a rising edge.

The 100-pin PQFP MDP hardware interface signals are shown Figure 2.

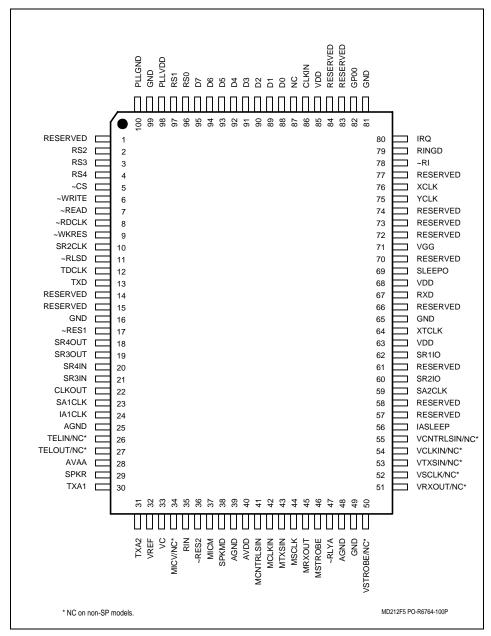

The 100-pin PQFP MDP signal pin assignments are shown Figure 3 and are listed in Table 4.

The MDP hardware interface signals are described in Table 5.

The digital interface characteristics are defined in Table 6.

The analog interface characteristics are defined Table 7.

The power requirements are defined in Table 8.

The absolute maximum ratings are defined in Table 9.

Figure 2. MDP Hardware Interface Signals-100-Pin PQFP

10

Figure 3. MDP Pin Signals - 100-Pin PQFP

Table 4. MDP Pin Signals - 100-Pin PQFP

| Pin | Signal Label | I/O Type | Interface <sup>3</sup>                        | Pin | Signal Label  | I/O Type | Interface                                                         |

|-----|--------------|----------|-----------------------------------------------|-----|---------------|----------|-------------------------------------------------------------------|

| 1   | RESERVED     |          | NC                                            | 51  | VRXOUT/NC*    | DI       | To SR3IN (21)                                                     |

| 2   | RS2          | IA       | Host Parallel Interface                       | 52  | VSCLK/NC*     | DI       | To SR2CLK (10)                                                    |

| 3   | RS3          | IA       | Host Parallel Interface                       | 53  | VTXSIN/NC*    | DI       | To SR3OUT (19)                                                    |

| 4   | RS4          | IA       | Host Parallel Interface                       | 54  | VCLKIN/NC*    | DI       | To CLKOUT (22)                                                    |

| 5   | ~CS          | IA       | Host Parallel Interface                       | 55  | VCNTRLSIN/NC* | DI       | To SR2IO (60)                                                     |

| 6   | ~WRITE       | IA       | Host Parallel Interface                       | 56  | IASLEEP       | DI       | To SLEEPO (69)                                                    |

| 7   | ~READ        | IA       | Host Parallel Interface                       | 57  | RESERVED      |          | NC                                                                |

| 8   | ~RDCLK       | OA       | DTE Serial Interface                          | 58  | RESERVED      |          | NC                                                                |

| 9   | ~WKRES       | IA       | MCU: READY/~WKRESOUT                          | 59  | SA2CLK        | DI       | To VSTROBE (50)                                                   |

| 10  | SR2CLK       | DI       | To VSCLK (52)                                 | 60  | SR2IO         | DI       | To VCNTRLSIN (55)                                                 |

| 11  | ~RLSD        | OA       | DTE Serial Interface                          | 61  | RESERVED      |          | NC                                                                |

| 12  | TDCLK        | OA       | DTE Serial Interface                          | 62  | SR1IO         | DI       | To MCNTRLSIN (41)                                                 |

| 13  | TXD          | IA       | DTE Serial Interface                          | 63  | VDD           | PWR      | +3.3V                                                             |

| 14  | RESERVED     |          | NC                                            | 64  | XTCLK         | IA       | DTE Serial Interface                                              |

| 15  | RESERVED     |          | NC                                            | 65  | GND           | GND      | DGND                                                              |

| 16  | GND          | GND      | DGND                                          | 66  | RESERVED      |          | NC                                                                |

| 17  | ~RES1        |          | PIF: ~RESET<br>SIF: Reset circuit             | 67  | RXD           | OA       | DTE Serial Interface                                              |

| 18  | SR4OUT       | DI       | To MTXSIN (43)                                | 68  | VDD           | PWR      | +3.3V                                                             |

| 19  | SR3OUT       | DI       | To VTXSIN (53)                                | 69  | SLEEPO        | DI       | To IASLEEP (56)                                                   |

| 20  | SR4IN        | DI       | To MRXOUT (45)                                | 70  | RESERVED      |          | NC                                                                |

| 21  | SR3IN        | DI       | To VRXOUT (51)                                | 71  | VGG           | REF      | +5V                                                               |

| 22  | CLKOUT       | DI       | To MCLKIN (42) & VCLKIN (54)                  | 72  | RESERVED      |          | NC                                                                |

| 23  | SA1CLK       | DI       | To MSTROBE (46)                               | 73  | RESERVED      |          | NC                                                                |

| 24  | IA1CLK       | DI       | To MSCLK (44)                                 | 74  | RESERVED      |          | NC                                                                |

| 25  | AGND         | GND      | Analog Ground                                 | 75  | YCLK          | OA       | NC                                                                |

| 26  | TELIN/NC*    | I(DA)    | Line/Audio Interface                          | 76  | XCLK          | OA       | NC                                                                |

| 27  | TELOUT/NC*   | O(DD)    | Line/Audio Interface                          | 77  | RESERVED      |          | NC                                                                |

| 28  | AVAA         | PWR      | +5VA                                          | 78  | ~RI           | OA       | DTE Serial Interface                                              |

| 29  | SPK          | O(DF)    | Line/Audio Interface                          | 79  | RINGD         | IA       | Line/Audio Interface                                              |

| 30  | TXA1         | O(DD)    | Line/Audio Interface                          | 80  | IRQ           | IA       | Host Parallel Interface                                           |

| 31  | TXA2         | O(DD)    | Line/Audio Interface                          | 81  | GND           | GND      | DGND                                                              |

| 32  | VREF         | REF      | VC through capacitors                         | 82  | GP00          | DI       | To ~RDCLK (8)                                                     |

| 33  | VC           | REF      | DAA through FB; GND through capacitors and FB | 83  | RESERVED      |          | NC                                                                |

| 34  | MICV/NC*     | I(DA)    | Line/Audio Interface                          | 84  | RESERVED      |          | NC                                                                |

| 35  | RIN          | I(DA)    | Line/Audio Interface                          | 85  | VDD           | PWR      | +3.3V                                                             |

| 36  | ~RES2        |          | PIF: ~RESET<br>SIF: Reset circuit             | 86  | CLKIN         | I        | Clock Circuit                                                     |

| 37  | MICM         | I(DA)    | Line/Audio Interface                          | 87  | NC            |          | NC                                                                |

| 38  | SPKMD        | OA       | Line/Audio Interface                          | 88  | D0            | IA/OB    | Host Parallel Interface                                           |

| 39  | AGND         | GND      | Analog Ground                                 | 89  | D1            | IA/OB    | Host Parallel Interface                                           |

| 40  | AVDD         | PWR      | +3.3V                                         | 90  | D2            | IA/OB    | Host Parallel Interface                                           |

| 41  | MCNTRLSIN    | DI       | To SR1IO (62)                                 | 91  | D3            | IA/OB    | Host Parallel Interface                                           |

| 42  | MCLKIN       | DI       | To CLKOUT (22)                                | 92  | D4            | IA/OB    | Host Parallel Interface                                           |

| 43  | MTXSIN       | DI       | To SR4OUT (18)                                | 93  | D5            | IA/OB    | Host Parallel Interface                                           |

| 44  | MSCLK        | DI       | To IA1CLK (24)                                | 94  | D6            | IA/OB    | Host Parallel Interface                                           |

| 45  | MRXOUT       | DI       | To SR4IN (20)                                 | 95  | D7            | IA/OB    | Host Parallel Interface                                           |

| 46  | MSTROBE      | DI       | To SA1CLK (23)                                | 96  | RS0           | IA       | Host Parallel Interface                                           |

| 47  | ~RLYA        | OD       | NC                                            | 97  | RS1           | IA       | Host Parallel Interface                                           |

| 48  | AGND         | GND      | AGND                                          | 98  | PLLVDD        | PLL      | To +3.3 (VDD) through 10 $\Omega$ and to DGND through 10 $\mu$ F. |

| 49  | GND          | GND      | DGND                                          | 99  | GND           | GND      | DGND                                                              |

| 50  | VSTROBE/NC*  | DI       | To SA2CLK (59)                                | 100 | PLLGND        | PLL      | DGND                                                              |

1. I/O types

IA, IB = Digital input; OA, OB = Digital output.

I(DA) = Analog input; O(DD), O(DF) = Analog output.

DI = Device interconnect.

2. NC = No external connection allowed (may have internal connection).

Interface Legend:

MDP = Modem Data Pump

DTE = Data Terminal Equipment

PIF = Parallel host interface

SIF = Serial DTE interface.

\* NC on non-SP models.

Table 5. MDP Signal Definitions

| Label                           | I/O Type                         | Signal/Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | "С Турс                          | OVERHEAD SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CLKIN                           | 1                                | Clock In. Connect to an external 28.224 MHz clock circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ~RES1,<br>~RES2                 | IA                               | Reset. ~RESET low holds the MDP in the reset state. ~RESET going high releases the MDP from the reset state and initiates normal operation using power turn-on (default) values. ~RESET must be held low for at least 3 µs. The MDP is ready to use 400 ms after the low-to-high transition of ~RESET. ~RES1 and ~RES2 are typically connected to the MCU ~RESET input and to the host bus ~RESET (or RESET through an inverter) line (parallel host) or reset circuit (serial DTE interface) which resets both the MCU and MDP upon power turn-on. ~RES1 and ~RES2 have active internal pull-up resistors.                      |

| ~WKRES                          | IA                               | Wake-up Reset. ~WKRES is connected internally to ~RESET but will not drive the MDP ~RESET pins.  Asserting ~WKRES performs the same reset function as the MDP ~RESET and typically used by the MCU to wake up the MDP from SLEEP Mode when the MDP ~RESET lines cannot be asserted (because they are also connected to the MCU ~RESET input). For a serial DTE or parallel host MCU configuration, connect ~WKRES to the MCU ~WKRESOUT output. ~WKRES has an active internal pull-up resistor.                                                                                                                                   |

| VDD                             | PWR                              | +3.3V Digital Circuit Power Supply. Connect to +3.3V through digital circuit power supply filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AVDD                            | PWR                              | +3.3V Analog Circuit Digital Power Supply. Connect to +3.3V through digital circuit power supply filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AVAA                            | PWR                              | Analog Circuit Analog Power Supply. Connect to +5V through analog circuit power supply filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VGG                             | REF                              | Input Reference Voltage. Reference voltage for +5V tolerant input pins. Connect to +5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GND                             | GND                              | Digital Ground. Connect to digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AGND                            | GND                              | Analog Ground. Connect to analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| XCLK                            | OA                               | X Clock. Output clock at 56.448 MHz (PLL disabled) or 63.5045 (PLL enabled), which runs during MDP Normal Mode and is turned off during Sleep Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| YCLK                            | OA                               | Y Clock. Output clock at 28.224 MHz, which runs during MDP Normal Mode and is turned off during Sleep Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SYCLK                           | OA                               | System Clock. Output clock at 28.224 MHz, which runs during MDP Normal Mode and during Sleep Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PLLVDD                          | PLL                              | <b>PLLVDD Connection.</b> Connect to +3.3V (VDD) through 10 $\Omega$ and to DGND through 10 (+) μF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PLLGND                          | PLL                              | PLLGND Connection. Connect to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                 |                                  | PARALLEL HOST INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| addition of ext<br>68000. The m | ernal logic, th<br>icroprocessor | interrupt hardware interface signals allow MDP connection to an 8086-compatible microprocessor bus. With the e interface can be made compatible with a wide variety of other microprocessors such as the 6502, 8086 or interface allows a microprocessor to change MDP configuration, read or write channel and diagnostic data, and y writing control bits and reading status bits.                                                                                                                                                                                                                                             |

| D0-D7                           | IA/OB                            | Data Lines. Eight bidirectional data lines (D0–D7) provide parallel transfer of data between the host and the MDP. The most significant bit is D7. Data direction is controlled by the Read Enable and Write Enable signals.                                                                                                                                                                                                                                                                                                                                                                                                     |

| RS0-RS4                         | IA                               | Register Select Lines. The five active high register select lines (RS0–RS4) address interface memory registers within the MDP interface memory. These lines are typically connected to the five least significant lines (A0–A4) of the address bus.  The MDP decodes RS0 through RS4 to address one of 32 internal interface memory registers (00–1F). The most significant address bit is RS4, while the least significant address bit is RS0. The selected register can be read from or written into via the 8-bit parallel data bus (D0–D7). The most significant data bit is D7, while the least significant data bit is D0. |

| ~CS                             | IA                               | <b>Chip Select.</b> ~CS selects the MDP for microprocessor bus operation. ~CS is typically generated by decoding host address bus lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ~READ                           | IA                               | <b>Read Enable.</b> During a read cycle (~READ asserted), data from the selected interface memory register is gated onto the data bus by means of three-state drivers in the MDP. These drivers force the data lines high for a one bit, or low for a zero bit. When not being read, the three-state drivers assume their high-impedance (off) state.                                                                                                                                                                                                                                                                            |

| ~WRITE                          | IA                               | <b>Write Enable.</b> During a write cycle (~WRITE asserted), data from the data bus is copied into the selected MDP interface memory register, with high and low bus levels representing one and zero bit states, respectively.                                                                                                                                                                                                                                                                                                                                                                                                  |

| IRQ                             | OA                               | Interrupt Request. The MDP IRQ output may be connected to the host processor interrupt request input in order to interrupt host program execution for immediate MDP service. The IRQ output can be enabled in the MDP interface memory to indicate immediate change of conditions. The use of IRQ is optional depending upon MDP application. The IRQ output is driven by a TTL-compatible CMOS driver.                                                                                                                                                                                                                          |

Table 5. MDP Signal Definitions (Cont'd)

| Label           | I/O Type       | Signal Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | •              | DTE SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| short wire leng | oths and circu | tatus signals provide a V.24-compatible serial interface. These signals are TTL compatible in order to drive the its normally found within a printed circuit board, stand-alone modem enclosures, or equipment cabinets. For signals can be easily converted to EIA/RS-232-D voltage levels.                                                                                                                                                                                                             |

| TXD             | IA             | <b>Transmitted Data.</b> The MDP obtains serial data to be transmitted from the local DTE on the Transmitted Data (TXD) input.                                                                                                                                                                                                                                                                                                                                                                           |

| RXD             | OA             | Received Data. The MDP presents received serial data to the local DTE on the Received Data (RXD) output.                                                                                                                                                                                                                                                                                                                                                                                                 |

| ~RTS            | IA             | Request to Send. Activating ~RTS causes the MDP to transmit data on TXD when ~CTS becomes active. The ~RTS pin is logically ORed with the RTS bit.                                                                                                                                                                                                                                                                                                                                                       |

| ~CTS            | OA             | Clear To Send. ~CTS active indicates to the local DTE that the MDP will transmit any data present on TXD. CTS response times from an active condition of RTS are shown in Table 3.                                                                                                                                                                                                                                                                                                                       |

| ~RLSD           | OA             | Received Line Signal Detector. ~RLSD active indicates to the local DTE that energy above the receive level threshold is present on the receiver input, and that the energy is not a training sequence.                                                                                                                                                                                                                                                                                                   |

|                 |                | One of four ~RLSD receive level threshold options can be selected (RTH bits). A minimum hysteresis action of 2 dB exists between the actual off-to-on and on-to-off transition levels. The threshold level and hysteresis action are measured with a modulated signal applied to the Receiver Analog (RXA) input. Note that performance may be degraded when the received signal level is less than -43 dBm. The ~RLSD on and off thresholds are host programmable in DSP RAM.                           |

| ~DTR            | IA             | <b>Data Terminal Ready.</b> In V.8, V.90, K56flex, V.34, V.32 bis, V.32, V.22 bis, V.22, or Bell 212A configuration, activating ~DTR initiates the handshake sequence. The DATA bit must be set to complete the handshake. In V.21, V.23, or Bell 103 configuration, activating ~DTR causes the MDP to enter the data state provided that the DATA bit is a 1. If in answer mode, the MDP immediately sends answer tone. In these modes, if controlled carrier is enabled, carrier is controlled by RTS. |

|                 |                | During the data mode, deactivating ~DTR causes the transmitter and receiver to turn off and return to the idle state.                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |                | The ~DTR input and the DTR control bit are logically ORed.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ~DSR            | OA             | <b>Data Set Ready.</b> ~DSR ON indicates that the MDP is in the data transfer state. ~DSR OFF indicates that the DTE is to disregard all signals appearing on the interchange circuits except Ring Indicator (~RI). ~DSR is OFF when the MDP is in a test mode (i.e., local analog or remote digital loopback).                                                                                                                                                                                          |

|                 |                | The DSR status bit reflects the state of the ~DSR output.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ~RI             | OA             | <b>Ring Indicator.</b> ~RI output follows the ringing signal present on the line with a low level (0 V) during the ON time, and a high level during the OFF time coincident with the ringing signal. The RI status bit reflects the state of the ~RI output.                                                                                                                                                                                                                                             |

| TDCLK           | OA             | <b>Transmit Data Clock.</b> The MDP outputs a synchronous Transmit Data Clock (TDCLK) for USRT timing. The TDCLK frequency is the data rate (±0.01%) with a duty cycle of 50±1%. The TDCLK source can be internal, external (input on XTCLK), or slave (to ~RDCLK) as selected by TXCLK bits in interface memory.                                                                                                                                                                                        |

| XTCLK           | IA             | <b>External Transmit Clock.</b> In synchronous communication, an external transmit data clock can be connected to the MDP XTCLK input. The clock supplied at XTCLK must exhibit the same characteristics as TDCLK. The XTCLK input is then reflected at the TDCLK output.                                                                                                                                                                                                                                |

| ~RDCLK          | OA             | Receive Data Clock. The MDP outputs a synchronous Receive Data Clock (~RDCLK) for USRT timing. The ~RDCLK frequency is the data rate (±0.01%) with a duty cycle of 50±1%. The ~RDCLK low-to-high transitions coincide with the center of the received data bits.                                                                                                                                                                                                                                         |

Table 5. MDP Signal Definitions (Cont'd)

| Label                        | I/O Type | Signal Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|