### **Applications**

- □ Bluetooth<sup>tm</sup> Class 1

- □ USB Dongles

- □ Laptops

- Access Points

- Cordless Piconets

- ☐ Flip chip and chip-on-board applications

#### **Features**

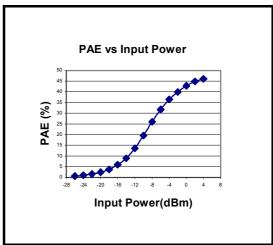

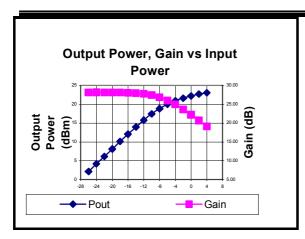

- □ +22.5 dBm at 47% Power Added Efficiency

- ☐ Low current 80 mA typical @ Pout=+20 dBm

- ☐ Temperature stability better than 1dB

- Power-control and Power-down modes

- □ -40C to +85C temperature range

- ☐ Gold bump bare die (0.63mm x 0.96mm)

#### **Ordering Information**

| Part       | Package            | Shipping<br>Method         |  |  |  |

|------------|--------------------|----------------------------|--|--|--|

| PA2423G    | Gold bump bare die | Diced wafer<br>Waffle pack |  |  |  |

| PA2423G-EV | Evaluation kit     |                            |  |  |  |

### **Product Description**

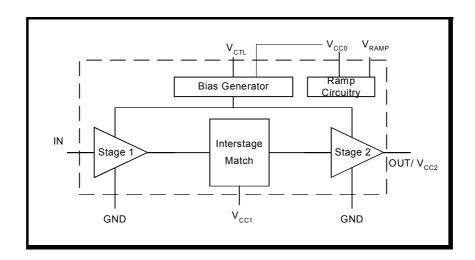

A monolithic, high-efficiency, silicon-germanium power amplifier IC, the PA2423G is designed for Class 1 Bluetooth<sup>tm</sup> 2.4 GHz radio applications. It delivers +22.5 dBm output power with 47% power-added efficiency – making it capable of overcoming insertion losses of up to 2.5 dB between amplifier output and antenna input in Class 1 Bluetooth<sup>tm</sup> applications.

The amplifier features:

- an analog control input for improving PAE at reduced output power levels;

- a digital control input for controlling power up and power down modes of operation.

An on-chip ramping circuit corrects the turn-on/off switching of amplifier output with less than 3 dB overshoot, meeting the Bluetooth tm specification 1.1.

The PA2423G operates at 3.3V DC. At typical output power level (+22.5 dBm), its current consumption is 120 mA.

The silicon/silicon-germanium structure of the PA2423G provides high thermal conductivity and a subsequently low junction temperature. This device is capable of operating at a duty cycle of 100 percent.

#### **Functional Block Diagram**

## **Pad Description**

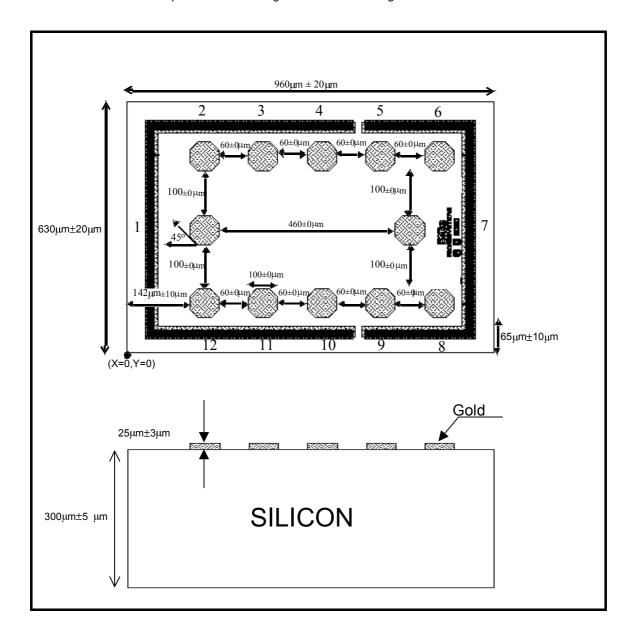

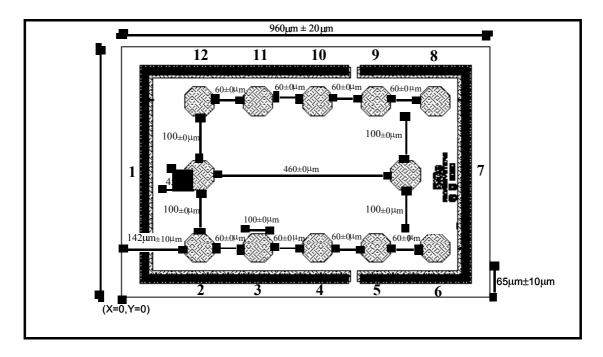

For reference of pad numbers to the package drawings, see pages 4 and 5.

| Number | Name     | Description                                   | Pad Coordinate, Center of Pad<br>(lower left corner is (0.0)) |

|--------|----------|-----------------------------------------------|---------------------------------------------------------------|

| 1      | IN       | PA input                                      | X = 192μm ± 10μm, Y = 315μm ± 10μm                            |

| 2      | VRAMP    | PA enable/disable control input               | X = 192μm ± 10μm, Y = 515μm ± 10μm                            |

| 3      | GND1     | Ground                                        | X = 352μm ± 10μm, Y = 515μm ± 10μm                            |

| 4      | VCTL     | Output power level control                    | X = 512μm ± 10μm, Y = 515μm ± 10μm                            |

| 5      | GND2     | Ground                                        | X = 672μm ± 10μm, Y = 515μm ± 10μm                            |

| 6      | GND3     | Ground                                        | X = 832μm ± 10μm, Y = 515μm ± 10μm                            |

| 7      | OUT/VCC2 | PA output and stage2 collector supply voltage | X = 752μm ± 10μm, Y = 315μm ± 10μm                            |

| 8      | GND4     | Ground                                        | X = 832μm ± 10μm, Y = 115μm ± 10μm                            |

| 9      | GND5     | Ground                                        | X = 672μm ± 10μm, Y = 115μm ± 10μm                            |

| 10     | VCC1     | Stage1 collector supply voltage               | X = 512μm ± 10μm, Y = 115μm ± 10μm                            |

| 11     | GND6     | Ground                                        | X = 352μm ± 10μm, Y = 115μm ± 10μm                            |

| 12     | VCC0     | Ramp supply voltage                           | X = 192μm ± 10μm, Y = 115μm ± 10μm                            |

## **Absolute Maximum Ratings**

| Symbol | Parameter                    | Min. | Max.            | Unit |

|--------|------------------------------|------|-----------------|------|

| Vcc    | Supply Voltage               | -0.3 | +3.6            | V    |

| VCTL   | Control Voltage              | -0.3 | V <sub>CC</sub> | V    |

| VRAMP  | Ramping Voltage              | -0.3 | V <sub>CC</sub> | V    |

| IN     | RF Input Power               |      | +8              | dBm  |

| TA     | Operating Temperature Range  |      | +85             | °C   |

| TSTG   | Storage Temperature Range    |      | +150            | ∘С   |

| Tj     | Maximum Junction Temperature |      | +150            | °C   |

Operation in excess of any one of the above Absolute Maximum Ratings may result in permanent damage. This device is a high performance RF integrated circuit with EST rating < 600V and is ESD sensitive. Handling and assembly of this device should be at ESD protected workstations.

#### **DC Electrical Characteristics**

Conditions:  $V_{CC0} = V_{CC1} = V_{CC2} = V_{RAMP} = 3.3V$ ,  $V_{CTL} = 3.3V$ ,  $P_{IN} = +2dBm$ ,  $TA = 25^{\circ}C$ , f = 2.45GHz,

Input and Output externally matched to  $50\Omega$  unless otherwise noted.

| Symbol                 | Note | Parameter                                                      | Min. | Тур. | Max. | Unit |

|------------------------|------|----------------------------------------------------------------|------|------|------|------|

| Vcc                    |      | Supply Voltage                                                 | 3.0  | 3.3  | 3.6  | V    |

| lcc                    | 1    | Supply Current (Icc = Ivcc0 + Ivcc1 + Ivcc2)                   |      | 120  | 150  | mA   |

| $\Delta$ ICC $_{temp}$ | 3    | Supply Current variation over temperature, (-40°C < Ta <+85°C) |      | 25   |      | %    |

| Vctl                   |      | PA Output Power Control Voltage Range                          | 0    |      | Vcc  | V    |

| ICTL                   | 1    | Current sourced by VcTL Pin                                    |      | 200  | 250  | μΑ   |

| Vramp —                | 3    | Logic High Voltage                                             | 2.0  |      |      | ٧    |

|                        | 3    | Logic Low Voltage                                              |      |      | 0.8  | ٧    |

| I <sub>stby</sub>      | 1    | Leakage Current when VRAMP = 0V                                |      | 0.5  | 10   | μΑ   |

#### **AC Electrical Characteristics**

$Conditions: V_{CC0} = V_{CC1} = V_{CC2} = V_{RAMP} = 3.3V, V_{CTL} = 3.3V, P_{IN} = +2 \text{ dBm}, T_A = 25^{\circ}\text{C}, f = 2.45\text{GHz}, T_{CC1} = 1.45 \text{ GHz}, T_{CC2} = 1.45 \text{$

Input and Output externally matched to  $50\Omega$ , unless otherwise noted

| Symbol                     | Note | Parameter                                                                                                               | Min                                                    | Тур. | Мах  | Unit |

|----------------------------|------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------|------|------|

| <u> </u>                   |      |                                                                                                                         | •                                                      |      |      |      |

| fL-U                       | 3    | Frequency Range                                                                                                         | 240<br>0                                               |      | 2500 | MHz  |

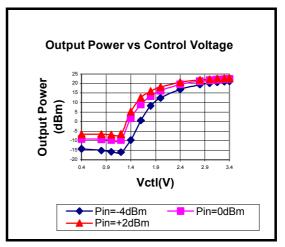

| Роит                       | 1    | Output Power @ PiN =+2 dBm,VcTL = 3.3V                                                                                  | 20.0                                                   | 22.5 | 23.5 | dBm  |

|                            | 1    | Output Power @ Pin =+2 dBm,VcTL =0.4V                                                                                   |                                                        | -8   | 0    | dBm  |

| $\Delta$ P <sub>TEMP</sub> | 3    | Pout variation over temperature (-40°C <ta <+85°c),="" vctl="3.3V&lt;/td"><td></td><td>1</td><td>2</td><td>dB</td></ta> |                                                        | 1    | 2    | dB   |

| dP out /dVctL              | 3    | Control Voltage Sensitivity                                                                                             |                                                        | 60   | 120  | dBmV |

| PAE                        |      | Power Added Efficiency at +22.5 dBm Output Power                                                                        |                                                        | 47   |      | %    |

| Gvar                       | 3    | Gain Variation over band (2400-2500 MHz)                                                                                |                                                        | 0.7  | 1    | dB   |

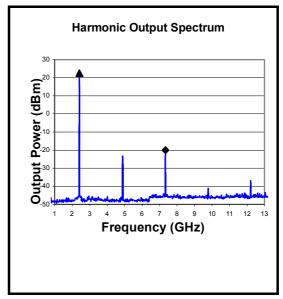

| 2f, 3f, 4f, 5f             | 3,4  | Harmonics                                                                                                               |                                                        | -35  | -30  | dBc  |

| IS21loff                   | 2    | Isolation in "OFF" State, PIN =+2dBm,VRAMP =0V                                                                          | 20                                                     | 25   |      | dB   |

| IS12 I                     | 2    | Reverse Isolation                                                                                                       | 32                                                     | 42   |      | dB   |

| STAB                       | 2    | Stability (PIN = +2dBm, Load VSWR = 6:1)                                                                                | All non-harmonically related outputs less than -50 dBc |      |      |      |

**Notes:** (1) Guaranteed by production test at TA =25°C.

- (2) Guaranteed by design only.

- (3) Guaranteed by design and characterization.

- (4) Harmonic levels are greatly affected by topology of external matching networks.

- (5) RF characteristics specified above are for direct die attach (Flip-chip) on SiGe Applications Board. For wire bonded applications there may be some degradation in performance due to effects of bond wires and interconnect.

# Gold Bump Bare Die - Top and Side Views

The first drawing provides the top view of the gold bump bare die (gold bumps on top surface). This view should be used for the chip-on-board mounting. The second drawing illustrates the side view of the die.

# Gold Bump Bare Die - Bottom View

This drawing shows the gold bump bare die when viewed from the bottom of the die (without gold bumps). This view and pintout orientation should be used for flip chip mounting – top surface of die (with gold bumps) is inverted to make contact with PCB.

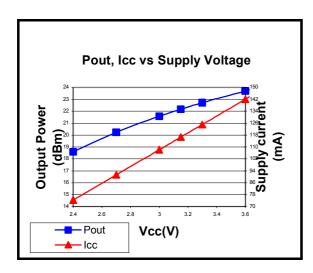

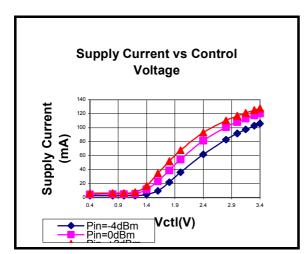

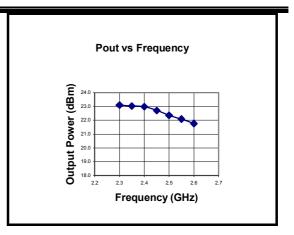

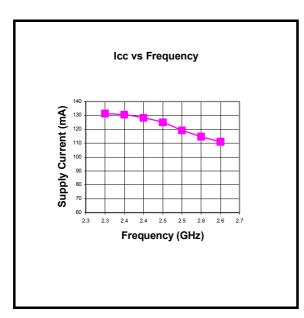

## **Typical Performance Characteristics**

SiGe PA2423G-EV evaluation board,  $V_{CC0}=V_{CC1}=V_{CC2}=V_{RAMP}=3.3V$ ,  $V_{CTL}=3.3V$ ,  $P_{IN}=+2$  dBm,  $T_A=25^{\circ}C$ , f=2.45GHz, Input and Output externally matched to  $50\Omega$ , unless otherwise noted)

#### **Applications Information**

For test and design purposes, SiGe Semiconductor offers an evaluation board for the PA2423G. The order part number is PA2423G-EV. The evaluation board is intended to simplify the testing with respect to RF performance of this power amplifier.

The application note, 05AN007 provides the supporting information for using the evaluation board. It contains information on the schematic, bill of materials and recommended layout for the power amplifier and the input and output matching networks. To assist in the design process, this layout is available, upon request, in gerber file format.

## Using V<sub>RAMP</sub>

$V_{RAMP}$  is a digital pin used to power-up and power-down the PA2423G in Time Duplex systems such as  $Bluetooth^{tm}$  1.1. During receive mode,  $V_{RAMP}$  voltage is pulled down, PA2423G acts as a 25 dB isolation block between the radio and the antenna while consuming a modest 1uA. In transmit mode,  $V_{RAMP}$  voltage is pulled to VCC and PA2423G offers 19 dB to 21dB of large signal gain. The rise and fall time are in the order of 1-2usec.

#### Using V<sub>CTL</sub>

$V_{CTL}$  is an analog pin that is designed to control the gain of PA2423G. Applying a voltage between 0V and Vcc will adjust the gain between -15dB and 21 dB. Used in combination with a variable drive level to PA2423G, the  $V_{CTL}$  function can greatly optimize the PAE of the system at all four Bluetooth<sup>tm</sup> transmitted power levels.

By applying approximately 1.4V to V<sub>CTL</sub>, for example, a Class1 radio can be modified to a Class2 radio with the PA2423G consuming only 15mA.

By implementing a resistor DAC, the  $V_{\text{CTL}}$  pin can interface with  $\mathrm{Bluetooth}^{tm}$  transceivers offering digital and programmable outputs.

#### http://www.sige.com

Headquarters: Canada

Phone: +1 613 820 9244

Fax: +1 613 820 4933

2680 Queensview Drive

Ottawa ON K2B 8J9 Canada sales@sige.com

U.S.A. United Kingdom

19925 Stevens Creek Blvd. 1010 Cambourne Business Park

Suite 135 Cambourne

Cupertino, CA 95014-2358 Cambridge CB3 6DP

Phone: +1 408 973 7835 Phone: +44 1223 598 444 Fax: +1 408 973 7235 Fax: +44 1223 598 035

Information furnished is believed to be accurate and reliable and is provided on an "as is" basis. SiGe Semiconductor Inc. assumes no responsibility or liability for the direct or indirect consequences of use of such information nor for any infringement of patents or other rights of third parties, which may result from its use. No license or indemnity is granted by implication or otherwise under any patent or other intellectual property rights of SiGe Semiconductor Inc. or third parties. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SiGe Semiconductor Inc. products are NOT authorized for use in implantation or life support applications or systems without express written approval from SiGe Semiconductor Inc.

The Bluetooth trademarks are owned by Bluetooth SIG Inc., USA.

Copyright 2001 SiGe Semiconductor All Rights Reserved