# PT502P01/PT500GA1 GATE ARRAY

TECHNICAL REFERENCE

#### **PREFACE**

This reference manual contains the specifications and functional descriptions of the chip set (the PT502P01 CPU and PT500GA1 Gate Array) that controls the LTP5000 series line thermal printers. It is recommended that the user thoroughly read this manual to become familiar with the equipment prior to use.

Fully investigate the industrial proprietary rights of the sample circuits described in this manual before using.

#### **CHAPTER 1**

#### **FEATURES**

The PT502P01 CPU and PT500GA1 Gate Array form a chip set that serves the intended purposes only when they are used as a pair.

The PT502P01 CPU and PT500GA1 Gate Array chip set:

- Achieves printing with less current by using division control according to the number of dots to be activated.

- Accepts both parallel and serial input.

- Drives the motor using two power supplies to avoid overheating the motor.

- Measures the thermal head resistance and automatically adjusts the energy used for printing.

- Provides high quality printing by automatically adjusting the print density according to the temperature and voltage.

- Detects abnormal head resistance, voltage, temperature, etc.

- Provides various character functions, including double-width/double-height, reverse printing, underlining, and character spacing control.

- Permits superimposing of character data and bit image data.

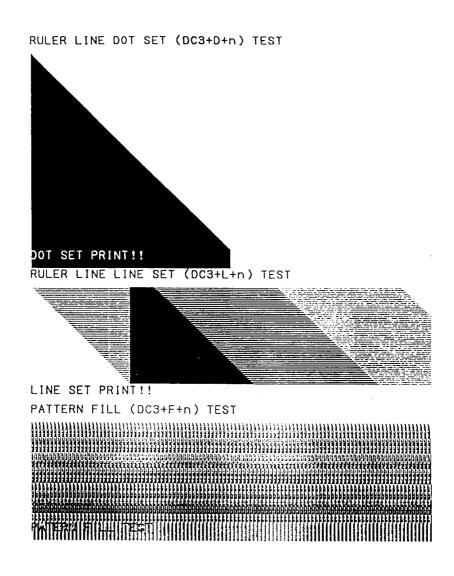

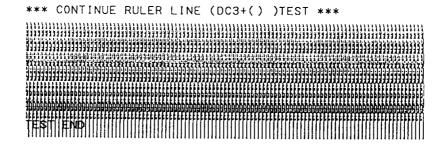

- Provides a ruler line function which allows ruler lines and characters to be easily overlaid.

- Provides a selection of two print speeds.

- Makes the control circuit compact by integrating peripheral ICs into the gate array.

- Supports printing on two-ply thermal paper.

- Loads paper automatically using the autoloading function.

- Cuts paper fully or partially using the autocutter unit control function.

#### **CHAPTER 2**

#### **GENERAL SPECIFICATIONS**

This chapter provides the general specifications for the PT502P01 and PT500GA1. For detailed information, refer to Chapters 4 and 9.

#### 2.1 TYPE AND DIMENSIONS

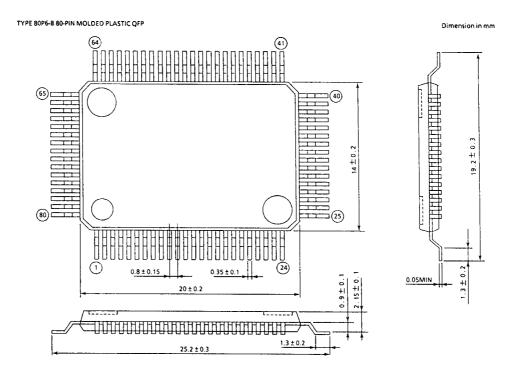

PT502P01 :80-pin flat package, 25.2 mm (W)  $\times$  19.2 mm (D)  $\times$  2.15 mm (H)

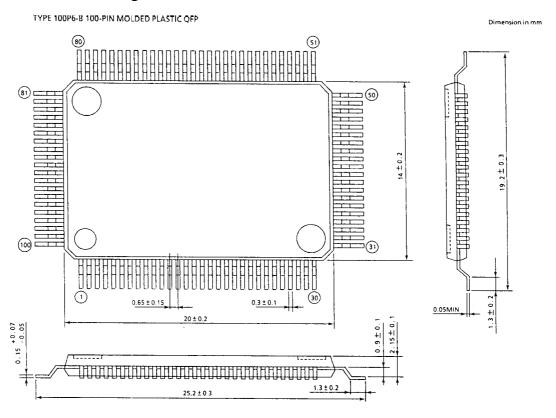

PT500GA1 :100-pin flat package, 25.2 mm (W)  $\times$  19.2 mm (D)  $\times$  2.15 mm (H)

# 2.2 STRUCTURE

**C-MOS LSI**

# 2.3 DATA TRANSMISSION

Parallel and serial data transmission modes are available.

Parallel :8-bit parallel, modified Centronics

Asynchronous serial :150, 300, 600, 1200, 2400, 4800, 9600, 19200 bps

selectable

# 2.4 PRINT FUNCTIONS

Applicable models :Six LTP5000 series models selectable

Print method :Thermal line dot method

For number of dots/characters per line, maximum print speed and print

resolution, see Table 2-1.

Table 2-1 Number of Dots/Characters per Line, Print Speed and Print Resolution

| Model   | Number of<br>Dots per<br>Line | Number of<br>Characters<br>per Line <sup>1</sup> | Maximum Print<br>Speed (mm/sec) | Print Resolution<br>(dot/mm) |

|---------|-------------------------------|--------------------------------------------------|---------------------------------|------------------------------|

| LTP5242 | 448                           | 28                                               | 50                              | 8                            |

| LTP5246 | 448                           | 28                                               | 25                              | 8                            |

| LTP5347 | 576                           | 36                                               | 50                              | 8                            |

| LTP5437 | 640                           | 40                                               | 50                              | 6                            |

| LTP5442 | 832                           | 52                                               | 50                              | 8                            |

| LTP5446 | 832                           | 52                                               | 25                              | 8                            |

When character spacing is 4 dots.

Available character types : IBM compatible character set and Japanese kana

character set (348 characters total)

Setting can be changed using the 24 (V)  $\times$  12 (H)

dot matrix function pin or function code

Line spacing :16 dot lines (programmable)

Character spacing :4 dots (programmable)

## 2.5 CONTROL FUNCTIONS

- Paper feed in forward or reverse direction (switch-selectable)

- Automatic measurement of thermal head resistance

- Automatic adjustment of energy applied to the thermal head

- Thermal head position and paper detection

- Emergency stop at abnormal temperatures or voltages

- Test print and HEX dump

- Selection using function codes :Interface mode 0 and 1

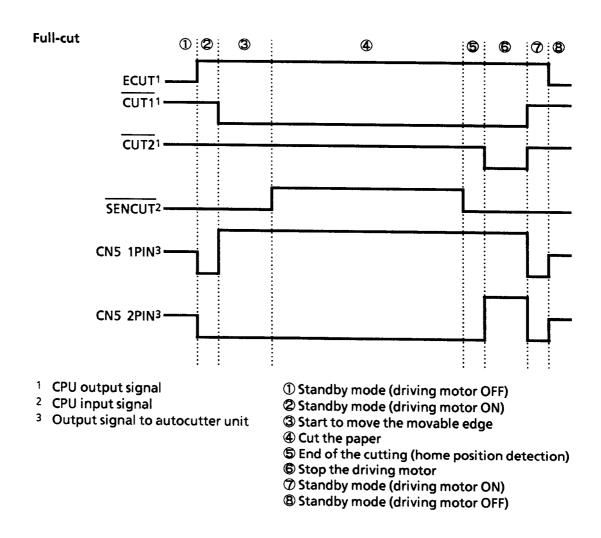

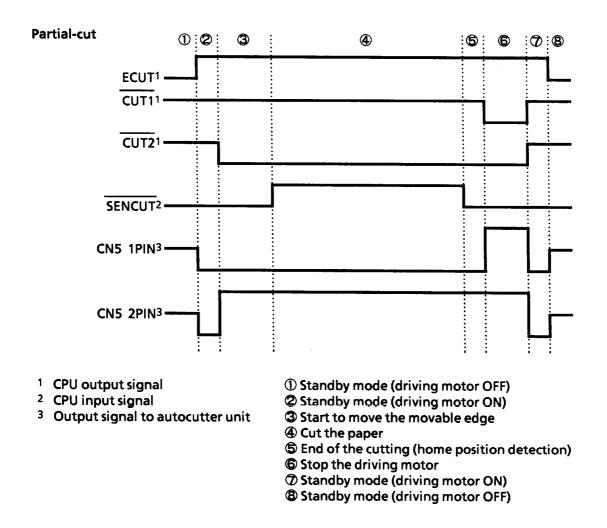

- Two selectable cutting modes :full cut and partial cut using function codes

ESC + i and ESC + m

# 2.6 OPERATING VOLTAGE

5 V ± 5% DC

# 2.7 OPERATING FREQUENCY

16 MHz ± 0.5%

# 2.8 CURRENT CONSUMPTION ( $V_{CC} = 5 \text{ V, STANDBY MODE}$ )

PT502P01 :24 mA maximum PT500GA1 :5 mA maximum

#### **CHAPTER 3**

#### **CONTROL FUNCTIONS**

## 3.1 THERMAL HEAD DRIVE OPERATION

Generally, when the line thermal head is operating, it is divided into several blocks which are activated one after another in succession. As a result, the number of simultaneously activated dots decreases, thus reducing the needed current capacity of the power supply.

For the line thermal head of an LTP5000 series printer mechanism, one line is divided into 3 to 6 blocks called physical blocks. A strobe signal is allocated to each physical block to activate it. To actually drive the head, physical blocks are activated in groups. The group of physical blocks is called a logical block.

For the PT502P01/PT500GA1, either dynamic division or fixed division can be selected as the method of division for driving the head. The selection is made through a function pin (pin 43 on the PT500GA1).

# (1) Dynamic division

The CPU counts the number of dots activated in each physical block and groups the physical blocks into logical blocks so that the number does not exceed the specified maximum number of activated dots. The maximum number of activated dots is specified in units of 64 dots by pins 39, 41, and 42 on the PT500GA1. The CPU determines logical blocks each time it prints a single dot line.

When the maximum number of activated dots is smaller than the number of dots in the largest physical block (128 to 192 dots), the way the PT502P01 drives the thermal head differs depending on the interface mode, mode 0 or mode 1, specified by pins 37 and 38 on the PT500GA1. The way the PT502P01 drives the thermal head in each interface mode is described in the following paragraphs.

In interface mode 0, the maximum number of activated dots is always the value set on the PT500GA1. However, because the largest physical block is 128 to 192 dots, if the maximum number of activated dots is set to a value smaller than the number of dots in the largest physical block, a single line of data must be divided and sent to the thermal head in multiple transmissions, until all data is printed. This method of data transfer (hereafter called "data masking transfer") is performed automatically by internal software. Table 3-1 indicates the conditions in which data masking transfer occurs.

Table 3-1 Conditions in Which Data MaskingTransfer Occurs

| Specified<br>Dot Count | PT50<br>Pin<br>39 | 00GA<br>Nos<br>41 |      | LTP5242 | LTP5246 | LTP5347 | LTP5437 | LTP5442 | LTP5446 |

|------------------------|-------------------|-------------------|------|---------|---------|---------|---------|---------|---------|

| 64                     | Low L             | -ow               | Low  | 0       | 0       | 0       | 0       | 0       | 0       |

| 128                    | Low L             | -ow               | High | 0       | 0       |         |         | 0       | 0       |

| 192                    | Low F             | ligh              | Low  |         |         |         |         |         |         |

| 256                    | Low H             | ligh              | High |         |         |         |         |         |         |

| 320                    | High I            | Low               | Low  |         |         |         |         |         |         |

| 384                    | High I            | Low               | High |         |         |         |         |         |         |

| 448                    | High H            | ligh              | Low  |         |         |         |         |         |         |

| 512                    | High H            | ligh              | High |         |         |         |         |         |         |

O indicates when data masking transfer occurs.

Figure 3-1 shows how the dots are activated by data masking transfer, when the maximum number of activated dots on the LTP5242 is specified as 64 and when all dots are activated.

| 1st PHYSICAL BLOCK<br>(192 DOTS) | 2nd PHYSICAL BLOCK<br>(128 DOTS) | 3rd PHYSICAL BLOCK<br>(128 DOTS) |

|----------------------------------|----------------------------------|----------------------------------|

| 64 64 64                         | 64 64                            | 64 64 (DOTS)                     |

| !                                | 1                                | 1st ACTIVATION                   |

|                                  |                                  | 2nd                              |

| i                                |                                  | 3rd                              |

|                                  |                                  | 4th                              |

| <u> </u>                         |                                  | 5th                              |

|                                  |                                  | 6th                              |

|                                  |                                  | 7th                              |

SHADED AREA = ACTIVATED DOTS

Figure 3-1 Data Masking Transfer When All Dots are Activated on the LTP5242 (Maximum Number of Activated Dots = 64)

When the maximum number of activated dots is equal to or more than the number of dots in the largest physical block, print data is transferred to the thermal head at one time and dots are activated in logical blocks. Figure 3-2 shows how the dots are activated by dynamic division when the maximum number of activated dots on the LTP5242 is specified as 192 and when all dots are activated.

| 1st PHYSICAL BLOCK<br>(192 DOTS) | 2nd PHYSICAL BLOCK<br>(128 DOTS) | 3rd PHYSICAL<br>(128 DOT |                |

|----------------------------------|----------------------------------|--------------------------|----------------|

|                                  |                                  |                          | 1st ACTIVATION |

|                                  |                                  |                          | 2nd            |

|                                  |                                  |                          | 3rd            |

| SHADED AREA = AC                 | TIVATED DOTS                     |                          |                |

Figure 3-2 Dynamic Division When All Dots are Activated on the LTP5242 (Maximum Number of Activated Dots = 192)

Because faster print speed is given priority in interface mode 1, if the specified maximum number of activated dots is smaller than the number of dots in the largest physical block on the thermal head, the maximum number of activated dots us rounded up to the number of dots in the largest physical block.

Print data is transferred to the thermal head at one time and dots are activated in physical blocks.

Table 3-2 shows the maximum number of dots actually activated simultaneously in mode 1.

Table 3-2 Maximum Number of Activated Dots for Dynamic Division in Mode 1

| Specified PT500GA1 Pin Nos. |      | Physical Block<br>( = Maximum Number of Activated Dots) |      |         |         |         |         |         |         |

|-----------------------------|------|---------------------------------------------------------|------|---------|---------|---------|---------|---------|---------|

|                             | 39   | 41                                                      | 42   | LTP5242 | LTP5246 | LTP5347 | LTP5437 | LTP5442 | LTP5446 |

| 64                          | Low  | Low                                                     | Low  | 192     | 192     | 128     | 128     | 160     | 160     |

| 128                         | Low  | Low                                                     | High | 192     | 192     | 128     | 128     | 160     | 160     |

| 192                         | Low  | High                                                    | Low  | 192     | 192     | 192     | 192     | 192     | 192     |

| 256                         | Low  | High                                                    | High | 256     | 256     | 256     | 256     | 256     | 256     |

| 320                         | High | Low                                                     | Low  | 320     | 320     | 320     | 320     | 320     | 320     |

| 384                         | High | Low                                                     | High | 384     | 384     | 384     | 384     | 384     | 384     |

| 448                         | High | High                                                    | Low  | 448     | 448     | 448     | 448     | 448     | 448     |

| 512                         | High | High                                                    | High | 448     | 448     | 512     | 512     | 512     | 512     |

The advantage of dynamic division is that the maximum number of activated dots can be specified according to the capacity of the power supply used. The printer can be operated with a small capacity power supply when the maximum number of activated dots is small. However, this process may increase the number of divisions and may lower print speed, depending on the content of the print data. This becomes obvious especially for block transfer. On the other hand, printing speed becomes faster when the maximum number of activated dots is larger, which, however, requires a larger power supply capacity.

#### NOTE

To maintain high print quality when printing ruler lines or bit images, set the maximum number of activated dots to a value at which block transfer will not be performed. Also, avoid block transfer when using two-ply thermal paper, otherwise the paper may stick to the thermal head.

# (2) Fixed division

For each printer model, the physical blocks which compose a logical block are determined beforehand. Fixed division always activates physical blocks in the same order, thereby realizing higher print quality.

For the fixed division method, the number of logical blocks are determined as shown in Table 3-3.

Table 3-3 Number of Logical Blocks When the Fixed Division is Selected

| Model   | Number of Logical Blocks |                    |  |  |  |

|---------|--------------------------|--------------------|--|--|--|

| Model   | High Printing Speed      | Low Printing Speed |  |  |  |

| LTP5242 | 2                        | 3                  |  |  |  |

| LTP5246 | 2                        | 3                  |  |  |  |

| LTP5347 | 2                        | 5                  |  |  |  |

| LTP5437 | 2                        | 5                  |  |  |  |

| LTP5442 | 2                        | 4                  |  |  |  |

| LTP5446 | 2                        | 3                  |  |  |  |

Note that it is impossible to print on two-ply thermal paper when using fixed division.

#### 3.2 MOTOR DRIVE METHOD

The PT502P01 CPU and PT500GA1 Gate Array have a dual-source motor drive feature and a feature that drives the motor by 2-2 phase excitation. One motor drive step pulse causes the printer mechanism to feed one dot line.

The PT502P01 and PT500GA1 employ a dual-source (Vp and Vcc) motor drive method to minimize the motor torque loss caused by the generation of heat from the motor when the printer mechanism is run in low-speed print mode. Even when the printer mechanism is to be used in high-speed print mode, it is recommended that a dual-source power supply be used since the motor will generate excessive heat, reducing the motor torque, if the speed of data input is too slow.

When the motor is started in the high speed printing mode, the motor accelerates while printing is performed to keep print quality uniform. The number of acceleration steps for the LTP5000 series printer mechanisms are listed in Table 3-4. The PT502P01 and PT500GA1 do not accelerate the motor when printing in low-speed mode.

See Section 4.11 for a sample motor control circuit. Refer also to the Technical Reference manual for the individual printer mechanism.

Table 3-4 Number of Acceleration Steps

| Model   | Maximum<br>Printing Speed | Number of Acceleration Steps |

|---------|---------------------------|------------------------------|

| LTP5242 | 400 pps                   | 8                            |

| LTP5246 | 200 pps                   | 4                            |

| LTP5347 | 400 pps                   | 8                            |

| LTP5437 | 300 pps                   | 4                            |

| LTP5442 | 400 pps                   | 8                            |

| LTP5446 | 200 pps                   | 4                            |

# 3.3 ADJUSTMENT OF ENERGY APPLIED TO THE THERMAL HEAD

The PT502P01 and PT500GA1 automatically control the print pulse width so that the print density remains constant regardless of possible changes in head resistance, head temperature, and power supply voltage (V<sub>P</sub>).

See Section 4.15 for the procedure on how to adjust thermal head energy. Refer also to the Technical Reference manual for the individual printer mechanism.

#### 3.4 PRINTING ON TWO-PLY THERMAL PAPER

# What is two-ply thermal paper?

A sheet of two-ply thermal paper consists of a sheet of low-sensitivity thermal paper on top of a sheet of high-sensitivity thermal paper thereby providing two copies simultaneously during one printing operation. It can be used for printing receipts, for example, where the printed result is given to the client while the copy is retained.

# Printing on Two-ply Thermal Paper

Though two-ply thermal paper is very useful for some applications, it requires higher printing energy than normal thermal paper since it contains two layers of thermal paper. Consequently, the control method is also different from that used for normal thermal paper.

The PT502P01 and PT500GA1 supports printing on two-ply thermal paper. The user can select whether printing will be performed on two-ply thermal paper or normal thermal paper through a function pin on the gate array (pin 35), or a command.

Table 3-5 shows the setting of the function pin on the gate array.

Table 3-5 Selection of Thermal Paper through the PT500GA1 Function Pin

| Pin No. 35 | Paper Selected        |  |

|------------|-----------------------|--|

| Low        | Normal thermal paper  |  |

| High       | Two-ply thermal paper |  |

For setting through a command, refer to code sequence ESC + ! + n in Section 9.5.

When the power is turned on or when the system is reset through a command or switch operation, the thermal paper that is specified by the function pin on the PT500GA1 takes precedence. After that, the thermal paper specified through a command takes precedence.

Table 3-6 Recommended Two-ply Thermal Paper

| Vendor               | Number   |  |

|----------------------|----------|--|

| Jujo Paper Co., Ltd. | TW80KK-M |  |

# Precautions for printing on two-ply thermal paper

Because of its characteristics, two-ply thermal paper requires different handling than normal thermal paper. The following should be taken into consideration when using two-ply thermal paper:

- The use of two-ply thermal paper is not supported during the fixed division mode. When fixed division is selected, the normal thermal paper is always selected.

- If the maximum number of dots to be activated is small, dense printing slows down the print speed.

- Since each strobe applies two pulses, the life span of the thermal head becomes one half of the life span of activation pulse resistance.

- If paper feed is stopped immediately after dense printing, such as solid black, paper may stick to the thermal head and may adversely affect paper feed. A minimum of five dots should be fed after performing prolonged dense printing.

- The bottom layer of two-ply thermal paper is sensitive to heat. Therefore, even the nonprinted part may darken if the printer is used in a high temperature environment or if dense printing is prolonged.

- If dense printing is performed using high-speed printing, the top layer of thermal paper may become blurred.

- When high resolution is required for output, (for example, in the case of graphic images), it is recommended that a low speed be selected for both the print speed and the paper feed rate.

- Ambient temperature should be between 10° C and 50° C during operation.

- To prevent the two-ply thermal paper from sticking to the thermal head, printer mechanisms that use 24 V (LTP5242, LTP5347, LTP5437, and LTP5442) block transfer dynamic division (described in Section 3.1) should not be used. For the same reason, the maximum number of dots to be activated for printer mechanisms that use 12 V (LTP5246 and LTP5446) should be set to a value more than or equal to the following:

LTP5246 :256 dots LTP5446 :448 dots

# 3.5 TEST PRINT

The PT502P01/PT500GA1 has a test print function. The current settings of the function pins and all available characters in the internal character set currently selected are printed when a test print is performed.

A test print can be performed by using one of the following procedures.

(1) Test print by turning the power on and off

Set the feed terminal (pin 16 on the PT502P01) to low, turn on  $V_{CC}$  and  $V_P$  (both simultaneously, or,  $V_{CC}$  first and then  $V_P$ ). The test print will then start.

(2) Test print via switches

The test print can be executed while the power ( $V_P$  and  $V_{CC}$ ) is on by performing the procedure below:

1. Before turning on the power, prepare normally-open switches by connecting a switch between the reset terminal (pin 28 on the PT502P01) and the GND and by connecting another between the feed terminal (pin 16 on the PT502P01) and the GND.

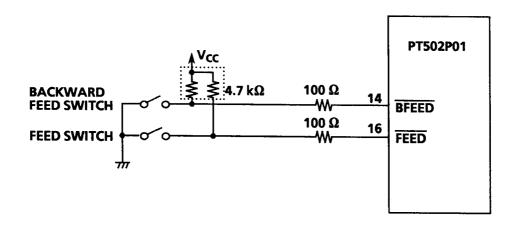

Each terminal should be pulled up with a 1 to 4.7 k $\Omega$  resistor and have a 100  $\Omega$  resistor serially inserted to prevent latch-up (see Figure 7-1). Care should be taken to prevent chattering of the switch.

- 2. Turn on both V<sub>CC</sub> and V<sub>P</sub> (simultaneously, or, V<sub>CC</sub> first and then V<sub>P</sub>).

- 3. Turn on the reset terminal (low), then turn on the feed terminal (low). Next, turn off the reset terminal (high), then turn off the feed terminal (high). The test print will then start.

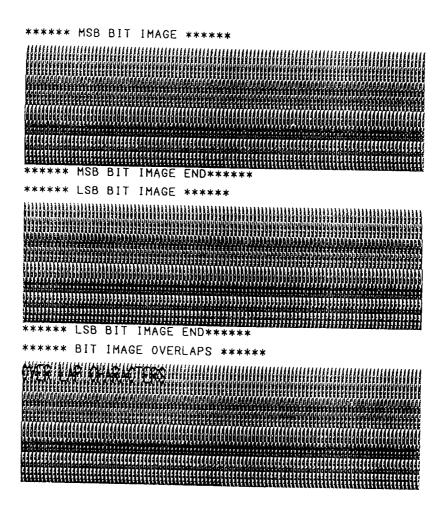

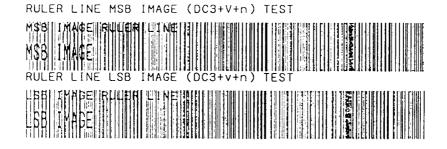

For a sample test print, see Figure 3-3.

```

LTP5000 series Interface

PT502P01 [ Ver 1.00 ]

11.Dec. 1992

Copyright(C): SII

*******

* DIP SWITCH 1 *

1..5) Mechanism : LTP5442

112mm, 24V, 8dot/mm

6) Feed : High speed

7) Print : High speed

8) Head drive : Dynamic division

* DIP SWITCH 2 *

1..3) DDD Max dot : 192 dots

4..5) I/F mode : MODE 0

6) FONT TYPE : IBM Compatible

7) 2PLY: 0FF

8) Data input : Parallel

* DIP SWITCH 3 *

1..3) Baud rate : 9600 bps

4) Bit length: 8 bit

5) Stop bit : 2 bit

6,7) Parity: None

8) Data control: Busy

* TEST PRINT *

!"#$%&'()*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPQRS

TUVWXYZ[\]^_`abcdefghijkImnopqrstuvwxyz{\}~ Çüéâäàāç

^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4} ^{4}

\equiv \pm \sum \subseteq \prod \div \approx^{\bullet} \cdot - \prod^{n \mid z} =

```

Figure 3-3 Test Print Sample (LTP5442)

# 3.6 HEX DUMP

The PT502P01/PT500GA1 contains a data dump function which allows data to be printed in hexadecimal.

There are two ways to execute the hex dump:

(1) Hex dump by turning the power on and off

Set the backward feed terminal (pin number 14 of the PT502P01) to low, turn on the  $V_{CC}$  and  $V_{P}$  (both simultaneously, or,  $V_{CC}$  first and then  $V_{P}$ ). The hex dump will then start.

(2) Hex dump via switches

A hex dump print can be executed while the power ( $V_P$  and  $V_{CC}$ ) is on by performing the procedure below:

1. Before turning on the power, prepare normally-open switches by connecting a switch between the reset terminal (pin 28 on the PT502P01) and the GND and by connecting another between the backward feed terminal (pin 14 on the PT502P01) and the GND.

Each terminal should be pulled up with a 1 to 4.7 k $\Omega$  resistor and have a 100  $\Omega$  resistor serially inserted to prevent latch-up (see Figure 7-1). Care should be taken to prevent chattering of the switch.

- 2. Turn on both V<sub>CC</sub> and V<sub>P</sub> (simultaneously, or, V<sub>CC</sub> first and then V<sub>P</sub>).

- 3. Turn on the reset terminal, then turn on the backward feed terminal (low). And turn off the reset terminal (high), then turn off the backward feed terminal (high). The hex dump will then start.

Data can be input in either serial or parallel.

The LTP5442 and LTP5446 start printing when they have received 16 bytes of data. The LTP5242, LTP5246, LTP5347, and LTP5437 start printing when they have received 8 bytes of data. Some data may remain in the buffer without being printed if the buffer does not become full. When data input is complete, set the feed terminal (pin 16 on the PT502P01) to low so that data remaining in the buffer will be printed.

For a sample hex dump, see Figure 3-4.

```

( HEX DUMP MODE ]

OD OA 2A 2A 2A 2A 2A 2A 2O 46 45 45 44 20 50 41

45 52 20 46 4F 52 57 41 52 44 20 42 41 43 48 57

41 52 44 20 54 45 53 54 20 2A 2A 2A 2A 2A 2A 0D

OA 18 41 00 20 30 20 44 4F 54 20 46 45 45 44 2D

20 2D 20 2D 20 2D 20 1B 4A 00 1B 6A 18 20 30 20

20 32 34 20 44 4F 54 20 42 46 45 45 44 0D 0A 1B

41 00 20 35 31 20 44 4F 54 20 46 45 45 44 2D 20

2D 2D 2D 2D 2D 2D 1B 4A 33 1B 6A 4B 2D 35 31 2D

20 37 35 20 44 4F 54 20 42 46 45 45 44 0D 0A 1B

41 00 20 31 30 32 20 44 4F 54 20 46 45 45 44 20

.20 2D 20 2D 2D 2D 2D 1B 4A 66 1B 6A 7E 2O 31 30

20 20 20 31 32 36 20 44 4F 54 20 42 46 45 45 44

OD OA 18 41 00 20 31 35 33 20 44 4F 54 20 46 45

45 44 20 20 20 20 20 20 20 20 18 4A 99 18 6A B1

20 31 35 33 20 20 20 20 20 20 20 20 20 20 20 20 20

20 20 20 20 20 20 31 37 37 20 44 4F 54 20 42 46

45 45 44 00 0A 1B 41 00 20 32 30 34 20 44 4F 54

20 46 45 45 44 2D 20 2D 2D 2D 2D 2D 2D 1B 4A CC

1B 6A E4 20 32 30 34 20 20 20 20 20 20 20 20 20

20 20 20 20 20 20 20 20 20 32 32 38 20 44 4F 54

20 42 46 45 45 44 0D OA 2A 2A 2A 2A 2A 2A 2D 52

45 53 45 54 20 54 45 53 54 20 2A 2A 2A 2A 2A 2A

2A OD OA 1B 57 O1 41 42 43 OD OA 1B 77 O1 41 42

43 00 0A 1B 49 01 41 42 43 0D 0A 1B 40 41 46 54

45 52 20 52 45 53 45 54 OD OA

```

Figure 3-4 Hex Dump Print Sample (LTP5442)

# **CHAPTER 4**

# **HARDWARE SPECIFICATIONS**

# **4.1 ABSOLUTE MAXIMUM RATINGS**

Tables 4-1 and 4-2 list the absolute maximum ratings of the PT502P01 CPU and PT500GA1 Gate Array, respectively.

Table 4-1 PT502P01 Absolute Maximum Ratings

| Item                 | Symbol           | Conditions             | Rating                            |

|----------------------|------------------|------------------------|-----------------------------------|

| Power supply voltage | Vcc              | _                      | – 0.3 V to 7 V                    |

| Analog power voltage | AV <sub>CC</sub> | _                      | – 0.3 V to 7 V                    |

| Input voltage        | VI               | _                      | -0.3 V to V <sub>CC</sub> + 0.3 V |

| Output voltage       | Vo               | -                      | -0.3 V to V <sub>CC</sub> + 0.3 V |

| Power consumption    | P <sub>D</sub>   | T <sub>A</sub> = 25° C | 500 mW                            |

| Storage temperature  | T <sub>STG</sub> | _                      | - 40° to 125° C                   |

Table 4-2 PT500GA1 Absolute Maximum Ratings

| ltem                 | Symbol           | Conditions             | Rating                            |

|----------------------|------------------|------------------------|-----------------------------------|

| Power supply voltage | Vcc              |                        | -0.3 V to 6.5 V                   |

| Input voltage        | VI               | _                      | -0.3 V to V <sub>CC</sub> + 0.3 V |

| Output voltage       | Vo               |                        | -0.3 V to V <sub>CC</sub> + 0.3 V |

| Power consumption    | P <sub>D</sub>   | T <sub>A</sub> = 25° C | 500 mW                            |

| Storage temperature  | T <sub>STG</sub> |                        | – 40° to 125° C                   |

# **4.2 OPERATING RANGES**

Tables 4-3 and 4-4 list the operating ranges of the PT502P01 CPU and PT500GA1 Gate Array, respectively.

**Table 4-3 PT502P01 Operating Range Characteristics**

| Item                           | Symbol               | Conditions | Rating           |

|--------------------------------|----------------------|------------|------------------|

| Power supply voltage           | Vcc                  | _          | 4.75 V to 5.25 V |

| Operating temperature          | T <sub>OPR</sub>     | _          | – 10° to 70° C   |

| External clock input frequency | f (X <sub>IN</sub> ) | _          | 16 ± 0.08 MHz    |

**Table 4-4 PT500GA1 Operating Range Characteristics**

| ltem                  | Symbol           | Conditions  | Rating                 |

|-----------------------|------------------|-------------|------------------------|

| Power supply voltage  | V <sub>CC</sub>  | <del></del> | 4.75 V to 5.25 V       |

| Input voltage         | VI               | _           | 0 V to V <sub>CC</sub> |

| Output voltage        | Vo               | _           | 0 V to V <sub>CC</sub> |

| Operating temperature | T <sub>OPR</sub> |             | – 10° to 70° C         |

## 4.3 ELECTRICAL CHARACTERISTICS

Tables 4-5 and 4-6 list the electrical characteristics of the PT502P01 CPU and PT500GA1 Gate Array, respectively.

Table 4-5 PT502P01 Electrical Characteristics  $(V_{CC} = 5 \text{ V}, T_A = 25^{\circ}\text{C}, f(X_{IN}) = 16 \text{ MHz})$

| ltem                 | Symbol                | Conditions                | Rating |       |       |

|----------------------|-----------------------|---------------------------|--------|-------|-------|

| iteiii               | Symbol                | Conditions                | MIN    | STD   | MAX   |

| Output voltage "H"   | V <sub>OH</sub>       | $I_{OH} = -10 \text{ mA}$ | 3 V    | _     | _     |

| Output voltage "L"   | V <sub>OL</sub>       | I <sub>OL</sub> = 10 mA   | _      | _     | 2 V   |

| Hysteresis (HTE)     | $(V_T + ) - (V_T - )$ | <del>_</del>              | 0.4 V  |       | 1 V   |

| Hysteresis (RESET)   | $(V_T + ) - (V_T - )$ | _                         | 0.2 V  | _     | 0.5 V |

| Hysteresis (Xin)     | $(V_T + )-(V_T - )$   |                           | 0.1 V  |       | 0.3 V |

| Input current "H"    | lін                   | V <sub>1</sub> = 5 V      | _      |       | 5 μΑ  |

| Input current "L"    | I <sub>IH</sub>       | V <sub>I</sub> = 0 V      |        |       | -5 μA |

| Power supply current | lcc                   | $f(X_{IN}) = 16 MHz$      |        | 12 mA | 24 mA |

Table 4-6 PT500GA1 Electrical Characteristics (T<sub>A</sub> = 25°C)

| Item                           | Symbol Conditions    |                                                                              |                 | Rating |                 |

|--------------------------------|----------------------|------------------------------------------------------------------------------|-----------------|--------|-----------------|

| ite                            | Jymbol               | Conditions                                                                   | MIN             | STD    | MAX             |

| Input voltage "H"              | V <sub>IH</sub>      | V <sub>CC</sub> = 5.5 V <sup>1</sup><br>V <sub>CC</sub> = 5.5 V <sup>2</sup> | 2.2 V<br>3.85 V |        | 5.5 V<br>5.5 V  |

| Input voltage "L"              | V <sub>IL</sub>      | V <sub>CC</sub> = 4.5 V <sup>1</sup><br>V <sub>CC</sub> = 4.5 V <sup>2</sup> | 0               | _      | 0.8 V<br>1.35 V |

| Hysteresis                     | (V <sub>T</sub> + )- | V <sub>CC</sub> = 5.0 V <sup>2</sup>                                         | 0.5 V           |        | 1.6 V           |

| Input current "H"              | l <sub>IH</sub>      | $V_{CC} = 5.5 \text{ V}, V_{I} = 5.5 \text{ V}$                              |                 |        | 1 μΑ            |

| Input current "L"              | Ι <sub>Ι</sub> L     | $V_{CC} = 5.5 \text{ V}, V_{I} = 0 \text{ V}$                                | _               |        | 1 μΑ            |

| Output voltage "H"             | VoH                  | $V_{CC} = 5.0 \text{ V, I}_{O} < 1 \mu\text{A}$                              | 4.95 V          |        |                 |

| Output voltage "L"             | Vol                  | $V_{CC} = 5.0 \text{ V, } I_{O} < 1 \mu\text{A}$                             |                 |        | 0.05 V          |

| Output current "H"             | Іон                  | $V_{CC} = 4.5 \text{ V}, V_{OH} = 4.1 \text{ V}$                             | _               | _      | - 2 mA          |

| Output current "L"             | loL                  | $V_{CC} = 4.5 \text{ V}, V_{OL} = 0.4 \text{ V}$                             | 6 μΑ            |        |                 |

| Pull-up resistance             | Ru                   | $V_{CC} = 5.0 \text{ V}, V_{I} = 0 \text{ V}^{3}$                            | <b>50 k</b> Ω   |        | <b>500 k</b> Ω  |

| Power supply current (standby) | IDD                  | $V_I = V_{SS}$ , $V_{CC}I_O = 0 \mu A$                                       |                 | _      | 5 mA            |

<sup>1</sup> Input terminals other than ID0-ID7 and STB

<sup>&</sup>lt;sup>2</sup> ID0-ID7 and STB

$<sup>^3</sup>$  RES0, RES1, DP10-DP17, DP20-DP27, DP30-DP37,  $\Phi,$  MODE, SDAT, SCLK, and KNJ0 to KNJ7

## 4.4 PIN DESCRIPTION

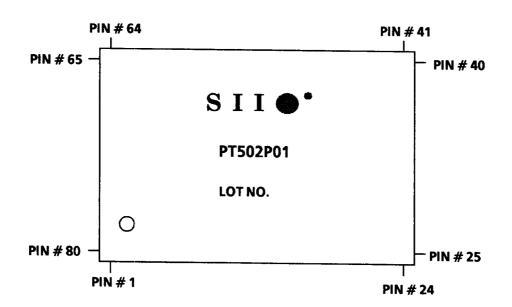

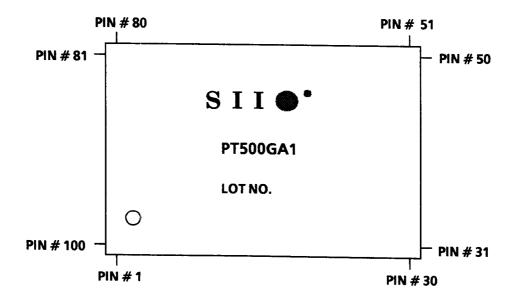

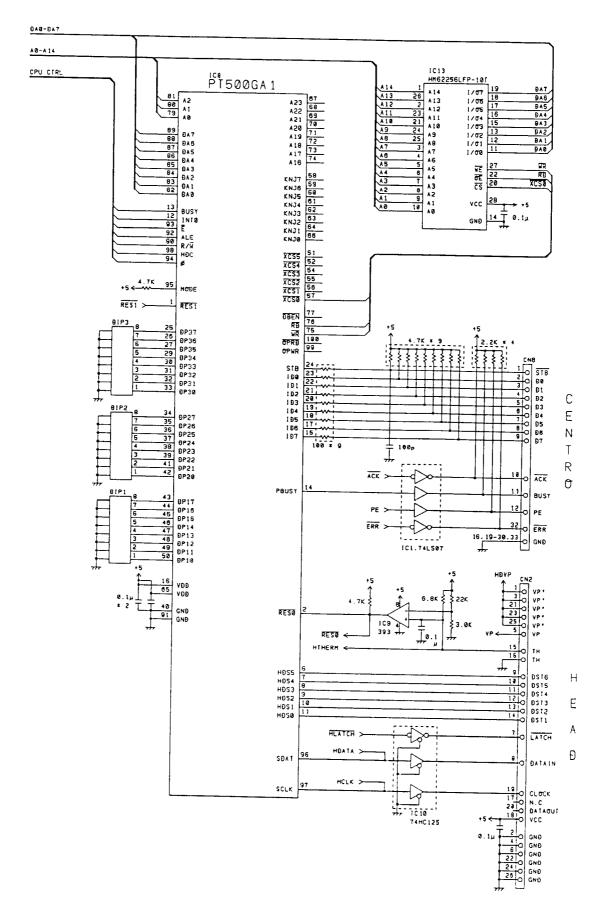

Figures 4-1 and 4-2 show the pin configurations of the PT502P01 CPU and PT500GA1 Gate Array, respectively. These figures are top views of the ICs. Tables 4-7 and 4-8 contain the pin definitions for the PT502P01 and PT500GA1, respectively.

Figure 4-1 PT502P01 Pin Configuration

Figure 4-2 PT500GA1 Pin Configuration

**Table 4-7 PT502P01 Pin Definitions**

| Pin<br>No. | Signal<br>Name | 1/01 | Function                                                         | Connected to<br>Gate Array Pin | Logic <sup>2</sup> |

|------------|----------------|------|------------------------------------------------------------------|--------------------------------|--------------------|

| 1          | SVP            | ı    | V <sub>P</sub> detection                                         |                                |                    |

| 2          | ERROR          | 0    | Error signal                                                     | <del>_</del>                   | L                  |

| 3          | BUSY           | 0    | Centronics data reception enabled                                | _                              | Н                  |

| 4          | ĀCK            | 0    | Centronics data reception complete                               |                                | L                  |

| 5          | ECUT           | 0    | Autocutter enable                                                |                                | Н                  |

| 6          | HTE            | ı    | Head temperature error                                           |                                | L                  |

| 7          | INT0           | ı    | Centronics data interrupt                                        | 12 (INT0)                      | _                  |

| 8          | CUT1           | 0    | Motor control terminal 1 for cutter                              | _                              | L                  |

| 9          | CUT2           | 0    | Motor control terminal 2 for cutter                              |                                | L                  |

| 10         | HDC            | 1    | Head dot counter                                                 | 98 (HDC)                       | _                  |

| 11         | HLATCH         | 0    | Head latch                                                       |                                | L                  |

| 12         | HVCCSW         | 0    | Head Vcc                                                         |                                | Н                  |

| 13         | HVPSW          | 0    | Head Vp                                                          |                                | Н                  |

| 14         | BFEED          | l i  | Backward feed                                                    | <del></del>                    | L                  |

| 15         | MCOM1          | 0    | Motor common                                                     |                                | Н                  |

| 16         | FEED           | 1    | Feed                                                             | _                              | L                  |

| 17         | SENCUT         | 0    | Cutter sensor input                                              |                                | L                  |

| 18         | MOTOR1         | 0    | Motor <b>Φ</b> 1                                                 |                                | Н                  |

| 19         | MOTOR2         | 0    | Motor Ф2                                                         |                                | Н                  |

| 20         | MOTOR3         | 0    | Motor ⊕3                                                         |                                | Н                  |

| 21         | MOTOR4         | 0    | Motor <b>Ф</b> 4                                                 | _                              | Н                  |

| 22         | OPE            | 0    | Out-of-paper error                                               | -                              | Н                  |

| 23         | Φ              | 0    | Φ                                                                | <b>94</b> (Φ)                  |                    |

| 24         | RDY            | Ī    | (Must be pulled up to $V_{CC}$ through a 10 $k\Omega$ resistor.) | _                              |                    |

| 25         | HOLD           | ı    | (Must be pulled up to $V_{CC}$ through a 10 $k\Omega$ resistor.) | _                              |                    |

| 26         | BYTE           | 1    | (Must be pulled up to $V_{CC}$ through a 10 $k\Omega$ resistor.) |                                |                    |

| 27         | CNVSS          |      | (Must be connected to GND.)                                      |                                |                    |

<sup>1</sup> I :Input O :Output 2 L :Low H :High

Table 4-7 PT502P01 Pin Definitions (Continued)

| Pin<br>No. | Signal<br>Name | I/O1     | Function              | Connected to<br>Gate Array Pin | Logic <sup>2</sup> |

|------------|----------------|----------|-----------------------|--------------------------------|--------------------|

| 28         | RESET          | ı        | Reset                 |                                | L                  |

| 29         | Xin            | <b> </b> | Clock input (16 MHz)  | _                              |                    |

| 30         | Xout           | 1-       | Clock output (16 MHz) |                                |                    |

| 31         | Ē              | 0        | Enable clock          | 93 (E)                         | L                  |

| 32         | VSS            | 1-       | Ground                | _                              |                    |

| 33         | P33            | 0        | NC (Reserved)         |                                | _                  |

| 34         | ALE            | 0        | ALE                   | 92 (ALE)                       | Н                  |

| 35         | P31            | 0        | NC (Reserved)         | _                              |                    |

| 36         | R/W            | 0        | R/W                   | 90 (R/W)                       |                    |

| 37         | DA7            | 1/0      | A23/D7                | 89 (DA7)                       | Н                  |

| 38         | DA6            | 1/0      | A22/D6                | 88 (DA6)                       | Н                  |

| 39         | DA5            | I/O      | A21/D5                | 87 (DA5)                       | Н                  |

| 40         | DA4            | 1/0      | A20/D4                | 86 (DA4)                       | Н                  |

| 41         | DA3            | 1/0      | A19/D3                | 85 (DA3)                       | Н                  |

| 42         | DA2            | 1/0      | A18/D2                | 84 (DA2)                       | Н                  |

| 43         | DA1            | 1/0      | A17/D1                | 83 (DA1)                       | Н                  |

| 44         | DA0            | 1/0      | A16/D0                | 82 (DA0)                       | Н                  |

| 45         | A15            | 0        | NC (Reserved)         | _                              | _                  |

| 46         | A14            | 0        | A14                   |                                | Н                  |

| 47         | A13            | 0        | A13                   | _                              | Н                  |

| 48         | A12            | 0        | A12                   | _                              | Н                  |

| 49         | A11            | 0        | A11                   |                                | Н                  |

| 50         | A10            | 0        | A10                   |                                | Н                  |

| 51         | A9             | 0        | A9                    | _                              | Н                  |

| 52         | A8             | 0        | A8                    |                                | Н                  |

| 53         | A7             | 0        | A7                    | *****                          | Н                  |

| 54         | A6             | 0        | A6                    |                                | Н                  |

| 55         | A5             | 0        | A5                    | _                              | Н                  |

1 I :Input O :Output 2 L :Low H :High

Table 4-7 PT502P01 Pin Definitions (Continued)

| Pin<br>No. | Signal<br>Name   | I/O <sup>1</sup> | Function                                                                                                 | Connected to<br>Gate Array Pin | Logic <sup>2</sup> |

|------------|------------------|------------------|----------------------------------------------------------------------------------------------------------|--------------------------------|--------------------|

| 56         | A4               | 0                | A4                                                                                                       |                                | Н                  |

| 57         | A3               | 0                | A3                                                                                                       |                                | Н                  |

| 58         | A2               | 0                | A2                                                                                                       | 81 (A2)                        | Н                  |

| 59         | A1               | 0                | A1                                                                                                       | 80 (A1)                        | Н                  |

| 60         | A0               | 0                | Α0                                                                                                       | 79 (A0)                        | Н                  |

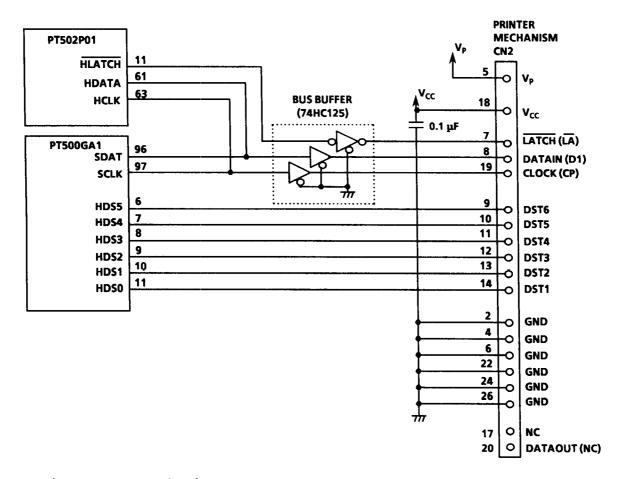

| 61         | HDATA            | 0                | Head data output                                                                                         | 96 (SDAT)                      | Н                  |

| 62         | DPI              | 1                | Optional DIP switch data input (must be pulled up to Vcc through a 10 $k\Omega$ resistor when not used.) | <del>-</del>                   | Н                  |

| 63         | HCLK             | 0                | Optional DIP switch clock/head clock                                                                     | 97 (SCLK)                      | <u></u>            |

| 64         | DPL              | 0                | Optional DIP switch data load                                                                            | _                              | L                  |

| 65         | TXD0             | 0                | RS-232C (Xon/Xoff)                                                                                       | _                              | Н                  |

| 66         | RXD0             | 1                | RS-232C (Data input)                                                                                     | _                              | Н                  |

| 67         | SBSY             | 0                | RS-232C (Busy output)                                                                                    | _                              | Н                  |

| 68         | P80              | 0                | NC (Reserved)                                                                                            |                                |                    |

| 69         | Vcc              |                  | Vcc                                                                                                      |                                | _                  |

| 70         | AV <sub>CC</sub> | _                | Vcc                                                                                                      |                                |                    |

| 71         | VREF             |                  | (Must be connected to V <sub>CC</sub> .)                                                                 |                                | _                  |

| 72         | AVSS             | _                | Ground                                                                                                   |                                | _                  |

| 73         | VSS              |                  | Ground                                                                                                   |                                | _                  |

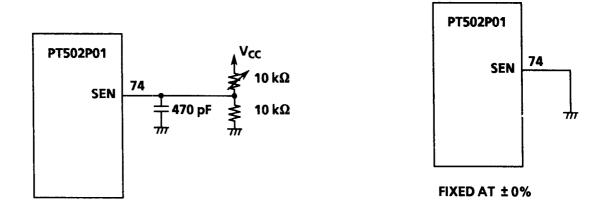

| 74         | SEN              | I                | Print density control<br>( – 15% to + 35%)                                                               |                                | _                  |

| 75         | HS               | I                | Head-up detection                                                                                        |                                | L                  |

| 76         | SV <sub>CC</sub> | I                | Reference voltage detection                                                                              |                                | _                  |

| 77         | PS               | I                | Paper detection                                                                                          |                                | Н                  |

| 78         | SHVP             | 1                | Head Vp voltage                                                                                          |                                | _                  |

| 79         | SHR              |                  | Head resistance measurement                                                                              | _                              |                    |

| 80         | STH              | I                | Head thermistor detection                                                                                |                                | _                  |

1 | I :Input O :Output

2 | L :Low | H :High | \( \int\_{-}^{\infty} \) : Leading edge

Table 4-8 PT500GA1 Pin Definitions

| Pin<br>No. | Signal<br>Name | I/O1 | Characteristics                | Function                             | Logic <sup>2</sup> |

|------------|----------------|------|--------------------------------|--------------------------------------|--------------------|

| 1          | RES1           | 1    | TTL level input (with pull-up) | Head strobe disable                  | L                  |

| 2          | RESO           |      | TTL level input (with pull-up) | Head strobe disable                  | L                  |

| 3          | N.U            | -    | NC                             | _                                    |                    |

| 4          | HDS7           | 0    | NC                             | Reserved                             |                    |

| 5          | HDS6           | 0    | NC                             | Reserved                             | _                  |

| 6          | HDS5           | 0    | CMOS output                    | Printer mechanism head strobe signal | Н                  |

| 7          | HDS4           | 0    | CMOS output                    | Printer mechanism head strobe signal | Н                  |

| 8          | HDS3           | 0    | CMOS output                    | Printer mechanism head strobe signal | Н                  |

| 9          | HDS2           | 0    | CMOS output                    | Printer mechanism head strobe signal | Н                  |

| 10         | HDS1           | 0    | CMOS output                    | Printer mechanism head strobe signal | Н                  |

| 11         | HDS0           | 0    | CMOS output                    | Printer mechanism head strobe signal | Н                  |

| 12         | INT0           | 0    | CMOS output                    | Centronics interrupt signal          | Н                  |

| 13         | BUSY           |      | TTL level input                | BUSY request signal                  | L                  |

| 14         | PBUSY          | 0    | CMOS output                    | BUSY signal                          | Н                  |

| 15         | ID7            | 1    | CMOS level Schmitt input       | Centronics data input signal         | Н                  |

| 16         | Vcc            | _    | Vcc                            | 5 V                                  | _                  |

| 17         | ID6            | I    | CMOS level Schmitt input       | Centronics data input signal         | Н                  |

| 18         | ID5            | I    | CMOS level Schmitt input       | Centronics data input signal         | Н                  |

| 19         | ID4            | _    | CMOS level Schmitt input       | Centronics data input signal         | Н                  |

| 20         | ID3            |      | CMOS level Schmitt input       | Centronics data input signal         | Н                  |

| 21         | ID2            | 1    | CMOS level Schmitt input       | Centronics data input signal         | Н                  |

| 22         | ID1            | 1    | CMOS level Schmitt input       | Centronics data input signal         | Н                  |

| 23         | ID0            | ı    | CMOS level Schmitt input       | Centronics data input signal         | Н                  |

| 24         | STB            | I    | CMOS level Schmitt input       | Centronics strobe input signal       | 1                  |

Table 4-8 PT500GA1 Pin Definitions (Continued)

| Pin<br>No. | Signal<br>Name | I/O1 | Characteristics                | Function                                       | Logic <sup>2</sup> |

|------------|----------------|------|--------------------------------|------------------------------------------------|--------------------|

| 25         | DP37           | ı    | TTL level input (with pull-up) | BUSY control select                            | Н                  |

| 26         | DP36           |      | TTL level input (with pull-up) | Parity enable/disable select                   | Н                  |

| 27         | DP35           | _    | TTL level input (with pull-up) | Parity odd/even select                         | Н                  |

| 28         | N.U            |      | NC                             | <del></del>                                    | _                  |

| 29         | DP34           | Ι    | TTL level input (with pull-up) | Stop bit select                                | Н                  |

| 30         | DP33           | I    | TTL level input (with pull-up) | Data length select                             | Н                  |

| 31         | DP32           | ı    | TTL level input (with pull-up) | Baud rate select                               | Н                  |

| 32         | DP31           | I    | TTL level input (with pull-up) | Baud rate select                               | Н                  |

| 33         | DP30           | I    | TTL level input (with pull-up) | Baud rate select                               | Н                  |

| 34         | DP27           | 1    | TTL level input (with pull-up) | Data receive mode select                       | Н                  |

| 35         | DP26           | ı    | TTL level input (with pull-up) | Paper type select                              | Н                  |

| 36         | DP25           | ı    | TTL level input (with pull-up) | Character set select                           | Н                  |

| 37         | DP24           | 1    | TTL level input (with pull-up) | Interface mode select                          | Н                  |

| 38         | DP23           | I    | TTL level input (with pull-up) | Interface mode select                          | Н                  |

| 39         | DP22           | ı    | TTL level input (with pull-up) | Dynamic division mode maximum dot count select | Н                  |

| 40         | GND            | _    | Ground                         |                                                |                    |

| 41         | DP21           | ı    | TTL level input (with pull-up) | Dynamic division mode maximum dot count select | Н                  |

| 42         | DP20           | 1    | TTL level input (with pull-up) | Dynamic division mode maximum dot count select | н                  |

| 43         | DP17           |      | TTL level input (with pull-up) | Print mode select                              | Н                  |

| 44         | DP16           |      | TTL level input (with pull-up) | Maximum print speed select                     | Н                  |

| 45         | DP15           |      | TTL level input (with pull-up) | Paper feed rate select                         | Н                  |

| 46         | DP14           | 1    | TTL level input (with pull-up) | Printer mechanism model select                 | Н                  |

| 47         | DP13           | I    | TTL level input (with pull-up) | Printer mechanism model select                 | Н                  |

| 48         | DP12           |      | TTL level input (with pull-up) | Printer mechanism model select                 | Н                  |

<sup>&</sup>lt;sup>1</sup> I :Input O :Output <sup>2</sup> L :Low H :High

Table 4-8 PT500GA1 Pin Definitions (Continued)

| Pin<br>No. | Signal<br>Name | I/O <sup>1</sup> | Characteristics                | Function                       | Logic <sup>2</sup> |

|------------|----------------|------------------|--------------------------------|--------------------------------|--------------------|

| 49         | DP11           |                  | TTL level input (with pull-up) | Printer mechanism model select | Н                  |

| 50         | DP10           | Ι                | TTL level input (with pull-up) | Printer mechanism model select | н                  |

| 51         | XCS5           | 0                | NC                             | Reserved                       | _                  |

| 52         | XCS4           | 0                | NC                             | Reserved                       |                    |

| 53         | N.U            | -                | NC                             | _                              | _                  |

| 54         | XCS3           | 0                | NC                             | Reserved                       |                    |

| 55         | XCS2           | 0                | NC                             | Reserved                       | I —                |

| 56         | XCS1           | 0                | NC                             | Reserved                       | _                  |

| 57         | XCS0           | 0                | CMOS output                    | External RAM enable            | L                  |

| 58         | KNJ7           | 1                | NC (with internal pull-up)     | Reserved                       |                    |

| 59         | KNJ6           | 1                | NC (with internal pull-up)     | Reserved                       | _                  |

| 60         | KNJ5           | I                | NC (with internal pull-up)     | Reserved                       | _                  |

| 61         | KNJ4           | T                | NC (with internal pull-up)     | Reserved                       | <b>1</b> —         |

| 62         | KNJ3           | 1                | NC (with internal pull-up)     | Reserved                       | _                  |

| 63         | KNJ2           | 1                | NC (with internal pull-up)     | Reserved                       |                    |

| 64         | KNJ1           | 1                | NC (with internal pull-up)     | Reserved                       | _                  |

| 65         | Vcc            | 1-               | V <sub>CC</sub>                | 5 V                            | <del> </del>       |

| 66         | KNJ0           | 1                | NC (with internal pull-up)     | Reserved                       |                    |

| 67         | A23            | 0                | NC                             | Reserved                       |                    |

| 68         | A22            | 0                | NC                             | Reserved                       | _                  |

| 69         | A21            | 0                | NC                             | Reserved                       | <b> </b>           |

| 70         | A20            | 0                | NC                             | Reserved                       | <del> </del>       |

| 71         | A19            | 0                | NC                             | Reserved                       | <b>—</b>           |

| 72         | A18            | 0                | NC                             | Reserved                       | 1-                 |

| 73         | A17            | 0                | NC                             | Reserved                       |                    |

| 74         | A16            | 0                | NC                             | Reserved                       | 1 —                |

| 75         | WR             | 0                | CMOS output                    | Write enable                   | L                  |

1 I :Input

2 L :Low

O :Output

H :High

Table 4-8 PT500GA1 Pin Definitions (Continued)

| Pin<br>No. | Signal<br>Name | I/O <sup>1</sup> | Characteristics                | Function                                          | Logic <sup>2</sup> |

|------------|----------------|------------------|--------------------------------|---------------------------------------------------|--------------------|

| 76         | RD             | 0                | CMOS output                    | Read enable                                       | L                  |

| 77         | DBEN           | 0                | NC                             | Reserved                                          |                    |

| 78         | N.U            | _                | NC                             |                                                   |                    |

| 79         | A0             | -                | TTL level input                | Address bus                                       | Н                  |

| 80         | A1             | ı                | TTL level input                | Address bus                                       | Н                  |

| 81         | A2             | 1                | TTL level input                | Address bus                                       | Н                  |

| 82         | DA0            | 1/0              | TTL level input CMOS output    | Data bus                                          | Н                  |

| 83         | DA1            | 1/0              | TTL level input CMOS output    | Data bus                                          | Н                  |

| 84         | DA2            | 1/0              | TTL level input CMOS output    | Data bus                                          | Н                  |

| 85         | DA3            | 1/0              | TTL level input CMOS output    | Data bus                                          | Н                  |

| 86         | DA4            | 1/0              | TTL level input CMOS output    | Data bus                                          | Н                  |

| 87         | DA5            | 1/0              | TTL level input CMOS output    | Data bus                                          | Н                  |

| 88         | DA6            | 1/0              | TTL level input CMOS output    | Data bus                                          | Н                  |

| 89         | DA7            | 1/0              | TTL level input CMOS output    | Data bus                                          | Н                  |

| 90         | R/W            | ı                | TTL level input                | Read/write input signal                           | _                  |

| 91         | GND            | _                | Ground                         |                                                   | 1_                 |

| 92         | ALE            | 1                | TTL level input                | ALE input signal                                  | Н                  |

| 93         | E              | T                | TTL level input                | Enable clock input signal                         | L                  |

| 94         | Φ              | T                | TTL level input (with pull-up) | Phase input signal Φ                              |                    |

| 95         | MODE           | l                | TTL level input (with pull-up) | Must be pulled up with a 4.7 k $\Omega$ resistor. |                    |

| 96         | SDAT           | 1                | TTL level input (with pull-up) | Head data input signal                            | Н                  |

| 97         | SCLK           | 1                | TTL level input (with pull-up) | Head clock input signal                           | Н                  |

| 98         | HDC            | 0                | CMOS output                    | Head data counter output                          | Н                  |

| 99         | OPWR           | 0                | NC                             | Reserved                                          |                    |

| 100        | OPRD           | 0                | NC                             | Reserved                                          | 1 —                |

<sup>1</sup> I :Input2 L :LowO :OutputH :High

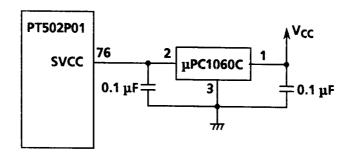

# 4.5 POWER CONNECTION

The PT502P01 CPU and PT500GA1 Gate Array power pins must be connected as listed in Tables 4-9 and 4-10.

Table 4-9 PT502P01 Power Pin Connection

| Pin No. | Symbol          | Connected to |

|---------|-----------------|--------------|

| 69      | V <sub>CC</sub> | Vcc          |

| 70      | V <sub>CC</sub> | Vcc          |

| 72      | AVss            | GND          |

| 73      | Vss             | GND          |

Table 4-10 PT500GA1 Power Pin Connection

| Pin No. | Symbol          | Connected to |

|---------|-----------------|--------------|

| 16      | V <sub>CC</sub> | Vcc          |

| 40      | GND             | GND          |

| 65      | V <sub>CC</sub> | Vcc          |

| 91      | GND             | GND          |

# NOTE

A 0.01  $\mu\text{F}$  to 0.1  $\mu\text{F}$  bypass capacitor must be connected across the V<sub>CC</sub> and GND pins of both the PT502P01 and PT500GA1.

# 4.6 TREATMENT OF UNUSED PINS

The unused pins on the PT502P01 CPU and PT500GA1 Gate Array are listed below. These pins should not be connected to anything.

PT502P01 Pins 33, 35, 45, and 68

PT500GA1

Pins 3, 4, 5, 28, 51, 52, 53, 54, 55, 56, 58, 59, 60, 61, 62, 63, 64, 66, 67, 68, 69, 70, 71, 72, 73, 74, 77, 78, 99, and 100

#### 4.7 RESET CIRCUIT

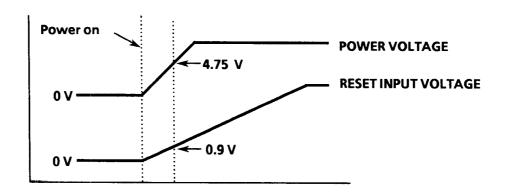

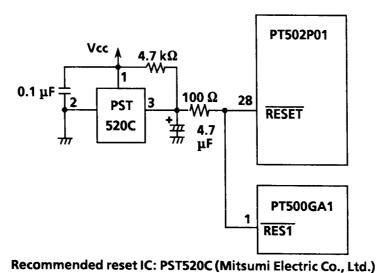

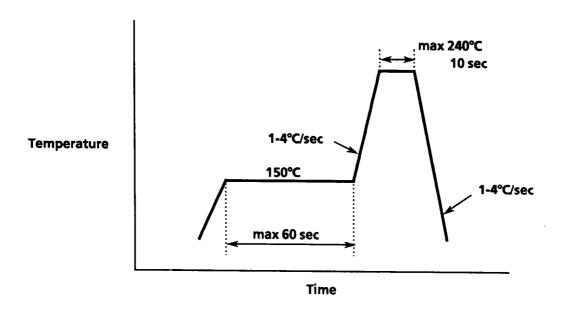

When the reset terminal (pin 28) is reset to high after being held low for longer than 2 microseconds at  $5 \text{ V} \pm 5\%$ , the PT502P01 CPU will return from the reset state and then initiate a programmed start sequence. The reset circuit must be designed so that the reset input voltage is 0.9 V or below at the point when the power voltage exceeds 4.75 V, as shown in Figure 4-3.

In the PT500GA1 Gate Array, when RES1 (pin 1) is set to low, gate array terminals HDS0 to HDS5 (pins 6 to 11) are forced to low and the thermal head is turned off.

An example of a reset circuit is shown in Figure 4-4.

Figure 4-3 Power-on Reset Condition

Recommended reserre. P31320C (WitSumi Electric Co., Ltd.

Figure 4-4 Sample Reset Circuit

#### 4.8 OSCILLATOR CIRCUIT

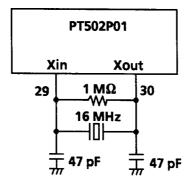

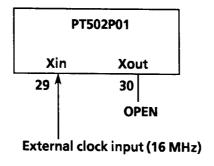

The PT502P01 CPU is provided with an internal oscillator circuit that generates necessary clocks. The internal clock  $\phi$  is developed by dividing by two the frequency of the clock input to the clock input terminal Xin (pin 29). The bus cycle operation is based on the clock whose rate is obtained by further dividing by two the resulting internal clock  $\phi$ . The internal oscillator circuit requires a ceramic or crystal resonator as an external device.

Figure 4-5 shows an example of an internal oscillator configuration using a ceramic resonator.

Figure 4-6 shows an example of an internal oscillator configuration that makes use of an external clock signal.

Recommended ceramic resonator: CSA16.00MX040 (Murata MFG. Co., Ltd.)

Figure 4-5 External Ceramic Resonator Circuit

Figure 4-6 External Clock Input Circuit

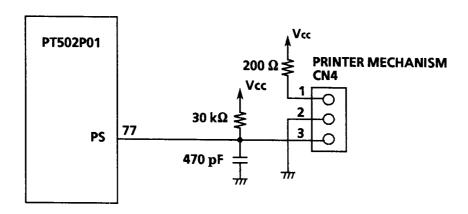

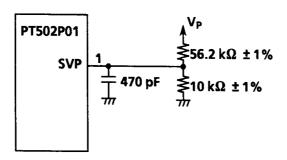

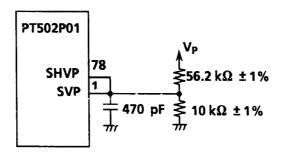

#### 4.9 PAPER DETECTION

The PT502P01 uses the input signal from the photo-interrupter mounted in the printer mechanism to check for paper.

The paper detector on the printer mechanism sets PS (pin 77 on the CPU) to low when paper exists, and sets it to high when out of paper.

When the PS terminal goes to high, the PT502P01 stops print operation and puts the printer in standby mode. At that time, the PT502P01 retains the print data. When the feed terminal (pin 16) is set to low after paper is installed, the PT502P01 resumes printing from the beginning of the line where the printing was suspended.

A sample paper detection circuit is shown in Figure 4-7.

Figure 4-7 Sample Paper Detection Circuit

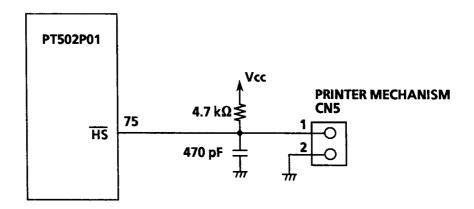

#### 4.10 HEAD-UP DETECTION CIRCUIT

The PT502P01 uses the input signal from the touch sensor mounted in the printer mechanism to check whether the thermal head is up or down.

The head-up detector is open when the head is in the down position and closed when the head is in the up position.

When the thermal head is in the up position, the HS terminal (pin 75) on the CPU becomes low. At that time, the PT502P01 stops print operation and puts the printer in standby mode. While in standby mode, the PT502P01 retains the print data. When the head returns to the down position, the PT502P01 resumes printing about one second later from the beginning of the line where printing was suspended.

A sample head-up detection circuit is shown in Figure 4-8.

Figure 4-8 Sample Head-up Detection Circuit

#### 4.11 MOTOR CONTROL CIRCUIT

It is recommended that two power supplies be used with the PT502P01 to control the motor. By detecting V<sub>P</sub> voltage variation and automatically controlling the applied V<sub>P</sub> pulse width of the motor, the influence of voltage variation can be minimized and motor heat can be reduced.

When the print speed is set to high, acceleration control is automatically executed to prevent the print pitch from being too small at motor start up.

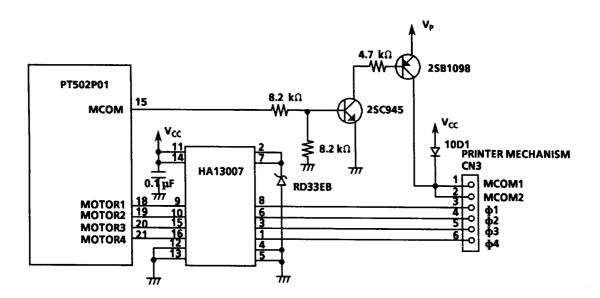

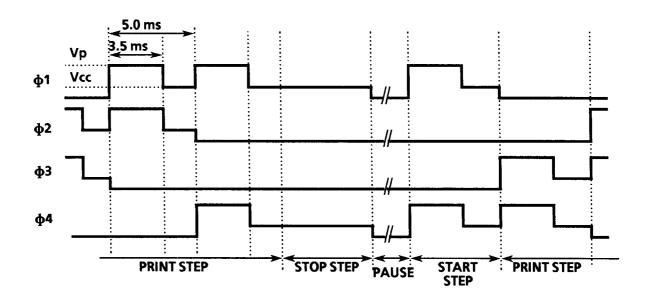

See Figures 4-9 and 4-11 for examples of motor control circuits, Figure 4-10 for the motor start/stop timing, and Figure 4-12 for the motor startup timing (under acceleration control).

# (1) Dual-source drive mode

Determine the type of transistors, diodes, and resistors according to the resistance of the motor winding resistance used in the printer mechanism.

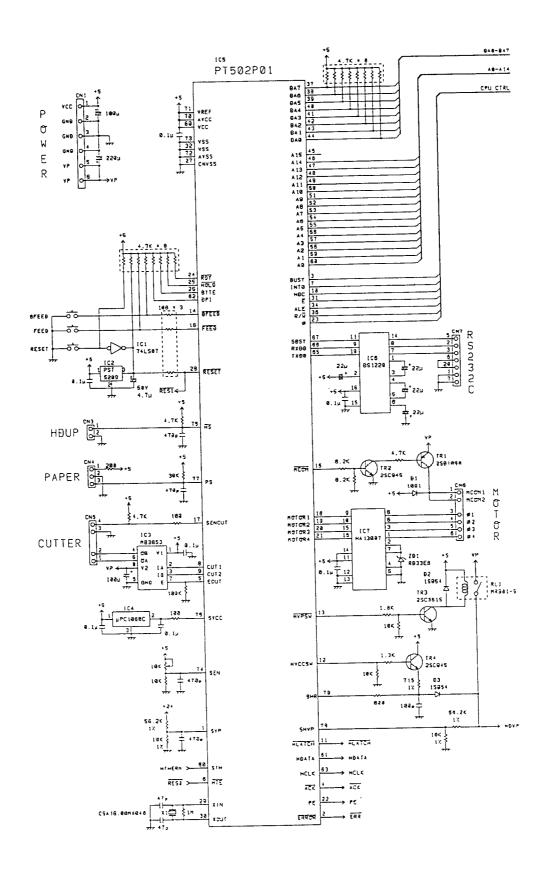

The following are recommended: HA13007 (Hitachi, Ltd.) as the motor driver IC, 2SB1098 (NEC Corp.) and 2SC945 (NEC Corp.) as the transistors, 10D1 (Nihon Inter Electronics Corp.) as the diode, and RD33EB (NEC Corp.) as the zener diode.

Figure 4-9 Sample Motor Control Circuit (Dual-source Drive Mode)

Figure 4-10 Motor Start/Stop Timing (24-V, 8 dot/mm Mechanism at Low Print Speed)

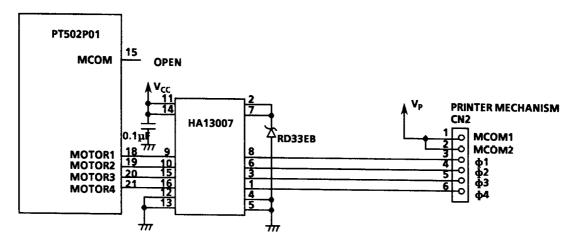

# (2) Single-source drive mode

The dual-source control block of the dual-source drive circuit may be omitted if all the following conditions are satisfied:

- maximum print speed is set to "High",

- the print mode is set to "Fixed division", and

- the CPU is to receive print data at a sufficiently higher speed than the print speed.

In this case, however, the motor may generate more heat than usual, resulting in reduced motor torque.

The recommended motor driver IC is HA13007 (Hitachi, Ltd.) and the recommended zener diode is RD33EB (NEC Corp.).

Figure 4-11 Sample Motor Control Circuit (Single-source Drive Mode)

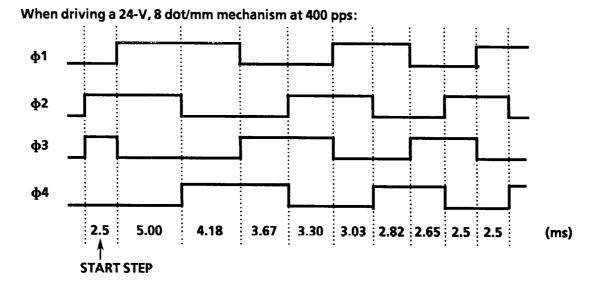

#### (3) Motor acceleration control

Only when the print speed is set to high does the PT502P01/PT500GA1 accelerate the print speed when the motor is started. By this, the PT502P01/PT500GA1 maintains constant print quality from the time the motor is started and prevents print pitch from being too small.

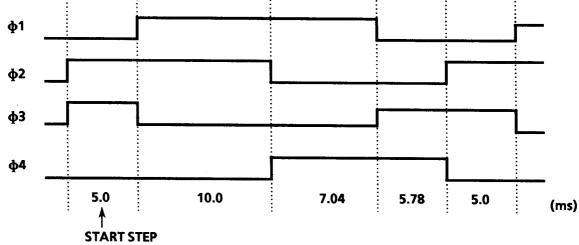

Figure 4-12 shows the acceleration control timing at the time the motor is started for both a 24-V, 8 dot/mm mechanism and a 12-V mechanism.

When driving a 12-V mechanism at 200 pps:

For both the 24-V, 8 dot/mm and 12-V mechanisms, the phase which was executed in the pause step is output again in the start step.

Figure 4-12 Motor Start Timing (Under Acceleration Control)

#### 4.12 AUTOLOADING

### What is autoloading?

The autoloading function utilizes the printer's paper detection sensor and paper feed motor to automatically load paper. When the paper is inserted into the paper inlet, the paper feed motor automatically starts and feeds the paper out from the thermal head.

The PT502P01 CPU has the autoloading function so the usual procedures for inserting the paper as described below are not required.

- 1. Raise the thermal head to the up position using head up lever.

- 2. Insert the paper into the paper inlet.

- 3. Lower the thermal head to the down position.

The design for the outer case, frame, etc., are simplified since the head-up lever is not required.

The procedures for using the autoloading function are given below.

- Make sure the PE signal (Pin 22 on the CPU) is high.

If paper is on the thermal head, the PE signal will be low. Remove the paper.

The PE signal will go to high.

- With the thermal head in the down position, insert the paper into the paper inlet until the PE signal goes to low.

The paper will be loaded automatically.

If the thermal head is in the up position, autoloading will not function.

- After autoloading has been completed, change the feed input terminal (Pin 16 on the CPU) to low to put the printer in print ready status.

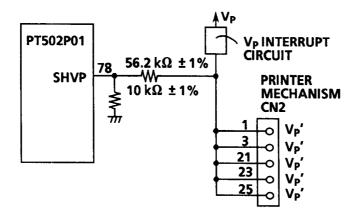

#### 4.13 HEAD CONTROL CIRCUIT

### (1) Resistance measurement circuit

The PT502P01 has a function for measuring the resistance of the thermal head. Based on the measurement, the PT502P01 determines how much energy to apply and detects problems. To use this function, the resistance measurement circuit is necessary.

### (2) Vp interrupt circuit

This circuit interrupts  $V_P$  to prevent electrolytic corrosion of the thermal head and to enable the detection of the resistance mentioned above.

Electrolytic corrosion may significantly shorten the life of the thermal head. Thermal paper ordinarily contains electrolytic material to prevent sheets from sticking to each other due to static electricity. If there is too much of this electrolytic material, high temperatures and humidity cause the material to ionize, resulting in electrolytic corrosion of the thermal head.

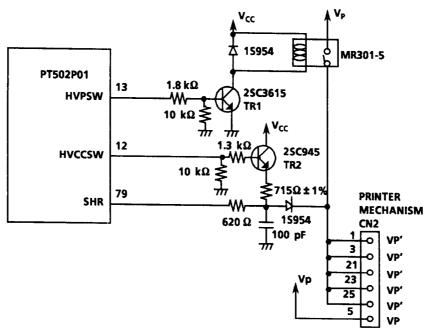

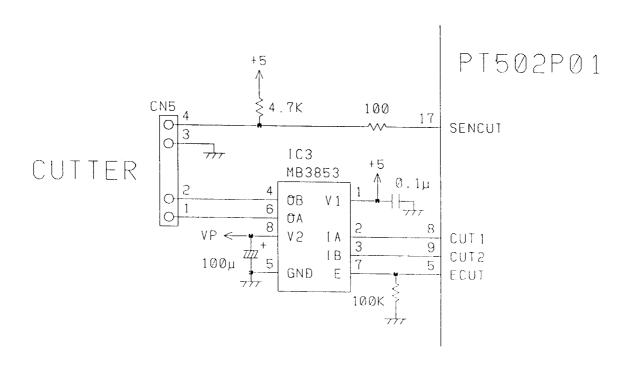

A sample resistance measurement circuit and V<sub>P</sub> interrupt circuit are shown in Figure 4-13. These circuits operate in the following manner:

- Interrupts V<sub>P</sub> at TR1. It is still necessary to apply Vp to the fifth terminal of the printer mechanism head connector.

- Turns on TR2 to apply V<sub>CC</sub> to the heat elements and measure the resistance. The head resistance is measured only once at initialization.

- When measurement ends, TR2 goes off and initialization is performed. When initialization is completed, the PT502P01 prepares for data input (standby mode). While in standby mode, Vp remains interrupted.

- When data is input and the printing conditions have been met, TR1 is turned on to start printing.

- If the PT502P01 receives no data for five seconds after printing has ended, the PT502P01 interrupts V<sub>p</sub> and enters standby mode.

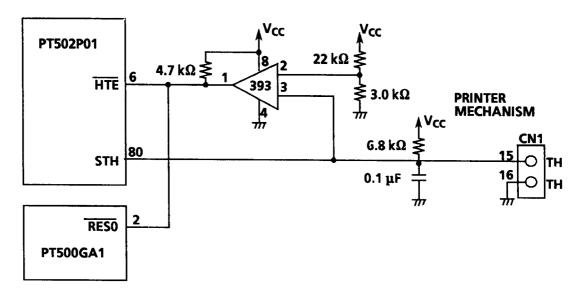

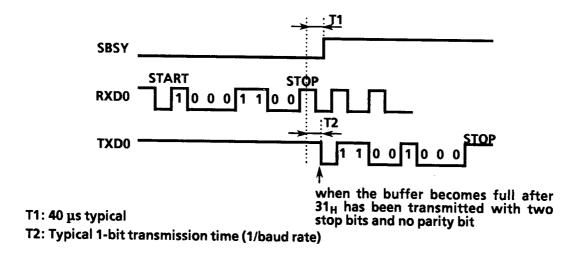

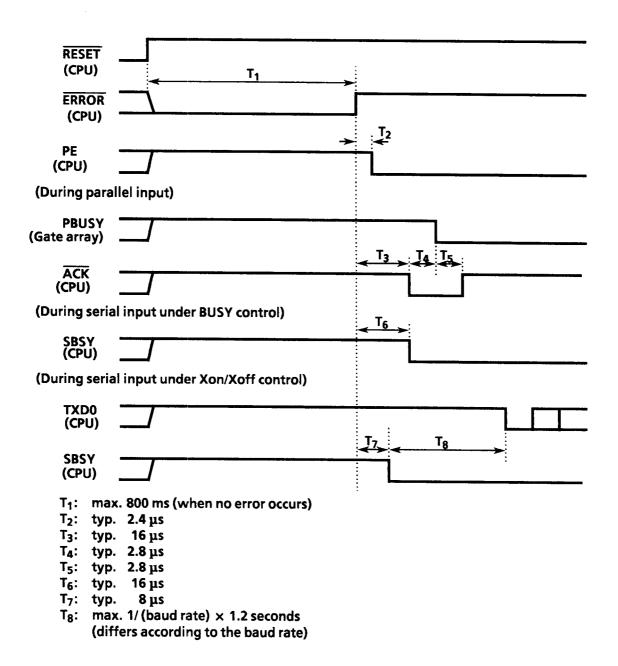

#### NOTE