# SINGLE-CHIP 8-BIT MICROCONTROLLER

#### DESCRIPTION

The MAB84X1 family of microcontrollers is fabricated in NMOS. The family consists of 5 devices:

- MAB8401 128 bytes RAM, external program memory, with 8-bit LED-driver (10mA), emulation of MAB/F8422/42\* possible

- MAB/MAF8421 2K bytes ROM/64 bytes RAM plus 8-bit LED-driver

- MAB/MAF8441 4K bytes ROM/128 bytes RAM plus 8-bit LED-driver

- MAB/MAF8461 6K bytes ROM/128 bytes RAM plus 8-bit LED-driver

Each version has 20 quasi-bidirectional I/O port lines, one serial I/O line, one single-level vectored interrupt, an 8-bit timer/event counter and on-board clock oscillator and clock circuits. Two 20-pin versions, MAB/F8422 and MAB/F8442\* are also available.

This microcontroller family is designed to be an efficient controller as well as an arithmetic processor. The instruction set is based on that of the MAB8048. The microcontrollers have extensive bit handling abilities and facilities for both binary and BCD arithmetic.

For detailed information see the 84XX family specification.

\* See data sheet on MAB/F8422/42.

#### Features

- 8-bit: CPU, ROM, RAM and I/O in a single 28-lead DIL package

- 2K, 4K or 6K ROM bytes plus a ROM-less version

- 64 or 128 RAM bytes

- 20 quasi-bidirectional I/O port lines

- Two testable inputs: one of which can be used to detect zero cross-over, the other is also the external interrupt input

- Single level vectored interrupts: external, timer/event counter, serial I/O

- Serial I/O that can be used in single or multi-master systems (serial I/O data via an existing port line and clock via a dedicated line)

- 8-bit programmable timer/event counter

- Internal oscillator, generated with inductor, crystal, ceramic resonator or external source

- Over 80 instructions (based on MAB8048) all of 1 or 2 cycles

- Single 5 V power supply (± 10%)

- Operating temperature ranges: 0 to + 70 °C -40 to + 85 °C

- 0 to + 70 °C MAB84X1 family -40 to + 85 °C MAF84X1 family only -40 to + 110 °C MAF84AX1 family only

#### **PACKAGE OUTLINES**

MAB8401B: 28-lead 'Piggy-back' package (with up to 28-pin EPROM on top). MAB8401WP: 68-lead plastic leaded chip-carrier (PLCC) (SOT188). MAB/MAF8421/41/61P: 28-lead DIL; plastic with internal heat spreader (SOT117). MAF84A21/41/61P: 28-lead DIL; plastic with internal heat spreader (SOT117). MAB8421/41/61T: 28-lead mini-pack; plastic (SO28; SOT136A).

#### August 1990

# 7110826 0074753 497 🔳

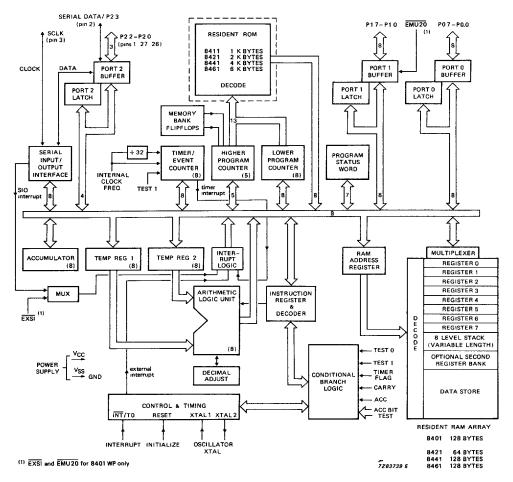

Fig. 1a Block diagram of the MAB84X1 family.

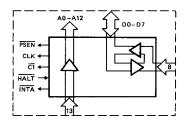

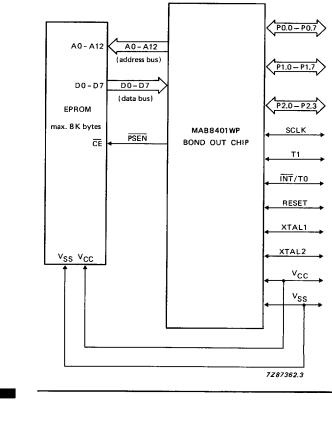

Fig. 1b Replacement for dotted part in Fig. 1a for the MAB8401WP bond-out version.

2-4 August 1990 ) ( ■ 7110826 0074754 323 ■

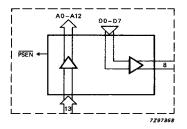

Fig. 1c Replacement of dotted part in Fig. 1a for the MAB8401B 'Piggy-back' version.

#### PINNING

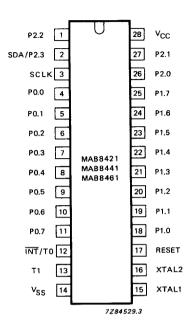

Fig. 2 Pinning diagram for mask-programmable devices MAB8421, MAB8441, MAB8461 and for MAB8401 'Piggy-back' version bottom pinning (for top pinning see Fig. 3).

#### PINNING DESIGNATION

| V <sub>SS</sub> | 14           | Ground                                                                                                                                                                                                        |

|-----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc             | 28           | Power supply, + 5 V                                                                                                                                                                                           |

| P0.0 – P0.7     | 4 11         | Port 0, 8-bit quasi-bidirectional I/O port                                                                                                                                                                    |

| P1.0 P1.7       | 18 25        | Port 1, 8-bit quasi-bidirectional I/O port with 8-bit LED driver                                                                                                                                              |

| P2.0 - P2.3     | 26, 27, 1, 2 | Port 2, 4-bit quasi-bidirectional I/O port; SDA/P2.3 is the serial data I/O in serial I/O mode                                                                                                                |

| SCLK            | 3            | Bidirectional clock for serial I/O                                                                                                                                                                            |

| INT/TO          | 12           | External interrupt input (sensitive to a negative-going edge min LOW $>$ 7 clock pulses, min HIGH $>$ 4 clock pulses), testable using the JTO or JNTO instructions.                                           |

| Τ1              | 13           | Input pin, testable using the JT1 or JNT1 instructions. It can be designated as event counter input using the STRT CNT instruction. It can also be used to detect zero cross-over of slowly moving AC inputs. |

| RESET           | 17           | Input to initialize the processor (active HIGH).                                                                                                                                                              |

| XTAL1           | 15           | Connection to timing component (crystal) that determines the frequency of the internal oscillator. It is also the input for an external clock source.                                                         |

| XTAL2           | 16           | Connection to other side of the timing component.                                                                                                                                                             |

August 1990

#### 7110826 0074755 26T 📟

#### MAB8401B (top pinning)

#### **PIN DESIGNATION**

| designation     | pin           | function             |

|-----------------|---------------|----------------------|

| V <sub>SS</sub> | 14, 22        | Ground               |

| Vcc             | 1, 26–28      | Power supply, + 5 V  |

| A0–A12          | 10—3, 25,     |                      |

|                 | 24, 21, 23, 2 | Address outputs      |

| D0–D7           | 11–13,        |                      |

|                 | 15—19         | Data inputs          |

| PSEN            | 20            | Program store enable |

Fig. 3 Pinning diagram for MAB8401B 'Piggy-back' version top pinning (for bottom pinning see Fig. 2); to access a 2732 or 2764 EPROM.

#### Note

Access times for ROMS/EPROMS to be below 1  $\mu$ s.

Fig. 3a Connection of EPROM to 'Piggy-back' package MAB8401B.

Single-chip 8-bit microcontroller

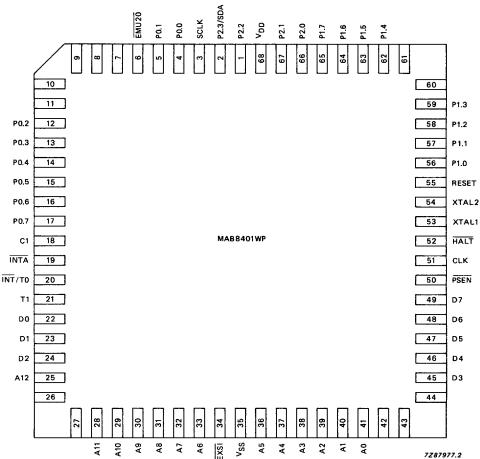

#### CHIP CARRIER DESIGNATION

| designation     | pad no.      | function .                                                                                                 |

|-----------------|--------------|------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub> | 35           | Ground                                                                                                     |

| Vcc             | 68           | Power supply, + 5 V                                                                                        |

| P0.0 – P0.7     | 4—5, 12—17   | Port 0, 8-bit quasi-bidirectional I/O port                                                                 |

| P1.0 - P1.7     | 56—59, 62—65 | Port 1, 8-bit quasi-bidirectional I/O port with 8-bit LED driver                                           |

| P2.0 P2.3       | 66, 67, 1, 2 | <b>Port 2,</b> 4-bit quasi-bidirectional I/O port; SDA/P2.3 is the serial data I/O in serial I/O mode      |

| SCLK            | 3            | Bidirectional clock for serial I/O                                                                         |

| INT/TO          | 20           | External interrupt input (sensitive to a negative-going edge), testable using the JTO or JNTO instructions |

2-7

### 7110826 0074757 032 🔳

| MAB84X1<br>MAF84X1<br>MAF84AX1<br>FAMILY |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Τ1                                       | 21                 | Input pin, testable using the JT1 or JNT1 instructions. It can be designated as event counter input using the STRT CNT inctruction. It can also be used to detect zero cross-over of slowly moving a.c. inputs.                                                                                                                                                                                                                                                                                                 |

| RESET                                    | 55                 | Input to initialize the processor (active HIGH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XTAL1                                    | 53                 | Connection to timing component (e.g. crystal) that determines<br>the frequency of the internal oscillator. It is also the input for an<br>external clock source.                                                                                                                                                                                                                                                                                                                                                |

| XTAL2                                    | 54                 | Connection to other side of the timing component                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EXSI                                     | 34                 | External serial I/O interrupt (active-LOW) for emulation of MAB/F8422/42.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

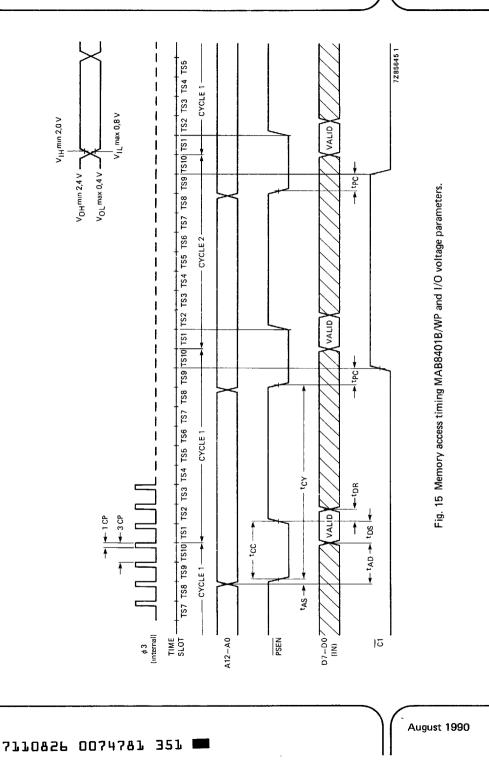

| A0-A12                                   | 41—36, 33—28<br>25 | Program memory address outputs (active HIGH); A0 = LSB,<br>A12 = MSB. Address output change after begin $\phi$ 3 of TS8.                                                                                                                                                                                                                                                                                                                                                                                        |

| D0D7                                     | 22–24, 45–49       | Data input lines (active HIGH) used for reading external program<br>memory. D0 = LSB, D7 = MSB,                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CLK                                      | 51                 | Clock output buffered from XTAL2. On the positive-going edge the (internal) $\phi$ clock goes HIGH.                                                                                                                                                                                                                                                                                                                                                                                                             |

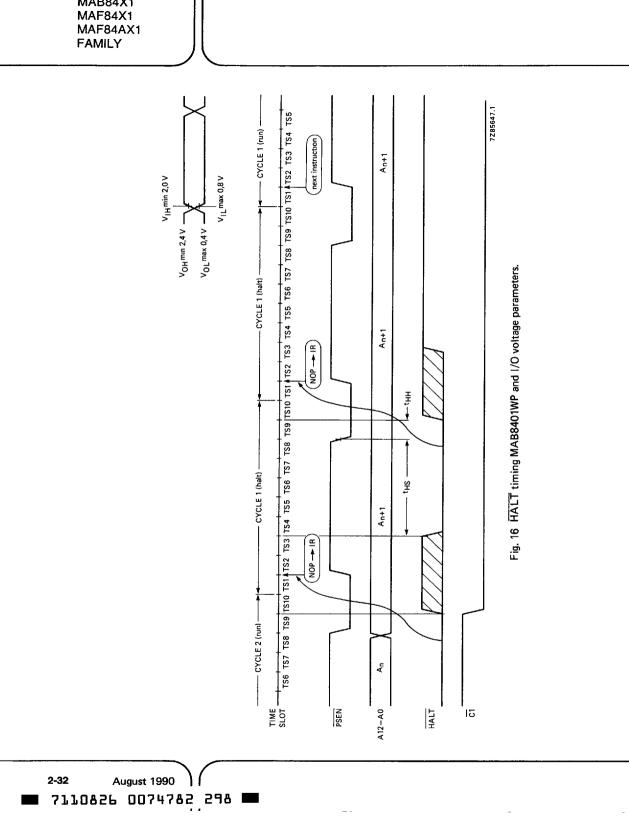

| PSEN                                     | 50                 | Program store enable. This signal is used for enabling the external EPROM (e.g. on the 'Piggy-back' version). For emulation, it enables the emulation memory and it indicates machine cycles. Active LOW during TS9, *TS10 of each machine cycle and TS1 of the following machine cycle.                                                                                                                                                                                                                        |

| <del>C1</del>                            | 18                 | Cycle 1 indication output (active LOW). During emulation, this signal indicates the opcode fetch cycle (useful for external instruction decoding, real-time trace). Active from start of TS10 of the cycle preceding cycle 1, until the start of TS10 of cycle 1.                                                                                                                                                                                                                                               |

| HALT                                     | 52                 | Halt input (active LOW). If activated, the current instruction is<br>finished and the microcontroller stops execution (HALT mode).<br>The next program counter address is available on the address bus.<br>Program counter and timer/event counter are no longer updated.<br>The serial I/O finishes the current transmit/receive action and<br>goes into the idle state. Interrupts are <i>not</i> sampled in the HALT<br>mode, they are only sampled when the microcontroller is running.                     |

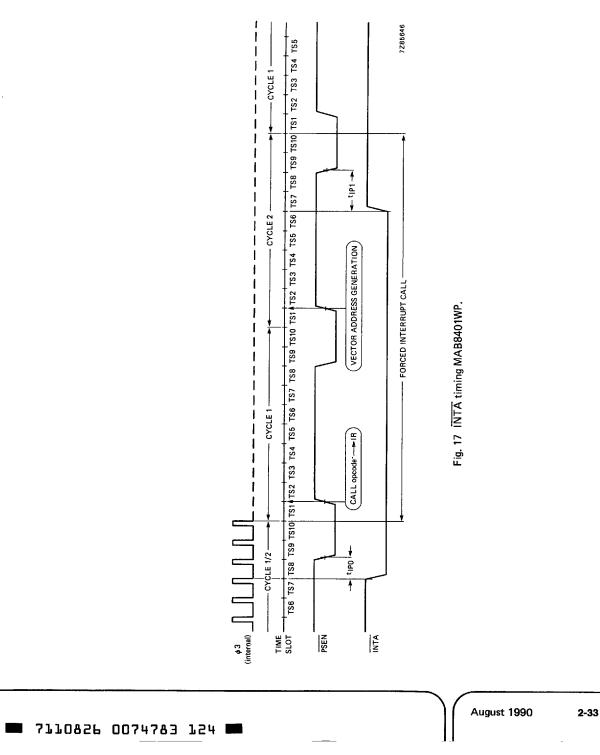

| INTA                                     | 19                 | Interrupt routines can be single-stepped as a normal program.<br>Interrupt acknowledge output (active LOW). It indicates any<br>interrupt acception. Active from start of TS8 of the interrupted<br>cycle, until start of TS7 of the second cycle of the (internally<br>forced 'CALL vector address' instruction. During INTA active,<br>the address bus shows the address that has been saved in the stack<br>(return address); the C1 output indicates opcode fetch cycles as<br>if a user CALL was executed. |

| EMU20                                    | 6                  | Emulate 20-pin version MAB/F8422/42 (active-LOW).                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

\* TS = Time slot, where 10 TS = 1 cycle.

■ 7110826 0074758 T79 ■ 2-8 August 1990

FUNCTIONAL DESCRIPTION (for more detail see 84XXX family specification)

#### Bond-out version MAB8401WP

The bond-out version is a microcontroller that contains no on-board ROM, but has all address and data lines brought out to access an external ROM or EPROM. Thus, this version has more pins than the standard microcontrollers with on-board ROM. It has all the features of the other members of the MAB84X1 family, including emulation facilities for the MAB/F8422/42 (20-pin version). It can address 8K bytes of external ROM. The RAM has 128 bytes.

#### Piggy-back version MAB8401B

The Piggy-back version is a special package that has standard pinning to the bottom which facilitates insertion as a mask-programmed device. An EPROM is mounted on top in an additional socket. Thus, the total package height is greater than the standard DIL package. Emulation of the 8422/42 is not possible.

#### Program and data memory

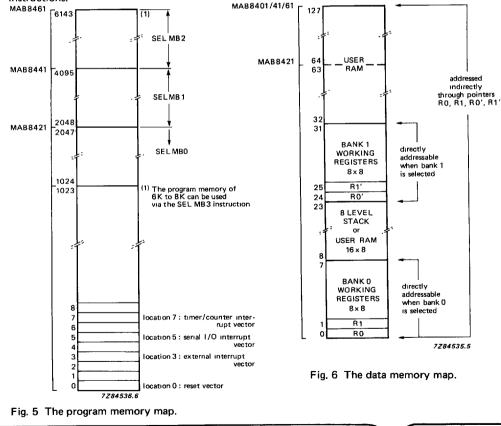

The program memory (ROM) is mask-programmed at our factory. Because the MAB84X1 family offers a range of ROM capacities to suit the application, ROM expansion is not required. Figure 5 shows the program memory map. Program memory is arranged in banks of 2K bytes, that are selected by SEL MB instructions.

# 7110826 0074759 905 🛲

August 1990

#### FUNCTIONAL DESCRIPTION (continued)

The data memory (RAM) consists of 64 or 128 bytes (8-bit words). All locations are indirectly addressable using RAM pointer registers and up to 16 designated location can be addressed directly. The memory also includes an 8-level program counter stack addressed by a 3-bit stack pointer. Figure 6 shows the data memory map.

#### **On-chip peripheral functions**

In addition to the CPU and memories, an interrupt system, I/O facilities, and an 8-bit timer/event counter are integrated on-chip to assist the CPU in repetitions, complicated or time-critical tasks. The I/O facilities include the I/O pins, parallel ports and a serial I/O port, consisting of a data line SDA shared with a parallel port line (P2.3), and a dedicated clock line SCLK.

#### I/O facilities

The MAB84XX family has 23 I/O lines arranged as:

- Two parallel ports of 8 lines (P0.0-P0.7, P1.0-P1.7). Each line of Port 1 can sink 10 mA.

- A parallel port of 4 lines (P2.0-P2.3).

- A serial I/O consisting of a data line shared with a parallel port line (P2.3) and a separate clock line SCLK;

- An external interrupt and test input INT/TO, which when used as a test input can be tested by the conditional jump instructions JTO or JNTO;

- A test input T1, which can alter program sequences when tested by conditional jump instructions JT1 or JNT1. T1 can also be used as an input to the timer/event counter or to detect zero cross-over of slowly moving AC signals.

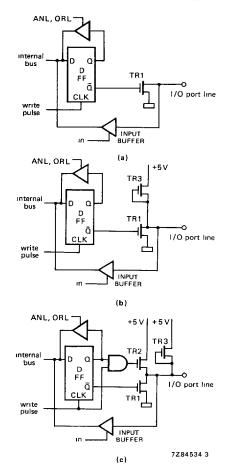

All parallel port lines are available in three optional output configurations (except P2.3 - option 1 only):

- Option 1; open drain output without pull-up transistor (Fig. 7(a))

- Option 2; open drain output with pull-up transistor (Fig. 7(b))

- Option 3; push-pull output with pull-up transistor (Fig. 7(c))

If the inputs and outputs on a port are mixed (mixed-mode), the inputs should be options 1 or 2 but not option 3. This prevents cross-currents via TR2 and an external connection to ground, while switching the output on the same port and in parallel, masking the inputs with logic 1s.

The MAB84X1 family serial I/O interface has been designed to eliminate the heavy processing load imposed upon a normal microcontroller performing serial data transfer. Whereas a normal microcontroller must regularly monitor the serial data bus for the presence of data, the serial I/O interface detects, receives and converts the serial data stream into a parallel format without interrupting the execution of the current program. An interrupt is sent to the microcontroller only when a complete byte is received. Then, the microcontroller reads the data byte in one instruction. Likewise, for transmission, the serial I/O interface performs parallel to serial conversion and subsequent serial output of the data and the microcontroller is only interrupted in the execution of its programmed tasks when a complete byte has been transmitted. The design of the serial I/O interface allows any number of MAB84X1 family devices and peripheral circuits with I<sup>2</sup>C bus compatibility to be interconnected by the two-line serial bus. This is achieved by allocating a specific 7-bit address or the 'general call' address.

Address recognition is performed by the interface hardware so that the microcontroller need only be interrupted when a valid address is received. This saves significant processing time and memory space compared to a conventional microcontroller with a software serial interface. When the address facility is not required, for instance in a system with only two microcontrollers, direct data transfer is possible. In multi-master systems, an automatically invoked arbitration procedure prevents two or more devices transmitting simultaneously.

| 7110 | 826 0074    |       |  |

|------|-------------|-------|--|

| 2-10 | August 1990 | • ) ( |  |

Fig. 7 Quasi-bidirectional I/O interface with (a) open drain output without pull-up transistor, (b) open drain output with pull-up transistor, (c) push-pull output with pull-up transistor.

#### Serial I/O interface

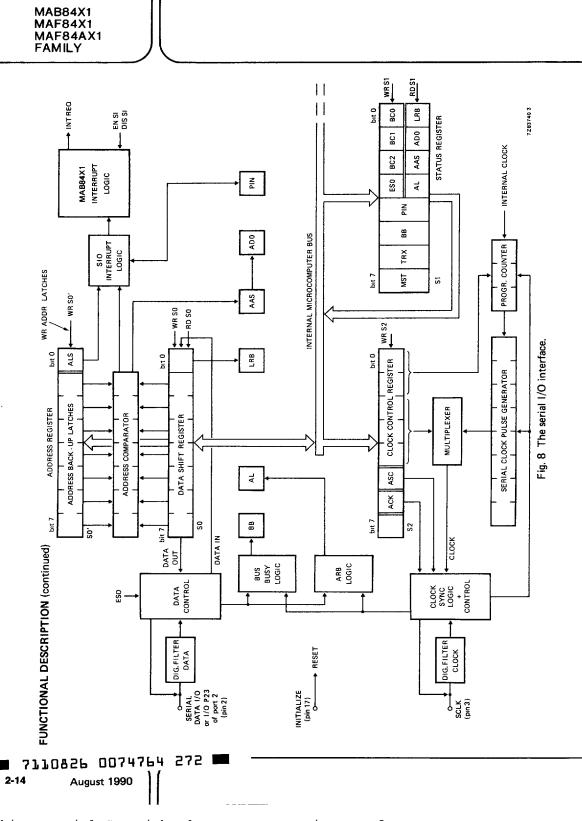

Figure 8 shows the serial I/O interface. The clock line of the serial bus has exclusive use of pin 3 (SCLK) while the data line shares pin 2 (serial data) with the I/O line P2.3 of port 2. When the serial I/O is enabled, P2.3 is disabled as a parallel port line (P2.3 and SCLK only open drain).

The microcontroller and interface communicate via the internal microcontroller bus and the Serial Interrupt Request line. Data and information controlling the operation of the interface are stored in four registers:

- data shift register S0,

- serial I/O interface status word S1,

- serial clock control word S2,

- address register S0'

# 7110826 0074761 563 🖿

2-11

August 1990

#### FUNCTIONAL DESCRIPTION (continued)

#### Serial I/O interface (continued)

#### Data shift register SO

S0 is the shift register that converts serial data to parallel format and vice versa. A pending interrupt is generated only after a complete byte has been transmitted, or after a complete data byte, specific or general call address has been received. The most significant bit is transmitted first.

#### Serial I/O interface status word S1

S1 provides information about the state of the interface and stores interface control information from the microcontroller. The four most significant bits are common to both read and write instructions, with a separate 4 read-only control bits and 4 write-only interface status bits.

#### MST and TRX

These bits determine the operating mode of the serial I/O interface (Table 2).

| Table 1 | Operating modes of the serial I/O interface. |

|---------|----------------------------------------------|

|---------|----------------------------------------------|

| MST | TRX | mode               |

|-----|-----|--------------------|

| 0   | 0   | slave receiver     |

| 1   | 0   | master receiver    |

| 0   | 1   | slave transmitter  |

| 1   | 1   | master transmitter |

#### **BB: Bus Busy**

This bit indicates the status of the bus.

#### PIN: Pending Interrupt Not

PIN = '0' indicates that there is an interrupt pending. This causes a Serial Interrupt Request when the serial interrupt mechanism is enabled.

ESO: Enable Serial Output

The ESO flag enables/disables the serial I/O interface: ESO = logic 1 enables ESO = logic 0 disables

BC0, BC1 and BC2

These bits indicate the number of bits received or transmitted in a serial data stream.

Bits ES0, BC0, BC1 and BC2 can only be written via software.

AL: Arbitration Lost

The AL flag is set via the hardware when the serial I/O interface, as a master transmitter, loses the bus arbitration procedure.

#### AAS: Addressed As Slave

This flag is set via the hardware when the interface detects either its own address or the 'general call' address as the first byte of a transfer and if the interface has been programmed to operate in the address recognition mode.

| 71100 | 826 00747   | 762 4TT 🔳 |   | <u> </u> |  |

|-------|-------------|-----------|---|----------|--|

| 2-12  | August 1990 |           | - | _        |  |

#### AD0: Address Zero

This flag is set via the hardware after the general call address is detected when the interface is operating in the address recognition mode.

#### LRB: Last Received Bit

This contains either the last data bit received or, for a transmitting device in the acknowledge mode, the acknowledge from the receiving device.

#### Bits AL, AAS, AD0 and LRB can only be read via software.

#### Serial clock control register S2

Bits 0 to 4 of S2 are used to set the frequency of the serial clock signal. When a 4,43 MHz crystal is used, the frequency of the serial clock can be varied between 100 kHz and 720 Hz. An asymmetrical clock with a HIGH to LOW ratio of 3 to 1 is produced by setting bit 5. The asymmetrical clock allows a microcontroller more time per clock period for sampling the data line, making the timing of this action less critical. Bit 6 is used to activate the acknowledge mode of the serial 1/O. S2 is a write-only register.

#### Address register SO'

The address register contains the 7-bit address back-up latches and the bit (ALS) used to enable/disable the address recognition mode. Only when ESO = 0 can the address register be written using the MOV S0,A and MOV S0,#data instructions.

#### Serial I/O interrupt logic

The interrupt logic is enabled by the EN SI instruction and disabled by DIS SI. When the interrupt logic is enabled, a pending interrupt results in a serial I/O interrupt to the controller, causing a jump to location 5 in the ROM. When the logic is disabled, the presence of an interrupt is still indicated by the PIN bit in register S1. Therefore, an interrupt can still be serviced but a vectored interrupt will not occur.

#### Interrupt system

External events and real-time on-chip peripherals require servicing by the CPU asynchronous to the execution of any particular section of code. To tie the asynchronous activities of these functions to normal program execution, three single-level nested interrupts are provided.

Each interrupt vectors to a separate location in the program memory for its service program. Each source can be individually enabled or disabled. When more than one interrupt occurs simultaneously, their priority will be: (1) external, (2) serial I/O and, (3) timer/event counter. An additional external interrupt can be created using the timer/event counter interrupt.

#### 7110826 0074763 336 🎟

August 1990

#### Test input T1

The T1 input line can be used as:

- a test input for branch instructions,

- an input for zero voltage cross-over detection,

- an external input to the event counter.

An internal pull-up transistor is provided as a ROM mask option. This is useful when the input is from a switch or standard TTL output.

When T1 is used as a test input, the JT1 or JNT1 instructions test for a HIGH or a LOW respectively.

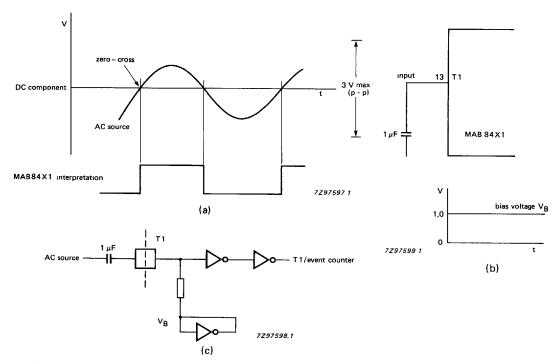

When used for zero-cross detection purposes, the T1 input must be coupled through a capacitor of typical value 1  $\mu$ F and operation carried out using the T1 input without the pull-up transistor. The maximum input voltage amplitude is 3 V (peak-to-peak), with a maximum operational frequency of 1 kHz. The T1 input has an on-chip DC offset circuit which self-biases the input to its exact switching level of 1 V. As a consequence a small change will cause a digital transition to occur. The switching level of the T1 input circuit is within the bias voltage of ± 135 mV. Upon each positive cycle on the pin, the event counter is incremented and an overflow will set the timer flag TF. Zero cross-over detection used in conjunction with the timer/event counter interrupt, is useful in thyristor control of power equipment. Figure 9 illustrates, (a) the input waveform, (b) the input diagram and (c) the on-chip self-stabilized bias.

Figure 9 Zero-cross detection circuitry; (a) input waveform, (b) input diagram, (c) on-chip self-stabilized bias.

The operation of T1 as an input to the timer/event counter is described under the heading Timer/ event counter.

7110826 0074765109 🔳

#### **High current outputs**

Ten pins are provided that can sink high currents:

-- P2.3 (serial data), pin 2

5 mA at 0,45 V (open drain),

-- SCLK, pin 3

5 mA at 0,45 V (open drain),

-- P1.0 -- P1.7 \*

10 mA at 1 V

#### Timer/event counter

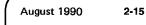

An 8-bit binary up-counter is provided. This can count external events, machine cycles divided by 32, or machine cycles directly. When used as a timer, the input to the counter is either the overflow or input of a 5-bit prescaler. When used as an event counter, LOW to HIGH transitions on T1 (pin 13) are counted. The maximum rate at which the counter may be incremented is once every machine cycle (200 kHz for a 5  $\mu$ s machine cycle). Figure 10 illustrates the timer/event counter.

Fig. 10 The timer/event counter.

|                                                                                                                                                                                         | 8021                                                                    | 8048                                                                      | 8401,<br>8421, 8441, 8461                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM capacity (bytes)<br>RAM capacity (bytes)<br>paralei 1/Ο lines<br>single inputs<br>serial 1/Ο<br>timer<br>prescaler<br>machine cycle time (μs)<br>for clock (MHz)<br>instruction set | 1K<br>64<br>8 + 8 + 4<br>1<br>no<br>8 bit<br>mod. 32<br>10<br>3<br>8021 | 1K<br>64<br>8+8+8<br>3<br>no<br>8 bit<br>mod. 32<br>2,5<br>6<br>8<br>8048 | ROMless , 2K, 4K, 6K<br>128, 64, 64, 128, 128<br>8 + 8 + 4<br>2<br>yes, 2-line multi-transmitter<br>8 bit<br>mod. 1 & mod. 32<br>5<br>6<br>8048 with omissions;<br>5 new serial I/O instructions,<br>2 new register instructions;<br>1 new control instructions;<br>1 new cond. branch instruction |

| interrupts<br>no. of pins (DIL)                                                                                                                                                         | none<br>28                                                              | 2<br>external<br>timer/<br>event counter<br>40                            | 3<br>external<br>serial I/O<br>timer/event counter<br>68 (PLCC), 28                                                                                                                                                                                                                                |

Differences between the MAB8021 and MAB8048 microcontrollers, and the MAB84X1 family.

\* P1.0 to P1.7 may be connected in parallel if their logic outputs are always the same.

7110826 0074766 045 I 2-16 August 1990

#### **OSCILLATOR CIRCUITRY**

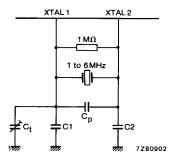

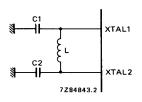

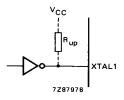

Clock frequency is determined by using the internal oscillator or by connecting an external clock to XTAL1. Where the internal oscillator is used, the frequency is set by a crystal between XTAL1 and XTAL2, or by a ceramic resonator or an inductor, each with two associated capacitors, between XTAL1 and XTAL2 (see Fig. 11a). A machine cycle consists of 10 states, each state being 3 oscillator periods. The common 6 MHz crystal gives a 5  $\mu$ s machine cycle. The MAB84X1 family has dynamic logic, and therefore, for adequate refreshing the oscillator frequency must be at least 1 MHz.

- 1. Crystal AT-cut

- 2. Ceramic resonator C1 = C2 = 27 pFC1 may be trimmed  $C_p \le 6,75 \text{ pF}$  (parasitic capacitance)

LC oscillator timing

| frequency | C1 = C2 | L      |

|-----------|---------|--------|

| 3,0 MHz   | 33 pF   | 100 μH |

| 4,0 MHz   | 33 pF   | 56 μH  |

| 4,4 MHz   | 33 pF   | 47 μH  |

| 5,0 MHz   | 33 pF   | 33 µH  |

| 6,0 MHz   | 33 pF   | 22 µH  |

Fig. 11b LC pi-network.

Fig. 11c External drive.

Drive XTAL1 Leave XTAL2 open Driver may be high-speed CMOS or any TTL  $t_{\rm r}, t_{\rm f} < 10 \, {\rm ns}$

# 7110826 0074767 781 🔳

2-17

August 1990

#### PROGRAM STATUS WORD

The program status word (PSW) is an 8-bit word in the CPU which stores information about the current status of the microcontroller (Fig. 12). The PSW bits are:

bits 0, 1 and 2 - stack pointer bits (SP<sub>0</sub>, SP<sub>1</sub>, SP<sub>2</sub>);

| •     |                                                                                                                                                      |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | — prescaler select (PS); 0 = divide-by-32; 1 = no prescaling;                                                                                        |

| bit 4 | <ul> <li>working register bank select (RBS):</li> <li>0 = register bank 0</li> <li>1 = register bank 1;</li> </ul>                                   |

| bit 5 | — not used (1);                                                                                                                                      |

| bit 6 | <ul> <li>auxiliary carry (AC):<br/>half-carry bit is generated by an ADD instruction and used by the decimal adjust<br/>instruction DA A;</li> </ul> |

| bit 7 | <ul> <li>carry (CY):<br/>the carry flag indicates that the previous operation has resulted in an overflow of<br/>the accumulator.</li> </ul>         |

| saved in the stack |    |   | he stad |    | stac | k pou | nter  |  |

|--------------------|----|---|---------|----|------|-------|-------|--|

| CY                 | AC | 1 | RBS     | PS | SP2  | SP1   | SPO   |  |

| 7<br>MSB           | 6  | 5 | 4       | 3  | 2    | 1     | LSB   |  |

|                    |    |   |         |    |      | 7Z    | 89149 |  |

Fig. 12 Program status word,

All bits can be read using MOV A, PSW and bit 3 can be written with MOV PSW, A.

Bits 6 and 7 can be set and cleared by CPU operation. Bit 4 is changed by the SEL RB instruction, bit 3 by the MOV PSW, A instruction, and bits 0, 1 and 2 by the CALL, RET or RETR instructions and when an interrupt occurs. Bits 4, 6 and 7 are stored in the program counter stack during sub-routine and interrupt calls. These bits are restored to the PSW with RETR (return and restore) instruction.

Note: The RET instruction has no restore feature and should not be used at the end of an interrupt because this would leave any further interrupts disabled.

The MAB84X1 family has arithmetic, logical and branching capabilities. The DA A, SWAP A, and XCHD instructions simplify BCD arithmetic and the handling of nibbles. The MOVP A,@A instruction permits efficient table look up from the current ROM page.

The conditional branch logic within the processor enables several conditions, internal and external to the processor, to be tested by the user's program. Table 2 lists the conditional branch instructions used to change the program execution sequence. The DJNZ instruction decrements a designated register and branches if the contents are not zero. This instruction makes the register an efficient program loop counter. The JMPP @A instruction allows multiway branches to destinations indirectly addressed by the contents of the accumulator.

#### Table 2 Conditional branches

| TEST                 | JUMP CONDITION | JUMP INSTRUCTION |

|----------------------|----------------|------------------|

| accumulator          | 0 or non-zero  | JZ, JNZ          |

| accumulator bit test | 1              | JB0 to JB7       |

| carry flag           | 0 or 1         | JNC, JC          |

| timer overflow flag  | 1              | JTF              |

| test input INT       | 0 or 1         | JNTO, JTO        |

| test input T1        | 0 or 1         | JNT1, JT1        |

| test flag O          | 1              | JF0              |

| test flag 1          | 1              | JF1              |

| register             | non-zero       | DJNZ             |

#### RESET

A positive-going signal on the RESET input:

- sets the program counter to zero,

- selects location 0 of memory bank 0, and register bank 0,

- sets the stack pointer to zero ('000'B); pointing to RAM address 8,

- disable the interrupts (external, timer and serial I/O),

- stops the timer/event counter, then sets it to zero,

- sets the timer prescaler to divide-by-32,

- resets the timer flag,

- sets all ports to logic '1' (input mode),

- sets the serial I/O to slave receiver mode and disables serial I/O.

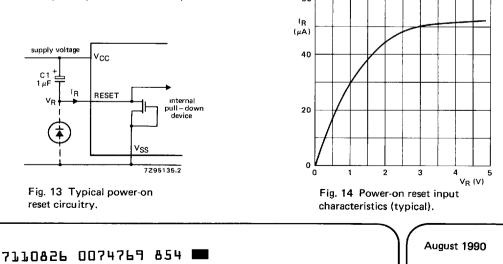

Automatic reset at power-up may be obtained by connecting the RESET pin to V<sub>CC</sub> through a 1  $\mu$ F capacitor C, together with a diode to V<sub>SS</sub> (cathode to RESET pin). This arrangement is satisfactory, if both the voltage (V<sub>CC</sub>) rise time and the oscillator start-up time do not exceed either 1 or 10 ms respectively.

The power-on reset circuit is shown in figure 13. At power-on the current drawn by RESET commences to charge the capacitor C. The difference between this increasing capacitor voltage and  $V_{CC}$  is known as  $V_{RESET}$ . The charging circuit is designed to hold  $V_{RESET}$  above the lower threshold of a Schmitt trigger arrangement long enough to effect a complete reset. The minimum time required; is the oscillator start-up time plus two machine cycles.

#### INSTRUCTION SET

The instruction set consists of over 80 one and two byte instructions and is based on the MAB8048 instruction set. New instructions include those for serial I/O operation and memory bank selection. Program code efficiency is high because all ROM locations on a 256 byte page require only a single byte address.

Table 3 gives the instruction set of the MAB84X1 family and Table 4 shows the instruction map. The following symbols and abbreviations are used.

Note: During development of software on a PMDS or similar system, it is important to ensure that no jump instruction (direct or indirect), outreaches the final address range of the device.

| symbol | description                                         |

|--------|-----------------------------------------------------|

| A      | the accumulator                                     |

| AC     | the auxiliary carry flag                            |

| addr   | program memory address (11-bits)                    |

| Bb     | bit designation (b = $0-7$ )                        |

| BS     | the bank switch                                     |

| С      | carry flag                                          |

| CLK    | clock signal                                        |

| CNT    | event counter                                       |

| D      | nibble designation (4-bits)                         |

| DBF    | program memory bank flip-flop                       |

| data   | number or expression (8-bits)                       |

| F0, F1 | flags 0 and 1                                       |

| I      | interrupt                                           |

| ĪNT    | external interrupt                                  |

| Р      | 'in-page' operation designation                     |

| Рр     | port designation ( $p = 1, 2 \text{ or } 4-7$ )     |

| PSW    | program status word                                 |

| Rr     | register designation ( $r = 0, 1 \text{ or } 0-7$ ) |

| SP     | stack pointer                                       |

| Т      | timer                                               |

| TF     | timer flag                                          |

| T0, T1 | test 0 and 1 inputs                                 |

| #      | immediate data prefix                               |

| @      | indirect address prefix                             |

| \$     | current value of program counter                    |

| ←      | is replaced by                                      |

| ⇔      | is exchanged with                                   |

■ 7110826 0074770 576 ■ 2-20 August 1990

|                      | ADD A, Rr<br>ADD A, @Rr | (hex.)   | bytes/<br>cycles | description                                   | function                                                                      |         | notes        |

|----------------------|-------------------------|----------|------------------|-----------------------------------------------|-------------------------------------------------------------------------------|---------|--------------|

|                      | D A. @Br                | 6*       | 1/1              | Add register contents to A                    | (A)+-(A) + (Rr)                                                               | r = 07  | -            |

|                      | )                       | 60<br>61 | 1/1              | Add RAM data, addressed by Rr, to A           | (A)+(A) + ((R0))<br>(A)+(A) + ((R1))                                          |         | -            |

| AD<br>AD             | ADD A, #data            | 03 data  | 2/2              | Add immediate data to A                       | (A)←(A) + data                                                                |         | -            |

| AD AD                | ADDC A, Rr              | 7*       | 1/1              | Add carry and register contents to A          | (A)←(A) + (Rr) + (C)                                                          | r = 0–7 | -            |

| <                    | ADDC A, @Rr             | 70<br>71 | 1/1              | Add carry and RAM data, addressed by Rr, to A | (A)←(A) + ((R0)) + (C)<br>(A)←(A) + ((R1)) + (C)                              |         | -            |

| 2                    | ADDC A, #data           | 13 data  | 2/2              | Add carry and immediate data to A             | (A)←(A) + data + (C)                                                          |         | <del>.</del> |

| AN                   | ANL A, Rr               | <u>ئ</u> | 1/1              | 'AND' Rr with A                               | (A)←(A) AND (Rr)                                                              | r = 0–7 |              |

|                      | ANL A, @Rr              | 50<br>51 | 1/1              | 'AND' RAM data, addressed by Rr, with A       | (A)←(A) AND ((R0))<br>(A)←(A) AND ((R1))                                      |         |              |

|                      | ANL A, #data            | 53 data  | 2/2              | 'AND' immediate data with A                   | (A)←(A) AND data                                                              |         |              |

|                      | ORL A, Rr               | 4*       | 1/1              | 'OR' Rr with A                                |                                                                               | r = 0–7 |              |

| <del>8</del><br>мпрр | ORL A, @Rr              | 40<br>41 | 1/1              | 'OR' RAM data, addressed by Rr, with A        | () ()                                                                         |         |              |

|                      | ORL A, #data            | 43 data  | 2/2              | 'OR' immediate data with A                    | (A)←(A) OR data                                                               |         |              |

| XR                   | XRL A, Rr               | *0       | 1/1              | 'XOR' Rr with A                               | (A)+-(A) XOR (Rr)                                                             | r = 0–7 |              |

| X                    | XRL A, @Rr              | 00<br>10 | 1/1              | 'XOR' RAM, addressed by Rr, with A            | (A)←(A) XOR ((R0))<br>(A)←(A) XOR ((R1))                                      |         |              |

| XR                   | XRL A, #data            | D3 data  | 2/2              | 'XOR' immediate data with A                   | (A)←(A) XOR data                                                              |         |              |

| INC A                | A C                     | 17       | 1/1              | increment A by 1                              | (A)←(A) + 1                                                                   |         |              |

| DE                   | DEC A                   | 07       | 1/1              | decrement A by 1                              | (A)++(A) - 1                                                                  |         |              |

| CLR A                | A A                     | 27       | 1/1              | clear A to zero                               | (A)+0                                                                         |         | _            |

| CPL A                | Α-                      | 37       | 1/1              | one's complement A                            | (A)←NOT(A)                                                                    |         |              |

| RL A                 | ٩                       | E7       | 1/1              | rotate A left                                 | (A <sub>n</sub> + 1)←(A <sub>n</sub> )<br>(A <sub>n</sub> )←(A <sub>7</sub> ) | n = 0–6 |              |

7110826 0074771 402 🔳

Г

MAB84X1 MAF84X1 MAF84AX1 FAMILY

2-21

August 1990

| notes            | 5                                                                                   |                                                                               | 2                                                                                      | 2                |                   |                             |                                      |                          |                                       |                                                           |                           |                                                        |                                       |                                                                |                                                          |                                  | m                              |                                   |

|------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|-------------------|-----------------------------|--------------------------------------|--------------------------|---------------------------------------|-----------------------------------------------------------|---------------------------|--------------------------------------------------------|---------------------------------------|----------------------------------------------------------------|----------------------------------------------------------|----------------------------------|--------------------------------|-----------------------------------|

|                  | n = 0—6                                                                             | n = 0—6                                                                       | n = 0–6                                                                                |                  |                   | r = 07                      |                                      |                          | r = 0–7                               |                                                           |                           |                                                        | r = 0–7                               |                                                                |                                                          |                                  |                                |                                   |

| function         | (A <sub>n</sub> + 1)←A <sub>n</sub><br>(A <sub>0</sub> )←(C), (C)←(A <sub>7</sub> ) | (A <sub>n</sub> )←(A <sub>n</sub> + 1)<br>(A <sub>7</sub> )←(A <sub>0</sub> ) | (A <sub>n</sub> )←(A <sub>n</sub> + 1)<br>(A <sub>7</sub> )←(C), (C)←(A <sub>0</sub> ) |                  | (A4-7)⇔(A0-3)     | (A)←(Rr)                    | (A)←((R0))<br>(A)←((R1))             | (A)←data                 | (Rr)←(A)                              | ((R0))+(A)<br>((R1))+(A)                                  | (Rr)←data                 | ((R0))←data<br>((R1))←data                             | (A)↔(Rr)                              | (A)↔((R0))<br>(A)↔((R1))                                       | (A0_3)↔((R00_3))<br>(A0_3)↔((R10_3))                     | (A)+(PSW)                        | (PSW3)←(A3)                    | (PC0_7)←(A), (A)←((PC))           |

| description      | rotate A left through carry                                                         | rotate A right                                                                | rotate A right through carry                                                           | decimal adjust A | swap nibbles of A | move register contents to A | move RAM data, addressed by Rr, to A | move immediate data to A | move accumulator contents to register | move accumulator contents to RAM location addressed by Rr | move immediate data to Rr | move immediate data to RAM location<br>addressed by Rr | exchange accumulator contents with Rr | exchange accumulator contents with<br>RAM data addressed by Rr | exchange lower nibbles of A and RAM data addressed by Rr | move PSW contents to accumulator | move accumulator bit 3 to PSW3 | move indirectly addressed data in |

| bytes/<br>cycles | 1/1                                                                                 | 1/1                                                                           | 1/1                                                                                    | 1/1              | 1/1               | 1/1                         | 1/1                                  | 2/2                      | 1/1                                   | 1/1                                                       | 2/2                       | 2/2                                                    | 1/1                                   | 1/1                                                            | 1/1                                                      | 1/1                              | 1/1                            | 1/2                               |

| opcode<br>(hex.) | F7                                                                                  | 77                                                                            | 67                                                                                     | 57               | 47                | *<br>Ľ                      | F0<br>F1                             | 23 data                  | A*                                    | A0<br>A1                                                  | B* data                   | B0 data<br>B1 data                                     | 2*                                    | 20<br>21                                                       | 30<br>31                                                 | c7                               | D7                             | A3                                |

| mnemonic         | RLC A                                                                               | RR A                                                                          | RRC A                                                                                  | DA A             | SWAP A            | MOV A, Rr                   | MOV A, @Rr                           | MOV A, #data             | MOV Rr, A                             | MOV @Rr, A                                                | MOV Rr, #data             | MOV @Rr, #data                                         | XCH A, Rr                             | XCH A, @Rr                                                     | XCHD A, @Rr                                              | MOV A, PSW                       | MOV PSW, A                     | MOVP A, @A                        |

|                  | (.tnoɔ                                                                              | ) яот                                                                         | אחרא                                                                                   | lus              | SA                |                             |                                      |                          |                                       |                                                           | S3/                       | /OM A                                                  | TA,                                   | a                                                              |                                                          |                                  |                                |                                   |

|                  | 0074<br>August í                                                                    | 772                                                                           | эч <sup>,</sup>                                                                        |                  |                   | -                           |                                      |                          |                                       |                                                           |                           |                                                        |                                       |                                                                |                                                          |                                  |                                |                                   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 5                                     |                         |                                              |                         |                                      |                                      |                                 |                                   |                                            |                                                                           |                                                                   |                                    |                                   |                                    | -                                  | -                                   |                                       |                                      |                                      |                                      | 4                                    |                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------|----------------------------------------------|-------------------------|--------------------------------------|--------------------------------------|---------------------------------|-----------------------------------|--------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------|-----------------------------------|------------------------------------|------------------------------------|-------------------------------------|---------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|-------------------------------------|

| CLR C       97       1/1       clear carry bit         INC Rr       1*       1/1       increment register by 1         INC Rr       1*       1/1       increment register by 1         INC @Rr       1*       1/1       increment register by 1         INC @Rr       1*       1/1       increment RAM data, addressed by Rr, by 1         DEC @Rr       C*       1/1       by 1       decrement register by 1         JMP addr       C*       1/1       by 1       decrement RAM data, addressed by Rr, by 1         JMP addr       C*       1/1       decrement RAM data, addressed by Rr, by 1       decrement RAM data, addressed by Rr, by 1         JMP @A       B3       1/2       unconditional jump within a 2K bank         JMP @A       B3       1/2       unconditional jump within a 2K bank         JMP @A       B3       1/2       unconditional jump within a 2K bank         JMP @A       B3       1/2       unconditional jump within a 2K bank         JMP @A       B3       1/2       unconditional jump within a 2K bank         JMP @A       B3       1/2       unconditional jump within a 2K bank         JMP @A       B3       1/2       unconditional jump within a 2K bank         JNNZ @Fr, addr       < |                                         | r = 0–7                 |                                              | r = 07                  |                                      |                                      |                                 | r = 0 - 7                         | -<br>-                                     |                                                                           |                                                                   | b = 0–7                            |                                   |                                    |                                    |                                     |                                       |                                      |                                      |                                      |                                      |                                     |

| CLR C97 $1/1$ CPL CA7 $1/1$ INC Rr $1 \times 10$ $1/1$ INC @Rr $1 \times 10$ $1/1$ INC @Rr $10$ $1/1$ DEC Rr $C \times 10$ $1/1$ DEC Rr $C \times 10$ $1/1$ DEC Rr $C \times 10$ $1/1$ DEC Rr $C \times 100$ $1/1$ DEC @Rr $C \times 100$ $1/1$ DEC Rr $C \times 100$ $1/1$ DEC @Rr $C \times 100$ $1/1$ JMP addr $\bullet$ 4 address $2/2$ JMPP @A $B3$ $1/2$ JMPP @A $B3$ $1/2$ JMPP @A $E \times address$ $2/2$ JNZ Rr, addr $E \times address$ $2/2$ JBb addr $E \times address$ $2/2$ JS addr $E \times address$ $2/2$ JZ addr $A \ge address$ $2/2$ JNC addr $S \oplus address$ $2/2$ JNC addr $S \oplus address$ $2/2$ JNT0 addr $S \oplus address$ $2/2$ JNT0 addr $S \oplus address$ $2/2$ JNT1 addr $5 \oplus address$ $2/2$ JNT1 addr $16 \oplus address$ $2/2$ JNTF addr $06 \oplus address$ $2/2$ JNTF addr $06 \oplus address$ $2/2$                                                                                                                                                                                                                                                                                                                                                                                   | (C)←0<br>(C)←NOT(C)                     | (Rr)+(Rr) + 1           | ((R0))+((R0)) + 1<br>((R1))+((R1)) + 1       | (Rr)←(Rr) – 1           | ((R0))→((R0)) −1<br>((R1))→((R1)) −1 | (PC8-10)←addr8-10<br>(PC0-7)←addr0-7 | (PC <sub>11−12</sub> )←MBFF 0−1 | (Br)+(Br) - 1                     | if (Rr) not zero (PC <sub>0-7</sub> )←addr | ((R0))+((R0)) −1<br>if ((R0)) not zero (PC <sub>0−7</sub> )+addr          | ((R1))+((R1)) − 1<br>if ((R1)) not zero (PC <sub>0−7</sub> )+addr | if b = 1: (PC <sub>0</sub> 7)←addr | if C = 1: (PC <sub>0</sub> )←addr | if C = 0: (PC <sub>07</sub> )←addr | if A = 0: (PC <sub>07</sub> )←addr | if A ≠ 0: (PC <sub>0−7</sub> )←addr | if T0 = 1: (PC <sub>0-7</sub> ) ←addr | if T0 = 0: {PC <sub>0−7</sub> }+addr | if T1 = 1: (PC <sub>0−7</sub> )←addr | if T1 = 0: (PC <sub>0−7</sub> )+addr | if TF = 1: (PC <sub>0</sub> _7)←addr | if TF = 0: (PC <sub>07</sub> )←addr |

| CLR C     97       CPL C     A7       INC Rr     1*       INC Rr     1*       INC @Rr     10       INC @Rr     10       INC @Rr     10       DEC Rr     C       DEC Rr     C       JMP addr     • 4 address       JMPP @A     • 33       JMPP @A     • 2 address       JMPP @A     E1 address       JMPP @A     E3 address       JNZ addr     E2 address       JZ addr     66 address       JZ addr     56 address       JNT1 addr     56 address       JNT1 addr     56 address       JNTF addr     16 address       JNTF addr     06 address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | clear carry bit<br>complement carry bit | increment register by 1 | increment RAM data, addressed by Rr,<br>by 1 | decrement register by 1 | decrement RAM data, addressed by Rr, | unconditional jump within a 2K bank  | indirect iumo within a nave     | decrement Br by 1 and iumn if not | zero to addr                               | decrement RAM data, addressed by Rr,<br>by 1 and jump if not zero to addr |                                                                   | jump to addr if Acc. bit $b = 1$   | jump to addr if $C = 1$           | jump to addr if $C = 0$            | jump to addr if $A = 0$            | jump to addr if A is NOT zero       | jump to addr if $TO = 1$              | jump to addr if $T0 = 0$             | jump to addr if T1 = 1               | jump to addr if $T1 = 0$             | jump to addr if Timer Flag = 1       | jump to addr if Timer Flag = 0      |

| CLLR C<br>CPL C<br>INC Rr<br>INC Rr<br>DEC Rr<br>DEC Rr<br>JMP addr<br>JMPP @A<br>JMPP @A<br>JNNZ @Rr, addr<br>JNNZ addr<br>JT addr<br>JT addr<br>JTT addr<br>JNT1 addr<br>JNT1 addr<br>JNT1 addr<br>JNT7 addr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1/1                                     | 1/1                     | 1/1                                          | 1/1                     | 1/1                                  | 2/2                                  | 117                             | 2/2                               |                                            | 2/2                                                                       |                                                                   | 2/2                                | 2/2                               | 2/2                                | 2/2                                | 2/2                                 | 2/2                                   | 2/2                                  | 2/2                                  | 2/2                                  | 2/2                                  | 2/2                                 |

| CLR C<br>CPL C<br>INC Rr<br>INC @Rr<br>DEC Rr<br>JMPP @A<br>JMPP @A<br>JMPP @A<br>DJNZ @Rr, a<br>JNNZ addr<br>JZ addr<br>JT addr<br>JT1 addr<br>JT1 addr<br>JT1 addr<br>JTT addr<br>JNT1 addr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97<br>A7                                | 1*                      | 10                                           | <u>ٹ</u>                | 0.0                                  | • 4 address                          | B3                              | E* address                        |                                            |                                                                           | E1 address                                                        | 2 address                          | F6 address                        |                                    |                                    |                                     |                                       |                                      |                                      |                                      |                                      |                                     |

| BRANCH REGISTER FLAGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | INC Rr                  |                                              |                         |                                      | JMP addr                             | JMPP @A                         | DJNZ Rr. addr                     |                                            |                                                                           |                                                                   |                                    |                                   | JNC addr                           | JZ addr                            | JNZ addr                            | JT0 addr                              | JNT0 addr                            | JT1 addr                             | JNT1 addr                            | JTF addr                             | JNTF addr                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59AJ7                                   |                         | яэтг                                         | :I93                    | B                                    |                                      |                                 |                                   |                                            |                                                                           | н                                                                 | DNA                                | ัยย                               |                                    |                                    |                                     |                                       |                                      |                                      |                                      |                                      |                                     |

7110826 0074773 285 페

г

#### MAB84X1 MAF84X1 MAF84AX1 FAMILY

2-23

August 1990

|                | notes            |                                                  |                                                  |                     |             |                          |                                      |                                       |                           |                            | 2<br>C                 | ى<br>م                 |                              |                              |                              |                              | 9                                          |                                   |                     | 9                            | 9                                                        |

|----------------|------------------|--------------------------------------------------|--------------------------------------------------|---------------------|-------------|--------------------------|--------------------------------------|---------------------------------------|---------------------------|----------------------------|------------------------|------------------------|------------------------------|------------------------------|------------------------------|------------------------------|--------------------------------------------|-----------------------------------|---------------------|------------------------------|----------------------------------------------------------|

|                | function         | (A)+(T)                                          | (T)+(A)                                          |                     |             |                          |                                      |                                       |                           |                            | (RBS)←0                | (RBS)←1                | (MBFF0)←0, (MBFF1)←0         | (MBFF0)←1, (MBFF1)←0         | (MBFF0)←0, (MBFF1)←1         | (MBFF0)←1, (MBFF1)←1         | ((SP))←(PC), (PSW4, 6, 7)<br>(SP)←(SP) + 1 | PC9-10)←addr8-10<br>PC07)←addr0-7 | (PC11-12)+-MBFF 0-1 | (SP)←(SP) - 1<br>(PC)←((SP)) | (SP)←(SP) - 1<br>(PSW4, 6, 7) + (PC)←((SP))              |

|                | description      | move timer/event counter contents to accumulator | move accumulator contents to timer/event counter | start event counter | start timer | stop timer/event counter | enable timer/event counter interrupt | disable timer/event counter interrupt | enable external interrupt | disable external interrupt | select register bank 0 | select register bank 1 | select program memory bank 0 | select program memory bank 1 | select program memory bank 2 | select program memory bank 3 | jump to subroutine                         |                                   |                     | return from subroutine       | return from interrupt and restore<br>bits 4, 6, 7 of PSW |

|                | bytes/<br>cycles | 1/1                                              | 1/1                                              | 1/1                 | 1/1         | 1/1                      | 1/1                                  | 1/1                                   | 1/1                       | 1/1                        | 1/1                    | 1/1                    | 1/1                          | 1/1                          | 1/1                          | 1/1                          | 2/2                                        |                                   |                     | 1/2                          | 1/2                                                      |