CMOS

Quad Multiplying 8-Bit

Digital-to-Analog Converter

#### **FEATURES**

- · On-Chip Latches for All DAC's

- Linearity Grades to ±1/8 LSB

- Single Supply Voltage (5 Volt)

- DAC's Matched to 1%

- Four Quadrant Multiplication

- Microprocessor TTL/CMOS Compatible

- Read/Write Capability for all DAC's

## **APPLICATIONS**

- Microprocessor Controlled Gain and Attenuation Circuits

- Microprocessor Controlled/Programmable Power Supplies

- Hardware Redundant Applications Requiring Data Readback

- PDIP, CDIP, PLCC & SOIC Packages Available

#### **GENERAL DESCRIPTION**

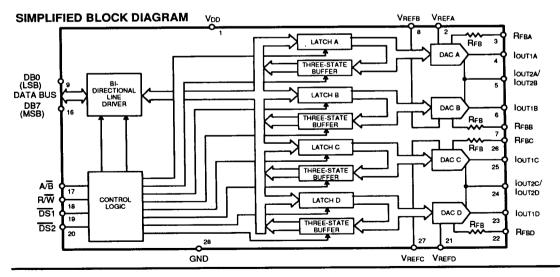

The MP7628 is a monolithic quad 8-bit digital-to-analog converter designed using Micro Power Systems' proven decoded DAC architecture featuring excellent DAC-to-DAC matching and guaranteed monotonicity.

Separate on-chip latches are provided for each DAC to allow easy microprocessor interface.

The readback function allows the user to poll or read the data latches, eliminating the need for storing information in RAM. In the event the microprocessor power supply is interrupted, it can poll the DACs to establish the last known system state.

Data is transferred into any of the four DAC data latches via common 8-bit TTL/CMOS compatible input port. Control inputs

DS1, DS2 and A/B determine which DAC is to be loaded. The MP7628's load cycle is similar to the write cycle of a random access memory and the device is bus compatible with most 8-bit microprocessors.

The device operates at +5 V power supply and dissipates less than 5mW.

All DAC's offer excellent four quadrant multiplication characteristics with a separate reference input and feedback resistor for each DAC.

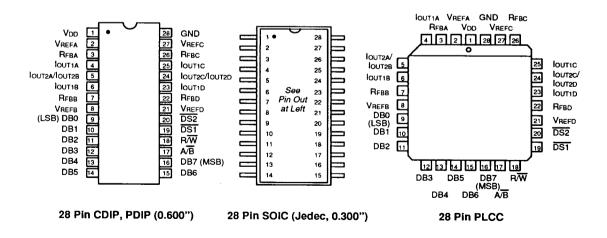

Specified for operation over the commercial / industrial (-40 to +85°C) and military (-55 to +125°C) temperature ranges, the MP7628 is available in Plastic and Ceramic dual-in-line, Plastic leaded chip carrier (PLCC) and Surface Mount (SOIC) packages.

4-179

## ORDERING INFORMATION

| Package<br>Type | Temperature<br>Range | Part No.     | Relative<br>Accuracy | Differential<br>Non-Linearity | Gain Error |  |

|-----------------|----------------------|--------------|----------------------|-------------------------------|------------|--|

| Plastic Dip     | -40 to +85°C         | MP7628JN     | ±1/2 LSB             | ±1/2 LSB                      | ±1.8% FSR  |  |

| Plastic Dip     | -40 to +85°C         | MP7628KN     | ±1/4 LSB             | ±1/4 LSB                      | ±0.9% FSR  |  |

| Plastic Dip     | -40 to +85°C         | MP7628LN     | ±1/8 LSB             | ±1/8 LSB                      | ±0.5% FSR  |  |

| SOIC            | -40 to +85°C         | MP7628JS     | ±1/2 LSB             | ±1/2 LSB                      | ±1.8% FSR  |  |

| SOIC            | -40 to +85°C         | MP7628KS     | ±1/4 LSB             | ±1/4 LSB                      | ±0.9% FSR  |  |

| SOIC            | -40 to +85°C         | MP7628LS     | ±1/8 LSB             | ±1/8 LSB                      | ±0.5% FSR  |  |

| PLCC            | ~40 to +85°C         | MP7628JP     | ±1/2 LSB             | ±1/2 LSB                      | ±1.8% FSR  |  |

| PLCC            | -40 to +85°C         | MP7628KP     | ±1/4 LSB             | ±1/4 LSB                      | ±0.9% FSR  |  |

| PLCC            | -40 to +85°C         | MP7628LP     | ±1/8 LSB             | ±1/8 LSB                      | ±0.5% FSR  |  |

| Ceramic Dip     | -40 to +85°C         | MP7628AD     | ±1/2 LSB             | ±1/2 LSB                      | ±1.8% FSR  |  |

| Ceramic Dip     | -40 to +85°C         | MP7628BD     | ±1/4 LSB             | ±1/4 LSB                      | ±0.9% FSR  |  |

| Ceramic Dip     | -40 to +85°C         | MP7628CD     | ±1/8 LSB             | ±1/8 LSB                      | ±0.5% FSR  |  |

| Ceramic Dip     | -55 to +125°C        | MP7628SD     | ±1/2 LSB             | ±1/2 LSB                      | ±1.8% FSR  |  |

| Ceramic Dip     | -55 to +125°C        | MP7628SD/883 | ±1/2 LSB             | ±1/2 LSB                      | ±1.8% FSR  |  |

| Ceramic Dip     | -55 to +125°C        | MP7628TD     | ±1/4 LSB             | ±1/4 LSB                      | ±0.9% FSR  |  |

| Ceramic Dip     | -55 to +125°C        | MP7628TD/883 | ±1/4 LSB             | ±1/4 LSB                      | ±0.9% FSR  |  |

| Ceramic Dip     | -55 to +125°C        | MP7628UD     | ±1/8 LSB             | ±1/8 LSB                      | ±0.5% FSR  |  |

| Ceramic Dip     | -55 to +125°C        | MP7628UD/883 | ±1/8 LSB             | ±1/8 LSB                      | ±0.5% FSR  |  |

## **PIN CONFIGURATIONS**

# PIN OUT DEFINITIONS

| PIN NO. | NAME              | DESCRIPTION                  |  |  |  |

|---------|-------------------|------------------------------|--|--|--|

| 1       | Voo               | Power Supply                 |  |  |  |

| 2       | VREFA             | Reference Voltage for DAC A  |  |  |  |

| 3       | RFBA              | Feedback Resistor for DAC A  |  |  |  |

| 4       | loutia            | Current Output 1 DAC A       |  |  |  |

| 5       | IOUT2A/<br>IOUT2B | Current Output 2 DAC A/DAC B |  |  |  |

| 6       | IOUT1B            | Current Output 1 DAC B       |  |  |  |

| 7       | RFBB              | Feedback Resistor for DAC B  |  |  |  |

| 8       | VREFB             | Reference Voltage for DAC B  |  |  |  |

| 9       | DB0               | Data Bit 0 (LSB)             |  |  |  |

| 10      | DB1               | Data Bit 1                   |  |  |  |

| 11      | DB2               | Data Bit 2                   |  |  |  |

| 12      | DB3               | Data Bit 3                   |  |  |  |

| 13      | DB4               | Data Bit 4                   |  |  |  |

| 14      | DB5               | Data Bit 5                   |  |  |  |

| 15      | DB6               | Data Bit 6                   |  |  |  |

| 16      | DB7               | Data Bit 7 (MSB)             |  |  |  |

| 17      | A/B               | DAC Selection                |  |  |  |

| 18      | ₽√W               | Read/Write                   |  |  |  |

| 19      | DS1               | Control 1                    |  |  |  |

| 20      | DS2               | Control 2                    |  |  |  |

| 21      | VREFD             | Reference Voltage for DAC D  |  |  |  |

| 22      | RFBD              | Feedback Resistor for DAC D  |  |  |  |

| 23      | loutid            | Current Output 1 DAC D       |  |  |  |

| 24      | lout2C/<br>lout2D | Current Output 2 DAC C/DAC D |  |  |  |

| 25      | loutic            | Current Output 1 DAC C       |  |  |  |

| 26      | RFBC              | Feedback Resistor for DAC C  |  |  |  |

| 27      | VREFC             | Reference Voltage for DAC C  |  |  |  |

| 28      | GND               | Ground                       |  |  |  |

# **MP7628**

# ELECTRICAL CHARACTERISTICS (VDD = + 5 V, VREF = +10 V unless otherwise noted)

| Parameter                          | Symbol       | Min | 25°C      | Max          | Tmin to | Tmax<br>Max  | 11-70-          | T                                                                                         |

|------------------------------------|--------------|-----|-----------|--------------|---------|--------------|-----------------|-------------------------------------------------------------------------------------------|

|                                    | Symbol       | Min | Тур       | мах          | Min     | мах          | Units           | Test Conditions/Comments                                                                  |

| STATIC PERFORMANCE (1)             |              |     |           |              |         |              |                 | FSR = Full Scale Range                                                                    |

| Resolution (All Grades)            | N            | 8   |           |              | 8       |              | Bits            |                                                                                           |

| Integral Non-Linearity             | INL          |     |           |              |         |              | LSB             | End Point Linearity Spec.                                                                 |

| (Relative Accuracy)                |              |     |           |              |         |              |                 |                                                                                           |

| J, A, S<br>K, B, T                 |              |     |           | ±1/2         |         | ±1/2         |                 |                                                                                           |

| L, C, U                            |              |     |           | ±1/4<br>±1/8 |         | ±1/4<br>±1/8 |                 |                                                                                           |

| Differential New Line and C        | DNL          |     |           |              |         | 10           | l               |                                                                                           |

| Differential Non-Linearity J. A. S | UNL          |     |           | ±1/2         |         | ±1/2         | LSB             | All grades monotonic over full                                                            |

| К, В, Т                            |              |     |           | ±1/4         |         | ±1/4         |                 | temperature range.                                                                        |

| L, C, U                            |              |     |           | ±1/8         |         | ±1/8         |                 |                                                                                           |

| Gain Error                         | GE           |     |           |              |         |              | % FSR           | Using Internal RFB                                                                        |

| J, A, S                            |              |     |           | ±1.5         |         | ±1.8         | 78 7 511        | Digital Inputs = VINH                                                                     |

| К, В, Т                            |              |     |           | ±0.8         |         | ±0.9         |                 | = 19.111 mpsts = 1 mm                                                                     |

| L, C, U                            |              |     |           | ±0.4         |         | ±0.5         |                 |                                                                                           |

| Gain Temperature Coefficient (2)   | TCGE         |     |           |              |         | 2            | ppm/°C          | ΔGain/ΔTemperature                                                                        |

| Power Supply Rejection Ratio       | PSRR         |     |           | ±200         |         | ±400         | ppm/%           | ΔGain/ΔV <sub>DO</sub>   ΔV <sub>DO</sub> = ± 5%<br>Digital Inputs = V <sub>INH</sub>     |

| Output Leakage Current (all)       | lout1        |     |           | ±50          |         | ±200         | nA              | Digital Inputs = VINL                                                                     |

| REFERENCE INPUT                    |              |     |           |              |         |              |                 |                                                                                           |

| Voltage Range (2)                  |              |     |           | ±20          |         | +20          | v               |                                                                                           |

| Input Resistance                   | Rin          | 12  |           | 28           | 12      | 28           | кΩ              |                                                                                           |

| DIGITAL INPUTS                     |              |     |           |              |         |              |                 |                                                                                           |

| Logic Thresholds                   |              |     |           |              |         |              |                 |                                                                                           |

| VINH                               |              | 2.4 |           |              | 2.4     |              | lv l            |                                                                                           |

| VINL                               |              |     |           | 0.8          |         | 0.8          | v               |                                                                                           |

| Input Leakage Current              | ILKG         |     |           | ±1           |         | ±10          | μА              |                                                                                           |

| Input Capacitance (2)              | Cin          |     | 3         |              |         |              | рF              |                                                                                           |

| DATA BUS OUTPUTS                   |              |     |           |              |         |              |                 |                                                                                           |

| Output Capacitance (2)             | Соит         |     | 7         |              |         |              | рF              |                                                                                           |

| Input Leakage Current              | llkg         |     |           | ±1           |         | ±10          | μА              |                                                                                           |

| ANALOG OUTPUTS                     |              |     |           |              |         |              |                 |                                                                                           |

| Propagation Delay (2)              |              | 500 |           |              | 750     |              | ns              | From digital input to 90% of final analog output current                                  |

| Output Capacitance (2)             |              |     |           |              |         | 4            | _               |                                                                                           |

| Glitch Energy (2)                  | Cout<br>Cout | 160 | 120<br>80 |              | 440     |              | pF<br>pF<br>nVs | DAC Inputs all 1's DAC Inputs all 0's Typical for code transition from all 0's to all 1's |

# **ELECTRICAL CHARACTERISTICS (CON'T)**

| Parameter                           | Symbol | Min | 25°C<br>Typ Max | Tmin to<br>Min | Tmax<br>Max | Units | Test Conditions/Comments              |

|-------------------------------------|--------|-----|-----------------|----------------|-------------|-------|---------------------------------------|

| POWER SUPPLY (5)                    |        |     |                 |                |             |       |                                       |

| Functional Voltage Range (2)        | VDD    | 4.5 | 5.5             | 4.5            | 5.5         | v     |                                       |

| Supply Current                      | loo    |     | 50              |                | 50          | μА    | All digital inputs = 0 V or all = 5 V |

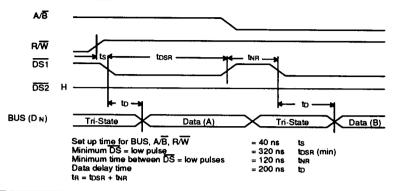

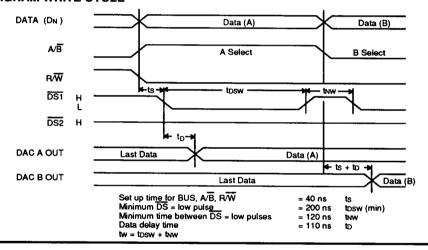

| SWITCHING<br>CHARACTERISTICS (2, 4) |        |     |                 |                |             |       |                                       |

| Data Write Time                     | tw     | 320 |                 | 400            |             | ns    |                                       |

| Write Strobe Req.                   | tosw   | 200 |                 | 250            |             | ns    |                                       |

| Data Hold Time                      | tohld  | 40  |                 | 50             |             | ns    |                                       |

| Data Read Time                      | tR     | 480 |                 | 600            |             | ns    |                                       |

| Tri-State Hold Time                 | ttshd  | 240 |                 | 300            |             | ns    |                                       |

| Read Strobe Req.                    | tosa   | 320 |                 | 400            |             | ns    |                                       |

#### NOTES:

- (1) Full Scale Range (FSR) is 10V for unipolar mode and ±10V for bipolar.

- (2) Guaranteed but not production tested.

- (3) Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

- (4) See timing diagram.

- (5) Specified values guarantee functionality. Refer to other parameters for accuracy.

Specifications are subject to change without notice

# ABSOLUTE MAXIMUM RATINGS (1, 2) (TA = +25°C unless otherwise noted)

| V <sub>DD</sub> to GND +7 V                                         | Storage Temperature65°C to +150°C               |

|---------------------------------------------------------------------|-------------------------------------------------|

| Digital Input Voltage to GND (2) GND -0.5 to V <sub>DD</sub> +0.5 V | Lead Temperature (Soldering, 10 seconds) +300°C |

| louts, louts to GND (2) GND -0.5 to V <sub>DD</sub> +0.5 V          | Package Power Dissipation Rating to 75°C        |

| V <sub>REF</sub> to GND                                             | CDIP, PDIP, SOIC, PLCC 450mW                    |

| V <sub>RFB</sub> to GND                                             | Derates above 75°C 6mW/°C                       |

## NOTES:

- (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- (2) Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies.

## **TIMING DIAGRAM READ CYCLE**

## **TIMING DIAGRAM WRITE CYCLE**

## **MODE SELECTION TABLE**

| DS1 | DS2 | A/B | R⁄W | MODE  | DAC     |

|-----|-----|-----|-----|-------|---------|

| L   | Н   | Н   | L   | WRITE | A       |

| L   | Н   | L   | L   | WRITE | В       |

| Н   | Ļ   | н   | lι  | WRITE | Ċ       |

| H   | L   | L   | L   | WRITE | lο      |

| L   | н   | н   | Н   | READ  | A       |

| L   | н   | L   | н   | READ  | В       |

| н : | L   | н   | Н   | READ  | l c     |

| 1 H | L   | L   | н   | READ  | D       |

| L   | L   | н   | Ļ   | WRITE | A&C     |

| L   | L   | L   | L   | WRITE | B&D     |

| H   | н   | Х   | х   | HOLD  | A/B/C/D |

| L   | L   | н   | н   | HOLD  | A/B/C/D |

| L.  | Ł   | L   | н   | HOLD  | A/B/C/D |

L = LOW STATE H = HIGH STATE X = DON'T CARE

#### INTERFACE LOGIC INFORMATION

DAC Selection: All DAC latches share a common 8-bit input port. The control inputs  $\overline{DS1}$ ,  $\overline{DS2}$  A $\overline{B}$  select which DAC can accept data from the input port.

Mode Selection: Inputs  $\overline{DS}$  and  $R/\overline{W}$  control the operating mode of the selected DAC. See Mode Selection Table on the previous page.

Write Mode: When  $\overline{DS}$  and  $R\overline{W}$  are both low the selected DAC is in the write mode. The input data latches of the selected

DAC are transparent and its analog output responds to activity on DB0-DB7.

Hold Mode: The selected DAC latch retains the data which was present on DB0-DB7 just prior to  $\overline{\rm DS}$  and  $R/\overline{\rm W}$  assuming a high state. Both analog outputs remain at the values corresponding to the data in their respective latches.

Read Mode: When  $\overline{\rm DS}$  is low and  ${\rm R/W}$  is high, the selected DAC is in the read mode and the data held in the appropriate latch is outputed to the data bus.

APPLICATION NOTES

Refer to Applications Section for Additional Information