## MB81C4256A-70L/-80L/-10L

## CMOS 1,048,576 BIT FAST PAGE MODE DYNAMIC RAM

## CMOS 256K x 4 Bits Fast Page Mode DRAM

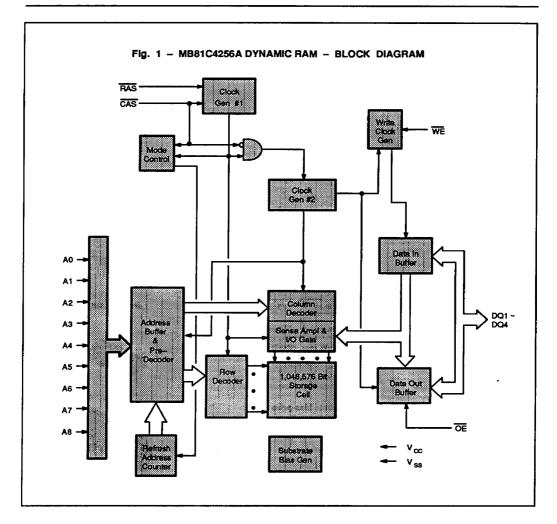

The Fujitsu MB81C4256A is a CMOS, fully decoded dynamic RAM organized as 256K words x 4 bits. The MB81C4256A has been designed for mainframe memories, buffer memories, and video image memories requiring high speed and high bandwidth output with low power dissipation, as well as for memory systems of battery operated computers requiring very low power dissipation.

Fujitsu's advanced three-dimensional stacked capacitor cell technology gives the MB81C4256A high  $\alpha$ -ray soft error immunity and extended refresh time. CMOS technology is used in the peripheral circuits to provide low power dissipation and high speed operation.

### **Features**

| Perameter                                | MB81C4256A<br>-70L | MB81C4256A<br>-80L | MB814256A<br>-10L |

|------------------------------------------|--------------------|--------------------|-------------------|

| RAS Access Time                          | 70 ns max.         | 80 ns max.         | 100 ns max.       |

| Random Cycle Time                        | 140 ns min.        | 155 ns min.        | 180 ns min.       |

| Address Access Time                      | 35 ns max.         | 40 ns max.         | 50 ns max.        |

| CAS Access Time                          | 20 ns max.         | 20 ns max.         | 25 ns mex.        |

| Fast Page Mode Cycle Time                | 50 ns min.         | 55 ns min.         | 65 ns min.        |

| Low Power Dissipation  Operating Current | 374 mW max.        | 341 mW max.        | 297 mW max.       |

| Standby Current                          | 5.5 mW max. (TT    | L level)/1.4 mW ma | x. (CMOS level)   |

- 262,144 words x 4 bits organization

- Silicon gate, CMOS, 3D—Stacked Capacitor Cell

- All input and output are TTL compatible

- 512 refresh cycles every 64 ms

- Early write or OE controlled write capability

- RAS only, CAS-before-RAS, or Hidden Refresh

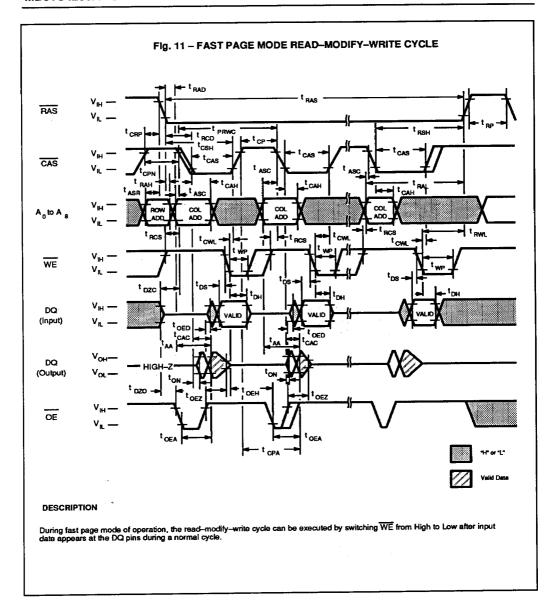

- Fast Page Mode, Read-Modify-Write capability

- On-chip substrate bias generator for high performance

## Absolute Maximum Ratings (See Note)

| Parameter                                |                       | Symbol                             | Value       | Unit |

|------------------------------------------|-----------------------|------------------------------------|-------------|------|

| Voltage at any pin relative t            | o V <sub>SS</sub>     | V <sub>IN</sub> , V <sub>OUT</sub> | -1 to +7    | ٧    |

| Voltage of V <sub>CC</sub> supply relati | ve to V <sub>SS</sub> | Vcc                                | -1 to +7    | ٧    |

| Power Dissipation                        |                       | PD                                 | 1.0         | W    |

| Short Circuit Output Curren              | t                     | _                                  | 50          | mA   |

| Storage Temperature                      | Ceramic               | T <sub>STG</sub>                   | -55 to +150 | °c   |

|                                          | Plastic               |                                    | -55 to +125 |      |

Note: Permanent device damage may occur if absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operation sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Copyright © 1990 by FWITSU LIMITED and Fulltsu Microelectronics, Inc.

This device contains circuitry to protect the inputs against damage due to high static votages or electric fletch. However, is advised that normal precautions be taken to avoid application any voltage higher than maximum rated voltages to this high impedance circuit.

## CAPACITANCE (T<sub>A</sub>= 25°C, f = 1MHz)

| Parameter                            | Symbol           | Тур | Max | Unit |

|--------------------------------------|------------------|-----|-----|------|

| Input Capacitance, A0 to A8          | C <sub>IN1</sub> | _   | 5   | pF   |

| Input Capacitance, RAS, CAS, WE, OE  | C <sub>IN2</sub> | _   | 5   | ρF   |

| Input/Output Capacitance, DQ1 to DQ4 | C <sub>DO</sub>  |     | 6   | рF   |

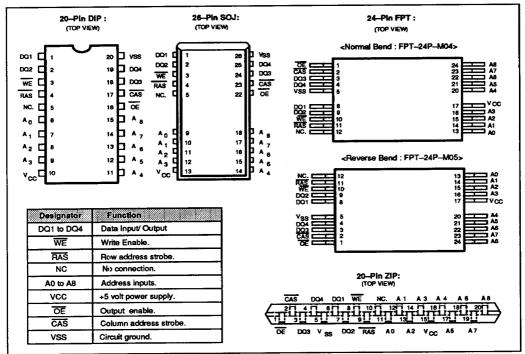

## PIN ASSIGNMENTS AND DESCRIPTIONS

# RECOMMENDED OPERATING CONDITIONS

| Parameter                      | Notes    | Symbol          | Min  | Тур | Mex | Unit | Amblent<br>Operating Temp |

|--------------------------------|----------|-----------------|------|-----|-----|------|---------------------------|

|                                |          | Vœ              | 4.5  | 5.0 | 5.5 | V    |                           |

| Supply Voltage                 | Ш        | V <sub>SS</sub> | 0    | 0   | 0   | · ·  |                           |

| Input High Voltage, all inputs | <u>-</u> | VIH             | 2.4  | _   | 6.5 | v    | 0 °C to +70 °C            |

| Input Low Voltage, all inputs  | <u>-</u> | VIL             | 2.0  | _   | 0.8 | v    |                           |

| Input Low Voltage, DQ(*)       | 1        | VILD            | -1.0 | _   | 0.8 | v    |                           |

<sup>\*:</sup> Undershoots of up to -2.0 volts with a pulse width not exceeding 20ns are acceptable.

## **FUNCTIONAL OPERATION**

### **ADDRESS INPUTS**

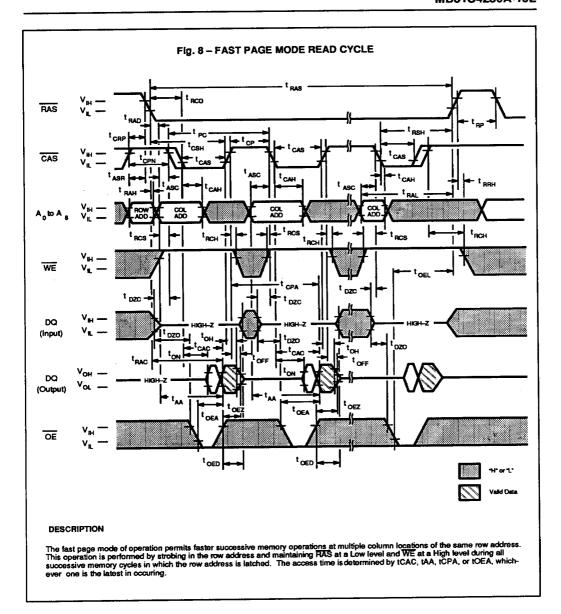

Eighteen input bits are required to decode any four of 1,048,576 celladdresses in the memory matrix. Since only nine address bits are available, the column and row inputs are separately strobed by CAS and RAS as shown in Figure 1. First, nine row address bits are input on pins AD—through—A8 and latched with the row address strobe (RAS) then, nine column address bits are input and latched with the column address strobe (CAS). Both row and column addresses must be stable on or before the fallingedge of CAS and RAS, respectively. The address latches are of the flow—through type; thus, address information appearing after taxi (min)+ tr is automatically treated as the column address.

### WRITE ENABLE

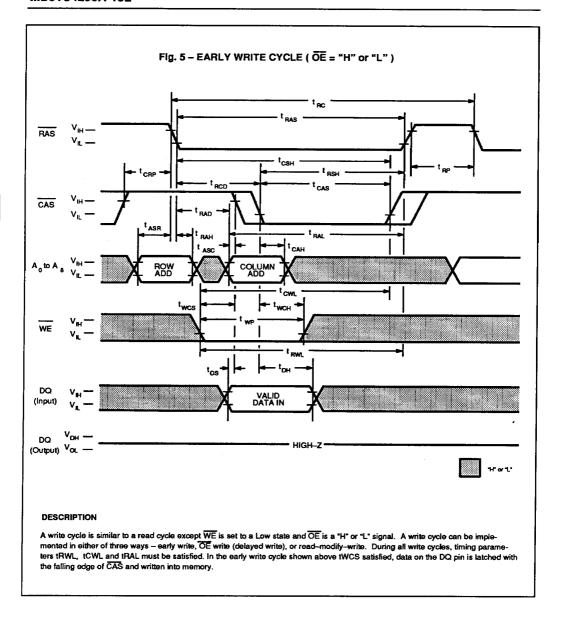

The read or write mode is determined by the logic state of WE. When WE is active Low, a write cycle is initiated; when WE is High, a read cycle is selected. During the read mode, input data is ignored.

### DATA INPUT

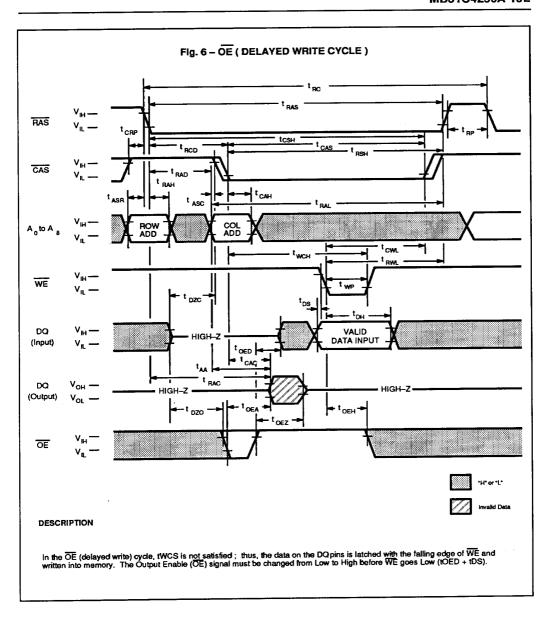

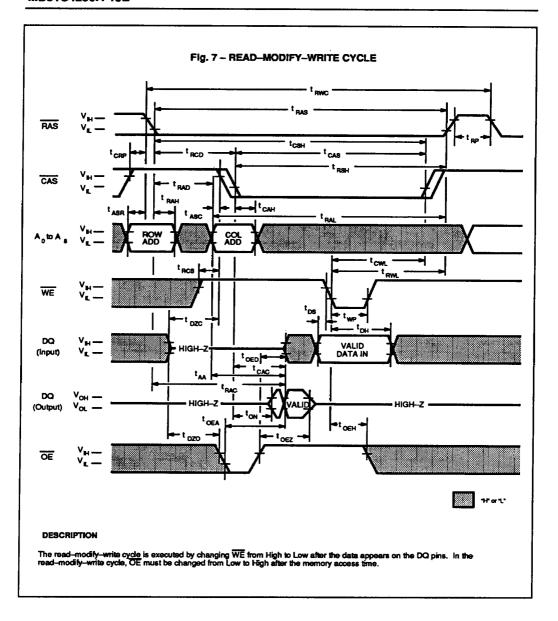

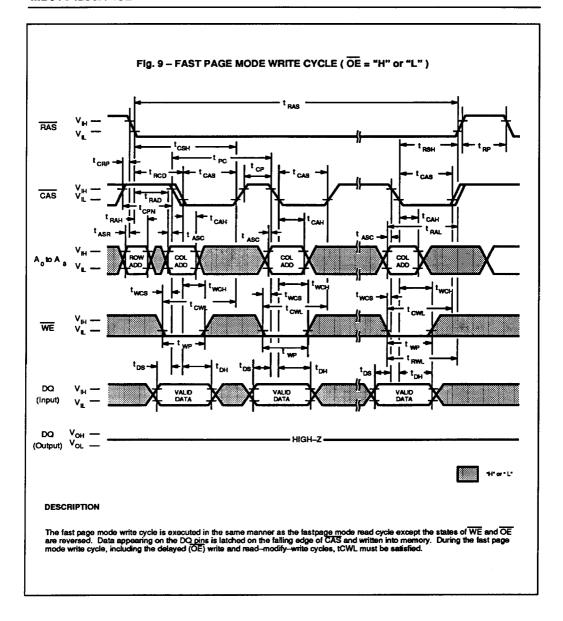

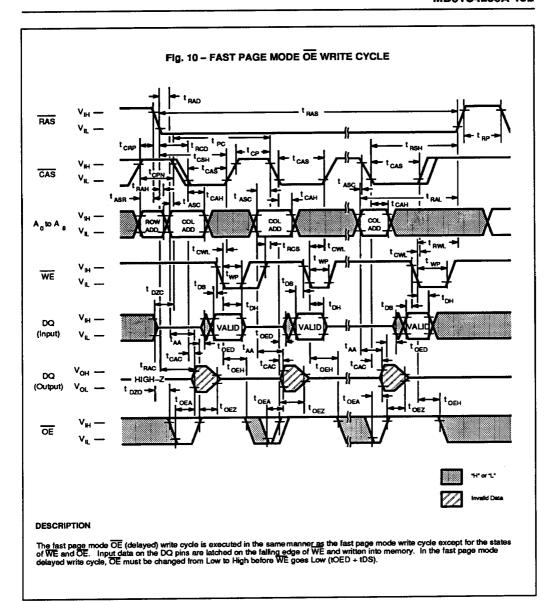

Input data is written into memory in either of three basic ways—an early write cycle, an  $\overline{OE}$  (delayed) write cycle, and a read-modify-write cycle. The falling edge of  $\overline{WE}$  or  $\overline{CAS}$ , whichever is later, serves as the input data-latch strobe. In an early write cycle, the input data (DQ1-DQ4) is strobed by  $\overline{CAS}$  and the setup/hold times are referenced to  $\overline{CAS}$  because  $\overline{WE}$  goes Low before  $\overline{CAS}$ . In a delayed write or a read-modify-write cycle,  $\overline{WE}$  goes Low after  $\overline{CAS}$ ; thus, input data is strobed by  $\overline{WE}$  and all setup/hold times are referenced to the write—enable signal.

### DATA OUTPUT

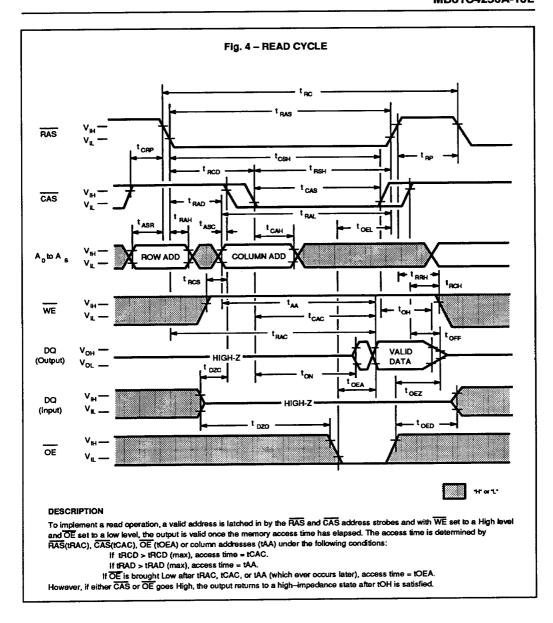

The three-state buffers are TTL compatible with a fanout of two TTL loads. Polarity of the output data is identical to that of the input; the output buffers remain in the high-impedance state until the column address strobe goes Low. When a read or read-modify-write cycle is executed, valid outputs are obtained under the following conditions:

- tRAC: from the falling edge of RAS when tech (max) is satisfied.

- tCAC: from the falling edge of CAS when tRCD is greater than tRCD, tRAD (max).

- tAA : from column address input when trab is greater than trab (max).

- tOEA: from the falling edge of OE when OE is brought Low after trac, toac, or tax

The data remains valid until either CAS or OE returns to a High logic level. When an early write is executed, the output buffers remain in a high-impedance state during the entire cycle.

DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted) Notes 3

| (Recommended                                              | operating cond | Notes 3          |                                                                                                                    |          |              |          |      |

|-----------------------------------------------------------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------|----------|--------------|----------|------|

| Parame                                                    | w Notes        | Symbol           | Conditions                                                                                                         | Uh       | Vales<br>372 | Max      | Unit |

| Output high voltage  Output low voltage                   |                | V <sub>OH</sub>  | I <sub>OH</sub> = -5 mA                                                                                            | 2.4      |              | _        | v    |

|                                                           |                | V <sub>OL</sub>  | 1 <sub>OL</sub> = 4.2 mA                                                                                           | -        |              | 0.4      |      |

| Input leakage current                                     | (any input)    | I I(L)           | 0V≤V <sub>N</sub> ≤5.5V;<br>4.5V≤V <sub>CC</sub> ≤5.5V;<br>V <sub>SS</sub> = 0V; All other pins<br>under test = 0V | -10      | -            | 10       | μΑ   |

| Output leakage curren                                     | ıt             | l O(r)           | 0V≤V <sub>OUT</sub> ≤ 5.5V;<br>Data out disabled                                                                   | -10      | _            | 10       |      |

|                                                           | MB81C4256A-70L |                  |                                                                                                                    |          |              | 68       |      |

| Operating current<br>(Average Power<br>supply Current)    | MB81C4256A-80L | I <sub>cc1</sub> | RAS & CAS cycling;<br>trc = min                                                                                    |          | _            | 62       | mA   |

| 2                                                         | MB81C4256A-10L | 2                |                                                                                                                    |          |              | 54       |      |

| Standby current<br>(Power supply<br>current)              | TTL level      |                  | RAS = CAS =VH                                                                                                      | ]        |              | 1.0      | mA.  |

|                                                           | CMOS level     | l cc2            | RAS - CAS ≥ V <sub>CC</sub> -0.2V                                                                                  | ] -      | _            | 0.25     | 1104 |

|                                                           | MB81C4256A-70L |                  | CAS = VH, RAS cycling;<br>tac = min                                                                                |          |              | 68<br>62 |      |

| Refresh current #1<br>(Average power sup-                 | MB81C4256A-80L | Icca             |                                                                                                                    | -        | . —          |          | mA   |

| ply current) 2                                            | MB81C4256A-10L |                  |                                                                                                                    |          |              | 54       |      |

|                                                           | MB81C4256A-70L |                  |                                                                                                                    |          |              | 55       |      |

| Fast Page Mode current 2                                  | MB81C4256A-80L | I <sub>CC4</sub> | RAS =VIL, CAS cycling;<br>tpc = min                                                                                | _        | -            | 50       | mA   |

|                                                           | MB81C4256A-10L |                  |                                                                                                                    | <u> </u> |              | 43       |      |

|                                                           | MB81C4256A-70L |                  | RAS cycling;                                                                                                       |          |              | 68       |      |

| Refresh current #2<br>(Average power sup-<br>ply current) | MB81C4256A-80L | l <sub>ccs</sub> | CAS-before-RAS;                                                                                                    | _        | -            | 62       | mA   |

| ply current) 2                                            | MB81C4256A-10L |                  | - 1mi                                                                                                              |          |              | 54       |      |

| Battery Back up                                           | MB81C4256A-70L |                  | RAS cycling ;<br>CAS before RAS ;                                                                                  |          |              |          |      |

| (Average power                                            | MB81C4256A-80L | lccs             | t <sub>RC</sub> =125 µs, t <sub>RAS</sub> =min.<br>to 1 µ.s, DQ1 to 4 ≥ Vcc<br>-0.2V or ≤ 0.2V or Open             | _        | _            | 250      | μΑ   |

| supply current)                                           | MB81C4256A-10L |                  | Other pin ≥V∞-0.2V or<br>≤ 0.2V                                                                                    |          |              |          |      |

## **AC CHARACTERISTICS**

(At recommended operating conditions unless otherwise noted.) Notes 3, 4, 5

| No. | Parameter Notes                             | Bymbol           | MBF   | =4786A<br>0L | MOIS<br>Se  | C42 <b>64</b><br>0L |      | C4256A<br>10L     | Unit  |

|-----|---------------------------------------------|------------------|-------|--------------|-------------|---------------------|------|-------------------|-------|

| ""  |                                             |                  | a Sin |              | <u>anna</u> | Min.                | Mile | 2.0               |       |

| 1   | Time Between Refresh                        | t <sub>REF</sub> | -     | 64           | _ `         | 64                  |      | 64                | ms    |

| 2   | Random Read/Write Cycle Time                | t <sub>RC</sub>  | 140   | -            | 155         |                     | 180  |                   | ns    |

| 3   | Read-Modify-Write Cycle Time                | † <sub>RWC</sub> | 180   | -            | 205         |                     | 240  | -                 | ns    |

| 4   | Access Time from RAS 6,9                    | t <sub>RAC</sub> |       | 70           |             | 80                  |      | 100               | ns    |

| 5   | Access Time from CAS 7.9                    | †CAC             | _     | 20           |             | 20                  |      | 25                | ns    |

| 6   | Column Address Access Time 8,9              | t <sub>AA</sub>  |       | 35           | -           | 40                  |      | 50                | ns    |

| 7   | Output Hold Time                            | t <sub>OH</sub>  | 0     | -            | 0           |                     | 0    |                   | ns    |

| 8   | Output Buffer Turn On Delay Time            | ton              | 0     |              | 0           |                     | 0    |                   | ns    |

| 9   | Output Buffer Turn off Delay Time 10        | toff             | _     | 15           |             | 20                  | -    | 25                | ns    |

| 10  | Transition Time                             | t <sub>T</sub>   | 2     | 50           | 2           | 50                  | 2    | 50                | ns    |

| 11  | RAS Precharge Time                          | t <sub>RP</sub>  | 60    |              | 65          | -                   | 70   |                   | ns    |

| 12  | RAS Pulse Width                             | t <sub>RAS</sub> | 70    | 100000       | 80          | 100000              | 100  | 100000            | ns    |

| 13  | RAS Hold Time                               | t <sub>RSH</sub> | 20    | _            | 20          |                     | 25   |                   | ns    |

| 14  | CAS to RAS Precharge Time                   | tcre             | •     | _            | 0           | -                   | 0    |                   | ns    |

| 15  | RAS to CAS Delay Time 11,12                 | t <sub>RCD</sub> | 20    | 50           | 22          | 60                  | 25   | 75                | ns    |

| 16  | CAS Pulse Width                             | tcas             | 20    | _            | 20          |                     | 25   |                   | ns    |

| 17  | CAS Hold Time                               | tcsH             | 70    | _            | 80          | _                   | 100  |                   | ns    |

| 18  | CAS Precharge Time (C-B-R cycle) 19         | t <sub>CPN</sub> | 20    | _            | 20          |                     | 20   |                   | ns    |

| 19  | Row Address Set Up Time                     | t <sub>ASR</sub> | 0     | _            | 0           |                     | 0    |                   | ns    |

| 20  | Row Address Hold Time                       | t <sub>RAH</sub> | 10    | _            | 12          |                     | 15   | -                 | ns    |

| 21  | Column Address Set Up Time                  | t ASC            | 0     |              | 0           | _                   | 0    |                   | ns    |

| 22  | Column Address Hold Time                    | t <sub>CAH</sub> | 12    | _            | 15          |                     | 15   |                   | ns    |

| 23  | RAS to Column Address Delay Time 13         | t <sub>RAD</sub> | 15    | 35           | 17          | 40                  | 20   | 50                | ns    |

| 24  | Column Address to RAS Lead Time             | t <sub>RAL</sub> | 35    |              | 40          |                     | 50   | _ '               | ns    |

| 25  | Read Command Set Up Time                    | t <sub>RCS</sub> | 0     |              | 0           |                     | 0    |                   | ns    |

| 26  | Read Command Hold Time<br>Referenced to RAS | t <sub>RRH</sub> | 0     |              | 0           | _                   | 0    |                   | ns    |

| 27  | Read Command Hold Time<br>Referenced to CAS | <sup>t</sup> ясн | 0     |              | ۰           |                     | 0    |                   | ns    |

| 28  | Write Command Set Up Time 15                | twcs             | 0     |              | 0           |                     | 0    |                   | ns .  |

| 29  | Write Command Hold Time                     | t <sub>WCH</sub> | 10    |              | 12          | <u> </u>            | 15   |                   | ns ns |

| 30  | WE Pulse Width                              | t <sub>wp</sub>  | 10    |              | 12          |                     | 15   | <b>↓</b> <u> </u> | ns .  |

| 31  | Write Command to RAS Lead Time              | t <sub>RWL</sub> | 15    | <u> </u>     | 20          | <u> </u>            | 25   | <u> </u>          | ns    |

| 32  | Write Command to CAS Lead Time              | t <sub>CWL</sub> | 12    |              | 15          |                     | 20   | <del>  -</del>    | ns    |

| 33  | DIN set Up Time                             | t <sub>DS</sub>  | 0     |              | 0           | <u> </u>            | •    | <b>↓</b>          | ns    |

| 34  | DIN Hold Time                               | t <sub>DH</sub>  | 10    |              | 12          |                     | 15   | <u> </u>          | ns    |

# AC CHARACTERISTICS (Continued)

(At recommended operating conditions unless otherwise noted.) Notes 3, 4, 5

|     | ( Iscontinenced oberaxing constitution                    |                   | MB810     | :4258A                                  |            | A256A | MBB10 |          |       |

|-----|-----------------------------------------------------------|-------------------|-----------|-----------------------------------------|------------|-------|-------|----------|-------|

| No. | Parameter Notes                                           | Symbol            | -7<br>Min | 200-10000000000000000000000000000000000 | -80<br>Min | Mex   | Win.  | Max      | Unit  |

| 35  | RAS Precharge time to CAS<br>Active Time (Refresh cycles) | t <sub>RPC</sub>  | 0         |                                         | 0          |       | 0     | _        | ns    |

| 36  | CAS Set Up Time for CAS-before-<br>RAS Refresh            | t <sub>CSR</sub>  | 0         | _                                       | 0          |       | 0     | _        | NB    |

| 37  | CAS Hold Time for CAS-before—<br>RAS Refresh              | t CHR             | 10        | _                                       | 12         |       | 15    |          | ns    |

| 38  | Access Time from OE                                       | t <sub>OEA</sub>  | _         | 20                                      |            | 20    |       | 25       | ns    |

| 39  | Output Buffer Turn Off Delay 10 from OE                   | toez              | ı         | 15                                      |            | 20    |       | 25       | ns    |

| 40  | OE to RAS Lead Time for Valid Data                        | t OEL             | 10        |                                         | 10         |       | 10    |          | ns    |

| 41  | OE Hold Time Referenced to WE 16                          | t OEH             | 0         | -                                       | 0          |       | 0     |          | ns    |

| 42  | OE to Data In Delay Time                                  | t <sub>OED</sub>  | 15        |                                         | 20         |       | 25    |          | ns    |

| 43  | DIN to CAS Delay Time 17                                  | t ozc             | ٥         |                                         | 0          |       | 0     |          | ns.   |

| 44  | DIN to OE Delay Time 17                                   | t <sub>D2O</sub>  | 0         |                                         | 0          |       | 0     |          | ne ne |

| 50  | Fast Page Mode Read/Write<br>Cycle Time                   | t <sub>PC</sub>   | 50        |                                         | 55         |       | 65    |          | ns    |

| 51  | Fast Page Mode Read-Modify-Write<br>Cycle Time            | t <sub>PRWC</sub> | 87        |                                         | 100        |       | 120   |          | ns    |

| 52  | Access Time from CAS Precharge 9,18                       | t CPA             |           | 45                                      | <u> </u>   | 50    | _ = _ | 60       | ns    |

| 53  | Fast Page Mode CAS Precharge Time                         | t <sub>CP</sub>   | 10        |                                         | 10         |       | 10    | <u> </u> | ns    |

### Notes:

- 1. Referenced to VSS

- icc depends on the output load conditions and cycle rates; The specified values are obtained with the output open.

icc depends on the number of address change as FAS = Vs. and

- Icc1, Icc3 and Iccs are specified at three time of address change during TAS = VL and TAS = VH.

- locs is specified at one time of address change during TAS = VIL

- 3. An Initial pause (RAS =CAS =VIH) of 200µs is required after power-up followed by any eight RAS -only cycles before proper device operation is achieved. In case of using internal refresh counter, a minimum of eight CAS -before-RAS initialization cycles instead of B RAS cycles are required.

- 4. AC characteristics assume tr = 5ns

- V<sub>H</sub> (min) and V<sub>L</sub> (max) are reference levels for measuring timing of input signals. Also transition times are measured between V<sub>H</sub> (min) and V<sub>L</sub> (max).

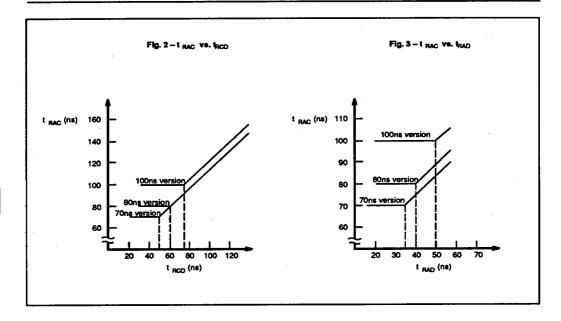

- Assumes that tracp≤ tracp (max), tracp≤ tracp (max). If tracp is greater than the maximum recommended value shown in this table, tracp will be increased by the amount that tracp exceeds the value shown. Refer to Fig. 2 and 3.

- 7. Assumes that trco≥ trco (max), trao≥ trao (max). If tasc≥ taa tcac t + access time is tcac.

- B. If tRAD ≥ tRAD (max) and tasc ≤ tax -tcac -t + , access time is tax.

- 9. Measured with a load equivalent to two TTL loads and 100 pF.

- topp and toez is specified that output buffer change to high impedance state.

- 11. Operation within the trace (max) limit ensures that trace (max) can be met. trace (max) is specified as a reference point only; if trace is greater than the specified trace (max) limit, access time is controlled exclusively by trace or trace.

- 12. tRCD (min) = tRAH (min)+ 2t T + tasc (min)

- 13. Operation within the trap (max) limit ensures that trac (max) can be met. trap (max) is specified as a reference point only; if trap is greater than the specified trap (max) limit, access time is controlled exclusively by trac or trap.

- 14. Either trial or trick must be satisfied for a read cycle.

- twcs is specified as a reference point only. If twcs ≥ twcs (min) the data output pin will remain High-Z state through entire cycle.

- 16. Assumes that twcs < twcs (min)

- 17. Either tozc or tozo must be satisfied.

- tcpa is access time from the selection of a new column address (that is caused by changing CAS from "L" to "H"). Therefore, if tcp is shortened, tcpa is longer than tcpa (max).

- Assumes that CAS-before-RAS refresh, CAS-before-RAS refresh counter test cycle only.

## **FUNCTIONAL TRUTH TABLE**

| Operation Mode                      |      |          | cinput |      | *************************************** | ress   |            | t Data           | Hefresh | Note                      |

|-------------------------------------|------|----------|--------|------|-----------------------------------------|--------|------------|------------------|---------|---------------------------|

| Standby                             | R/AS | CAS<br>H | WE     | X    | How<br>—                                | Column | Input<br>— | Output<br>High-Z | _       | ,                         |

| Read Cycle                          | L    | L        | н      | L    | Valid                                   | Valid  | _          | Valid            | Yes *   | tncs≥tncs (min)           |

| Write Cycle<br>(Early Write)        | L    | ٦        | L      | х    | Valid                                   | Valid  | Valid      | High-Z           | Yes *   | twcs≥twcs (min)           |

| Read-Modify-<br>Write Cycle         |      | L        | H→Ł    | L-→H | Valid                                   | Valid  | Valid      | Valid            | Yes *   |                           |

| RAS-only<br>Refresh Cycle           | L    | н        | х      | х    | Valid                                   | _      | _          | High-Z           | Yes     |                           |

| CAS-before-<br>RAS Refresh<br>Cycle | L    | ٦        | х      | х    | _                                       | _      | _          | High-Z           | Yes     | tcsn <u>≥</u> twcsn (min) |

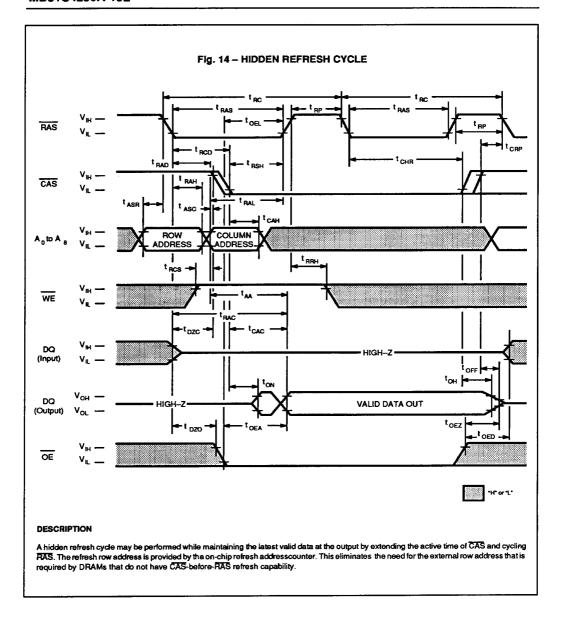

| Hidden Refresh                      | H→L  | L        | x      | L    | _                                       | _      | _          | Valid            | Yes     | Previous data<br>is kept. |

X; "H" or "L"

"; It is impossible in Fast Page Mode

### DESCRIPTION

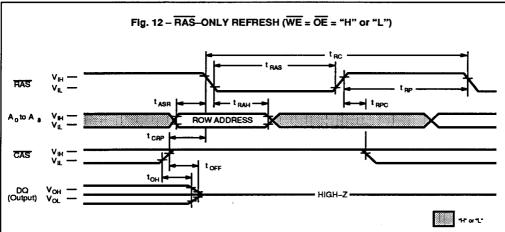

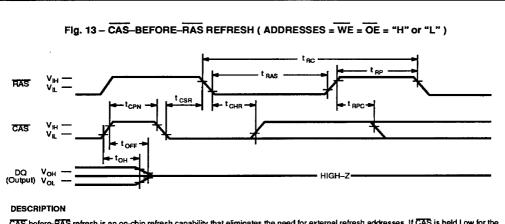

Refresh of RAM memory cells is accomplished by performing aread, a write, or a read-modify-write cycle at each of 512 row addresses every 8.2-milliseconds. Three refresh modes are available: RAS-only refresh, CAS-before-RAS refresh, and hidden refresh.

RAS—only refresh is performed by keeping RAS Low and CAS High throughout the cycle; the row address to be refreshed is latched on the falling edge of RAS. During RAS—only refresh, Dout pin is kept in a high-impedance state.

CAS-before-FAS refresh is an on-chip refresh capability that eliminates the need for external refresh addresses. If CAS is held Low for the specified setup time (tcsn) before FAS goes Low, the on-chip refresh control clock generators and refresh address counter are enabled. An internal refresh operation automatically occurs and the refresh address counter is internally incremented in preparation for the next CAS-before-FAS refresh operation.

### DESCRIPTION

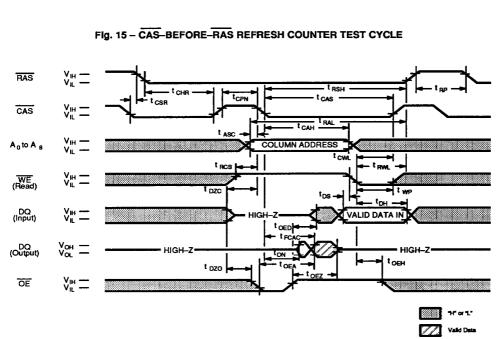

A special timing sequence using the CAS-before-RAS refresh counter test cycle provides a convenient method to verify the functionality of CAS-before-RAS refresh circuitry. If, after a CAS-before-RAS refresh cycle. CAS makes a transition from High to Low while RAS is held Low, read and write operations are enabled as shown above. Row and column addresses are defined as follows:

Row Address: Bits A0 through A8 are defined by the on-chip refresh counter.

Column Address: Bits A0 through A8 are defined by latching levels on A0-A8 at the second falling edge of CAS.

The CAS-before-HAS Counter Test procedure is as follows ;

- 1) Initialize the internal refresh address counter by using 8 CAS-before-RAS refresh cycles.

- 2) Use the same column address throughout the test.

- 3) Write "0" to all 512 row addresses (DQ1 to DQ4) at the same column address by using normal write cycles.

- 4) Read "0" written in procedure 3) and check; simultaneously write "1" to the same addresses by using CAS—before—RAS refresh counter test (read—modify—write cycles). Repeat this procedure 512 times with addresses generated by the internal refresh address counter.

- 5) Read and check data written in procedure 4) by using normal read cycle for all 512 (DQ1 to DQ4) memory locations.

- 6) Complement test pattern and repeat procedures 3), 4), and 5).

(At recommended operating conditions unless otherwise noted.)

| No. | Parameter            | Symbol | MB81<br>-7<br>Min | C4256A<br>OL<br>Max | MB81:<br>-8:<br>Min | C4256A<br>DL<br>Max | MB81 | C4256A<br>OL<br>Max | Unit |

|-----|----------------------|--------|-------------------|---------------------|---------------------|---------------------|------|---------------------|------|

| 90  | Access Time from CAS | t FCAC | _                 | 45                  | _                   | 50                  | _    | 60                  | ກຣ   |

Note . Assumes that CAS-before-RAS refresh counter test cycle only.

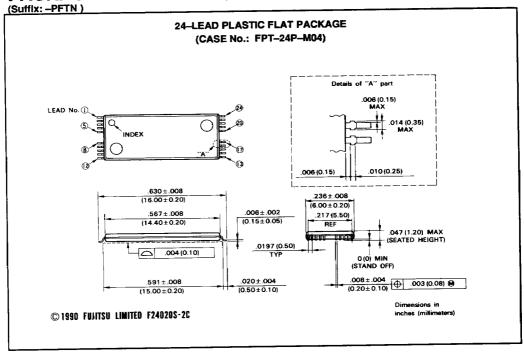

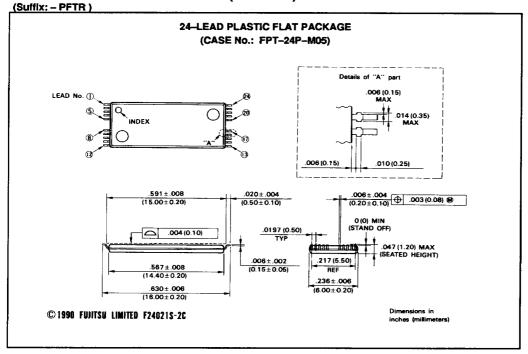

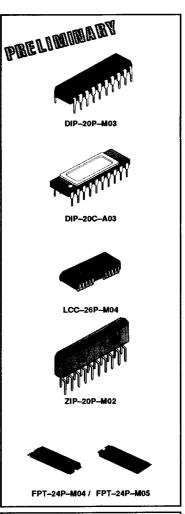

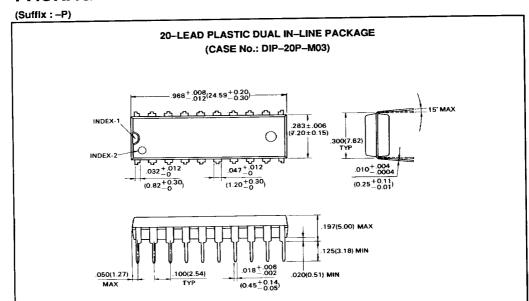

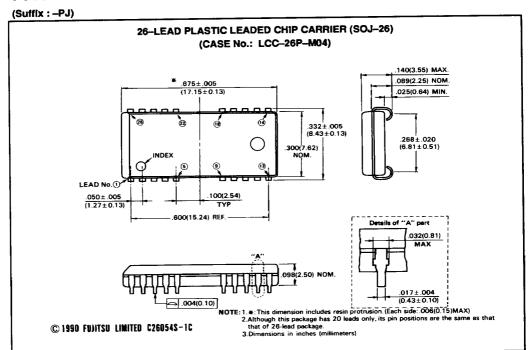

## **PACKAGE DIMENSIONS**

© 1988 FUJITSU LIMITED D20011S-1C

Dimensions in inches (millimeters)

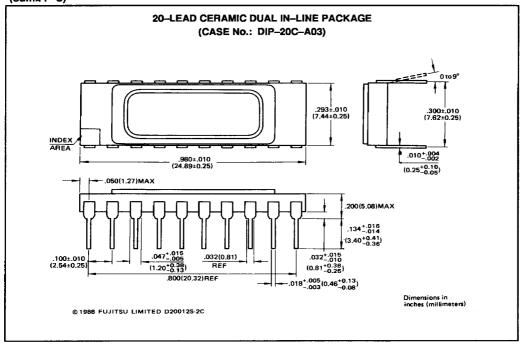

(Suffix : -C)

Dimensions in

inches (millimeters)

# PACKAGE DIMENSIONS (Continued)

© 1989 FUJITSU LIMITED Z20D02S-4C

(Suffix:-PSZ) 20-LEAD PLASTIC ZIG-ZAG IN-LINE PACKAGE (CASE No.: ZIP-20P-M02) -1.019<sup>+.008</sup>(25.88<sup>+0.20</sup>) .112±.008 (2.85±0.20) .387±.013 (9.83±0.33) INDEX .335 ± .010 (8.50±0.25) .010±.002 .118(3.00) MIN (0.25 ± 0.05) .100(2.54) TYP (0.50±0.10) (ROW SPACE) LEAD No. (1) (BOTTOM VIEW)