# **FUJITSU**

## Corporate names revised in the documents

The Fujitsu Limited reorganized its LSI business into a wholly owned subsidiary, the Fujitsu Microelectronics Limited on March 21, 2008.

The corporate names "Fujitsu" and "Fujitsu Limited" described all in this document have been revised to the "Fujitsu Microelectronics Limited". Thank you for your cooperation and understanding this notice.

Moreover, there are no changes in the related documents other than corporate names revised. Customers are advised to consult with sales representatives before ordering.

> March 21, 2008 Fujitsu Microelectronics Limited

**FUJITSU SEMICONDUCTOR**

AM41-10101-1E

ASSP MANUAL

# ICS FOR MONITORING POWER VOLTAGE POWER SUPPLY ASSP

# **APPLICATION NOTES**

# ICS FOR MONITORING POWER VOLTAGE POWER SUPPLY ASSP

# **APPLICATION NOTES**

**FUJITSU LIMITED**

## PREFACE

### Objectives and Intended Reader

The purpose of this manual is to promote the idea among our users that Fujitsu's ICs are easy to use. It is composed of a collection of frequently asked questions and data items which provide supplementary information to data sheets. Through numerous examples, it provides easy-to-understand explanations aimed at helping users make effective use of our products. We hope that this manual will be helpful for the users of Fujitsu ICs engaged in power voltage monitoring.

It should be remembered that the circuit diagrams and data values mentioned in this manual are for reference use only and that these numerical values are not guaranteed ones.

This manual should be read by engineers responsible for developing products which will use Fujitsu ICs for monitoring power voltage.

## Structure of This Manual

### This manual consists of five chapters as follows:

### Chapter 1 MB3761 Applications

This chapter provides applications regarding the MB3761.

## Chapter 2 MB3771 Applications

This chapter provides applications regarding the MB3771.

#### Chapter 3 MB3773 Applications

This chapter provides applications regarding the MB3773.

## Chapter 4 MB3790 Applications

This chapter provides applications regarding the MB3790.

#### Chapter 5 MB3793 Applications

This chapter provides applications regarding the MB3793.

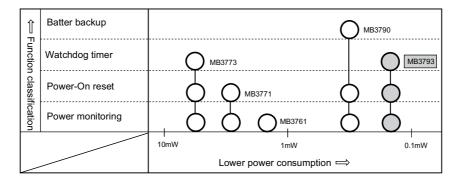

## FUNCTION CLASSIFICATION OF ICS FOR MONITORING POWER VOLTAGE

## **READING THIS MANUAL**

## Page Layout

Each of the sections in this manual has a summary placed immediately below the section title. This summary provides an outline of the section to assist readers in using the manual easily.

The titles of upper sections appear also in the lower sections to help you identify where you are in the manual.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering. 1. The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams. 2. The contents of this document may not be reproduced or copied without the permission of FUJITSU LIMITED. 3. FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipments, industrial, communications, and measurement equipments, personal or household devices, etc.). CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval. 4. Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and

abnormal operating conditions.5. If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior

authorization by Japanese government should be required for export of those products from Japan.

equipment such as redundancy, fire protection, and prevention of over-current levels and other

# CONTENTS

| CHAP | TER 1 MB3761 Applications                                                              | 1  |

|------|----------------------------------------------------------------------------------------|----|

| 1.1  | How to Produce Hysteresis Characteristics                                              | 2  |

| 1.2  | How to Add Hysteresis Characteristics                                                  | 8  |

| 1.3  | How to Search for Power Voltage Malfunctions [1]                                       | 11 |

| 1.4  | How to Search for Power Voltage Malfunctions [2]                                       | 12 |

| 1.5  | Programmable Zener                                                                     | 14 |

| 1.6  | Calculation in Sample Circuit for Resetting Reduced Voltage                            | 15 |

| 1.7  | How to Search for Malfunctions in Power Voltage with Hysteresis Characteristics [1]    | 17 |

| 1.8  | How to Search for Malfunctions in Power Voltage with Hysteresis Characteristics [2]    | 19 |

| 1.9  | How to Troubleshoot the MB3761                                                         |    |

| 1.9  | .1 If there are output fluctuations                                                    | 22 |

| 1.9  | .2 If hysteresis characteristics are not appropriate                                   |    |

| 1.10 | Q&A Set Regarding the MB3761                                                           | 26 |

| CHAP | TER 2 MB3771 Applications                                                              | 29 |

| 2.1  | Equations for Calculating External Fine-tuning Types                                   | 30 |

| 2.2  | Monitoring Arbitrary Power Voltage (for VCC smaller than or equal to 18V Relationship) | 32 |

| 2.3  | Monitoring Arbitrary Power Voltage (for 5V constant voltage output)                    | 33 |

| 2.4  | Monitoring Power Voltages of 5V and 12V                                                | 35 |

| 2.5  | Monitoring Power Voltage with Delayed Trigger                                          | 37 |

| 2.6  | Monitoring Negative Power Supply                                                       | 39 |

| 2.7  | Generating Reference Voltage and Monitoring Voltage Drops [1]                          | 41 |

| 2.8  | Generating Reference Voltage and Monitoring Voltage Drops [2]                          | 43 |

| 2.9  | Detecting Low Voltage and Excess Voltage                                               | 45 |

| 2.10 | Reset Output                                                                           |    |

| 2.11 | Handling Unused Terminals                                                              |    |

| 2.12 | Q&A Set Regarding the MB3771                                                           |    |

| 2.13 | Equivalent Circuits for MB3771 Input/output Unit                                       | 53 |

| CHAP | TER 3 MB3773 Applications                                                              | 55 |

| 3.1  | Equations for Calculating External Fine-tuning Types                                   | 56 |

| 3.2  | Monitoring Power Voltage with Delayed Trigger                                          | 57 |

| 3.3  | Equations for Calculating Timing Setting and Related Fluctuations                      | 59 |

| 3.4  | Configuration of CK Input Circuit Unit                                                 | 61 |

| 3.5  | How the Watch-dog Timer Works                                                          | 62 |

| 3.6  | How to Stop Watch-dog Timer                                                            | 64 |

| 3.7  | Cautions Regarding Watch-dog Timer Stop Circuit [1]                                    |    |

| 3.8  | Cautions Regarding Watch-dog Timer Stop Circuit [2]                                    | 66 |

| 3.9  | Operations of Comparator and Latch                                                     | 69 |

| 3.10 | Power Drop in Resetting Watch-dog Timer                                                |    |

| 3.11 | Handling Unused Terminals                                                              |    |

| 3.12 | Q&A Set Regarding the MB3773                                                           |    |

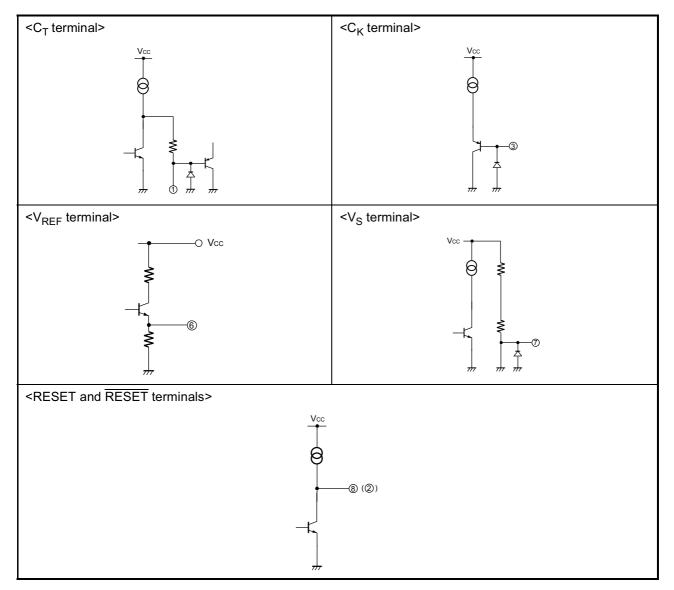

| 3.13 | Equivalent Circuits for MB3773 Input/output Unit                                       | 74 |

| CHAPT | ER 4 MB3790 Applications                                                           | 75  |

|-------|------------------------------------------------------------------------------------|-----|

| 4.1   | How to produce alarms in the case of a battery replacement                         | 76  |

| 4.2   | Analog switches                                                                    |     |

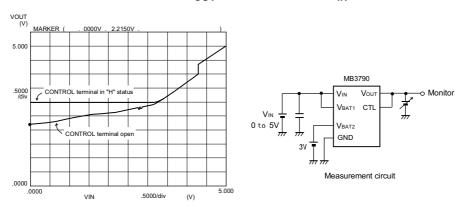

| 4.3   | How to fine-tune the voltage detection level for the power supply                  | 79  |

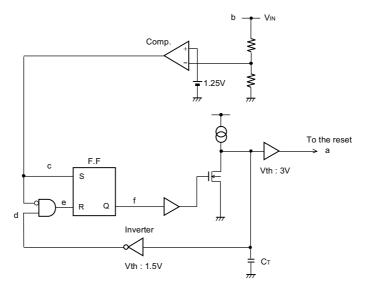

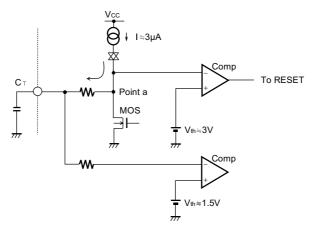

| 4.4   | Capacitance connected to the terminal CT                                           | 80  |

| 4.5   | How to adjust the time for detecting the voltage of the power supply               | 81  |

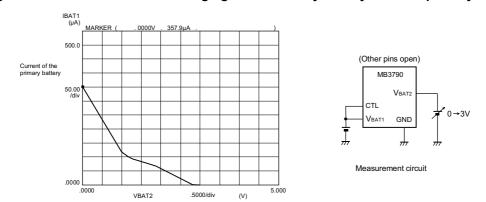

| 4.6   | Current consumption (IBATA and IBATB) in the primary battery                       | 83  |

| 4.7   | How to calculate the reset pulse width (tPO)                                       | 85  |

| 4.8   | Charging the secondary battery from the primary battery                            | 86  |

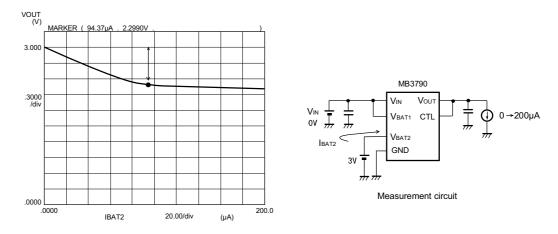

| 4.9   | Major reasons for drop in battery charges                                          | 88  |

| 4.10  | Operation at input pulse width (tPI) of less than 5µs                              | 90  |

| 4.11  | Backup: How to add a super capacitor to VOUT                                       | 92  |

| 4.12  | How to charge the secondary battery to more than 3V                                | 94  |

| 4.13  | Relationship between capacitance and output delay time                             | 95  |

| 4.14  | Warning remarks about connecting a diode to the VOUT terminal for power protection | 96  |

| 4.15  | Handling unused terminals                                                          | 98  |

| 4.16  | Q&A set regarding the MB3790                                                       | 99  |

| 4.17  | Comparison between the MB3780A and the MB3790                                      | 101 |

| СНАРТ | ER 5 MB3793 Applications                                                           | 103 |

| 5.1   | Meaning of values A to D                                                           | 104 |

| 5.2   | Clock timing                                                                       | 106 |

| 5.3   | Recommended circuit for limiting fmax                                              | 108 |

| 5.4   | Timing for the circuit limiting fmax                                               | 109 |

| 5.5   | Handling unused terminals                                                          | 110 |

| 5.6   | Typical circuit for monitoring only the voltage of the power supply                | 112 |

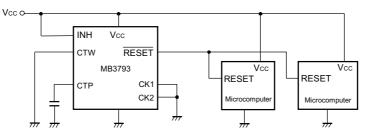

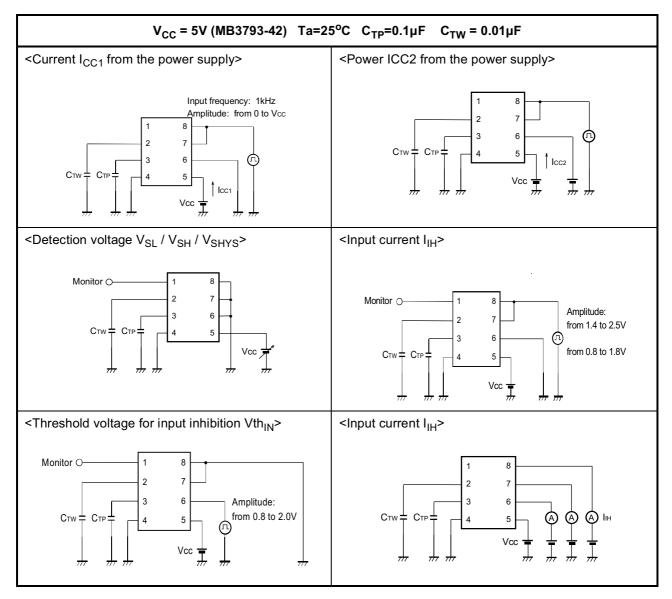

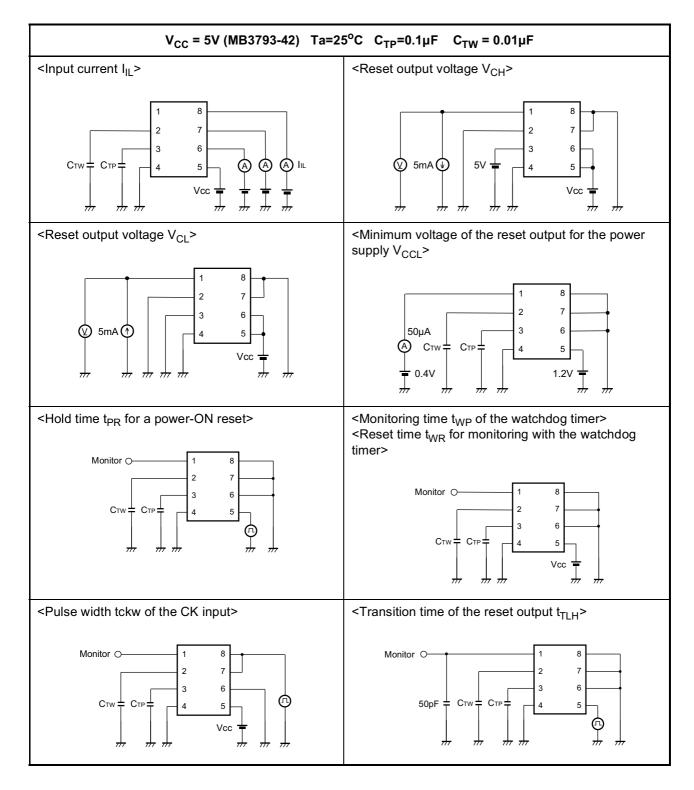

| 5.7   | Specific ways of checking external circuits of the MB3793-42                       | 113 |

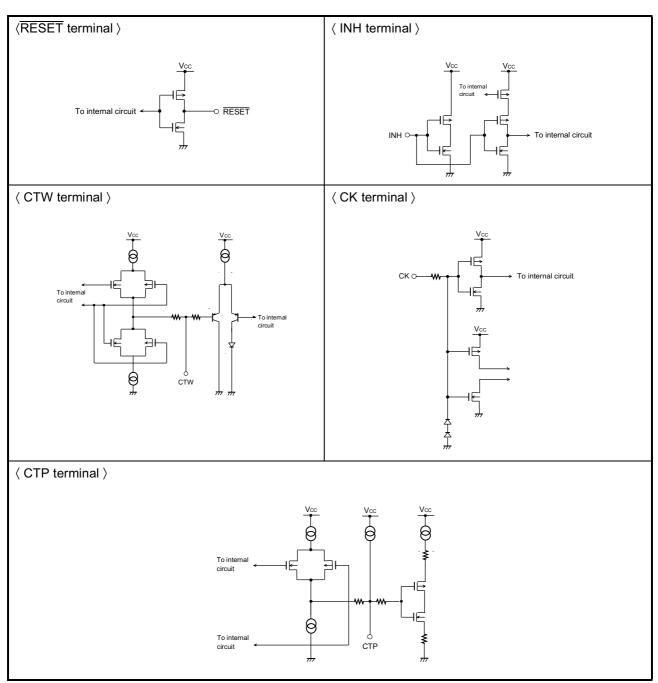

| 5.8   | Equivalent circuits for the use as input/output unit of the MB3793                 | 115 |

| 5.9   | Circuits for measuring the electric characteristics of the MB3793-42               | 117 |

| INDEX |                                                                                    | 119 |

## **FIGURES**

| <b>-</b> : <b>4 4 4</b> |                                                                                                                       | ~  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1-1            | Comp. A equivalent circuit                                                                                            |    |

| Figure 1.1-2            | Output operation of Comp. A (during a VIN rise)                                                                       |    |

| Figure 1.1-3            | Circuit operation of Comp. A with pin 3 terminal voltage lower than VR                                                |    |

| Figure 1.1-4            | Equivalent circuit of Comp. A under V3 < VR condition                                                                 |    |

| Figure 1.1-5            | Output operation of Comp. A (during a VIN fall)                                                                       |    |

| Figure 1.1-6            | Circuit operation of Comp. A with pin 3 terminal voltage higher than VR                                               |    |

| Figure 1.1-7            | Equivalent circuit of Comp. A under V3 > VR condition                                                                 | 4  |

| Figure 1.1-8            | Comp. B equivalent circuit                                                                                            |    |

| Figure 1.1-9            | Output operation of Comp. B (during a VIN fall)                                                                       | 5  |

| Figure 1.1-10           | Circuit operation of Comp. B with pin 1 terminal voltage higher than VR                                               | 5  |

| Figure 1.1-11           | Equivalent circuit of Comp. B under V1 > VR condition                                                                 | 6  |

| Figure 1.1-12           | Output operation of Comp. B (during a VIN rise)                                                                       | 6  |

| Figure 1.1-13           | Circuit operation of Comp. B with pin 1 terminal voltage lower than VR                                                | 6  |

| Figure 1.1-14           | Equivalent circuit of Comp. B under V1 < VR condition                                                                 | 7  |

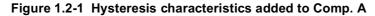

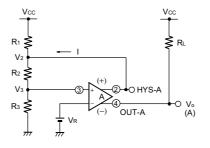

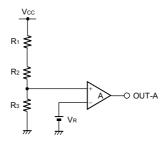

| Figure 1.2-1            | Hysteresis characteristics added to Comp. A                                                                           | 8  |

| Figure 1.2-2            | Equivalent circuit of Comp. A under V3 < VR condition                                                                 | 8  |

| Figure 1.2-3            | Equivalent circuit of Comp. A under V3 > VR condition                                                                 | 9  |

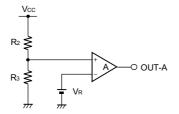

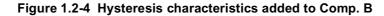

| Figure 1.2-4            | Hysteresis characteristics added to Comp. B                                                                           | 9  |

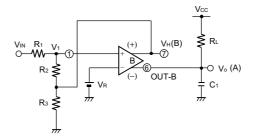

| Figure 1.2-5            | Equivalent circuit of Comp. B under V1 > VR condition                                                                 | 9  |

| Figure 1.2-6            | Equivalent circuit of Comp. B under V1 < VR condition                                                                 | 10 |

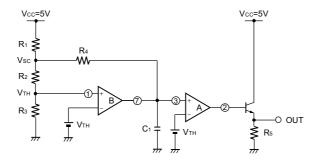

| Figure 1.6-1            | Equivalent circuit for resetting reduced voltage                                                                      | 15 |

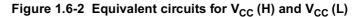

| Figure 1.6-2            | Equivalent circuits for VCC (H) and VCC (L)                                                                           | 15 |

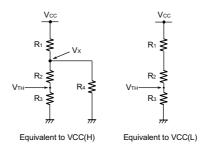

| Figure 1.7-1            | Sample circuit detecting for malfunctions in power voltage with hysteresis characteristics [1] .                      | 17 |

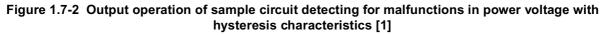

| Figure 1.7-2            | Output operation of sample circuit detecting for malfunctions in power voltage with hysteresis characteristics [1] 18 |    |

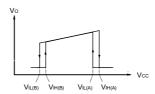

| Figure 1.7-3            | Equivalent circuit detecting malfunctions in power voltage with hysteresis characteristics [1]                        | 18 |

| Figure 1.8-1            | Sample circuit detecting for malfunctions in power voltage with hysteresis characteristics [2] .                      | 19 |

| Figure 1.8-2            | Output operation of sample circuit detecting for malfunctions in power voltage with hysteresis characteristics [2] 20 |    |

| Figure 1.9-1            | How to remove unstable output [1]                                                                                     | 22 |

| Figure 1.9-2            | How to remove unstable output [2]                                                                                     | 23 |

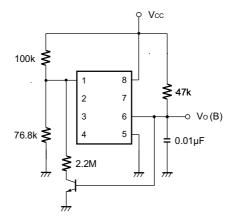

| Figure 1.9-3            | Adding hysteresis characteristics to Comp. A                                                                          | 24 |

| Figure 1.9-4            | Result close to the setting                                                                                           | 25 |

| Figure 1.9-5            | Result not close to the setting                                                                                       | 25 |

| Figure 2.1-1            | Equivalent circuit for calculating external fine-tuning types                                                         | 30 |

| Figure 2.2-1  | Equivalent circuit for monitoring arbitrary power voltage                                                                   | 32  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.3-1  | Equivalent circuit for providing constant voltage output                                                                    | 33  |

| Figure 2.4-1  | Equivalent circuit for monitoring 12V power voltage (when voltage at pin 2 is higher than 1.245 35                          | 5V) |

| Figure 2.4-2  | Equivalent circuit for monitoring 12V power voltage (when voltage at pin 2 is lower than 1.245 35                           | iV) |

| Figure 2.4-3  | Equivalent circuit for monitoring 5V power voltage                                                                          | 36  |

| Figure 2.5-1  | Equivalent circuit for monitoring power voltage with delayed trigger                                                        | 37  |

| Figure 2.5-2  | Change in voltage level at pin 7                                                                                            | 37  |

| Figure 2.5-3  | Measurements of detection time TPI (reference only)                                                                         | 38  |

| Figure 2.6-1  | Equivalent circuit for monitoring negative power supply [1]                                                                 | 39  |

| Figure 2.6-2  | Equivalent circuit for monitoring negative power supply [2]                                                                 | 39  |

| Figure 2.7-1  | Equivalent circuit for reference voltage generation and voltage drop detection [1] (generating and monitoring 5V/9V) 41     | 9V  |

| Figure 2.7-2  | Equivalent circuit for reference voltage generation and voltage drop detection [2] (generating and monitoring 5V/9V) 41     | 9V  |

| Figure 2.8-1  | Equivalent circuit for reference voltage generation and voltage drop detection [1] (generating and monitoring 5V) 43        | 5V  |

| Figure 2.8-2  | Equivalent circuit for reference voltage generation and voltage drop detection [2] (generating 1.245V and monitoring 5V) 43 |     |

| Figure 2.9-1  | Equivalent circuit for detecting low voltage and excess voltage                                                             | 45  |

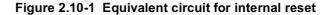

| Figure 2.10-1 | Equivalent circuit for internal reset                                                                                       | 46  |

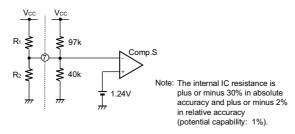

| Figure 3.1-1  | Equivalent circuit for calculating external fine-tuning types                                                               | 56  |

| Figure 3.2-1  | Equivalent circuit for monitoring power voltage with delayed trigger                                                        | 57  |

| Figure 3.2-2  | Change in voltage level at pin 7                                                                                            | 57  |

| Figure 3.2-3  | Measurements of detection time TPI (reference only)                                                                         | 58  |

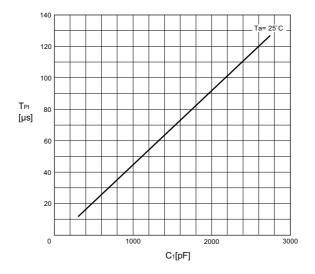

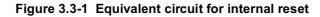

| Figure 3.3-1  | Equivalent circuit for internal reset                                                                                       | 59  |

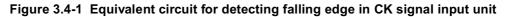

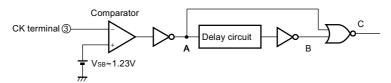

| Figure 3.4-1  | Equivalent circuit for detecting falling edge in CK signal input unit                                                       | 61  |

| Figure 3.4-2  | Equivalent circuit for detecting falling edge in CK signal input unit (waveforms)                                           | 61  |

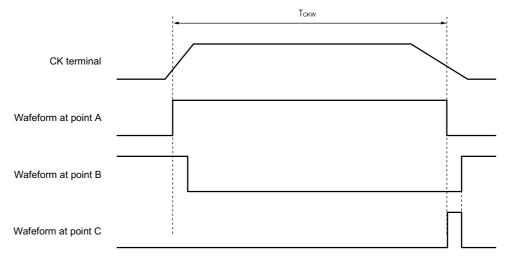

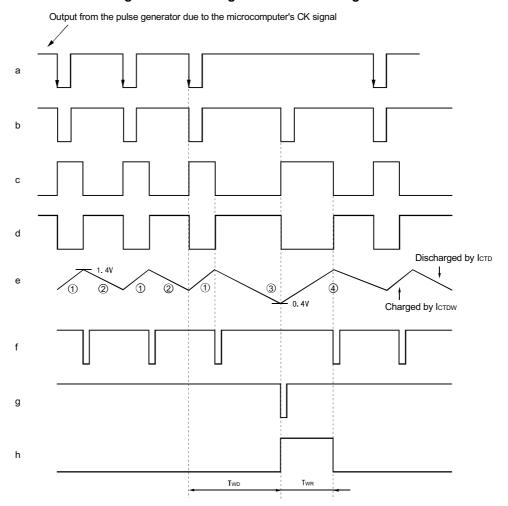

| Figure 3.5-1  | Equivalent circuit for watch-dog timer                                                                                      | 62  |

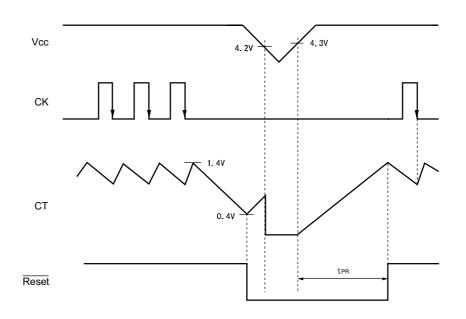

| Figure 3.5-2  | Timing chart for watch-dog timer                                                                                            | 63  |

| Figure 3.6-1  | How to stop watch-dog timer (using NPN trasistors)                                                                          | 64  |

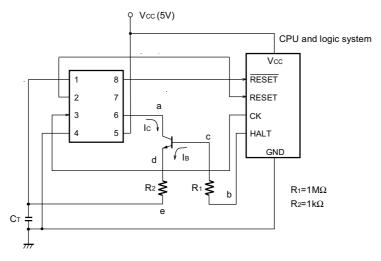

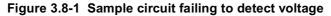

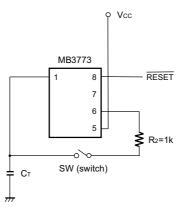

| Figure 3.8-1  | Sample circuit failing to detect voltage                                                                                    | 66  |

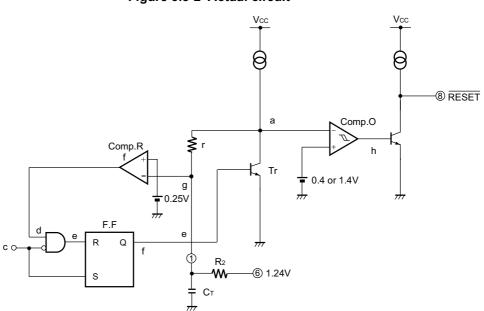

| Figure 3.8-2  | Actual circuit                                                                                                              | 67  |

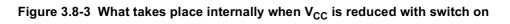

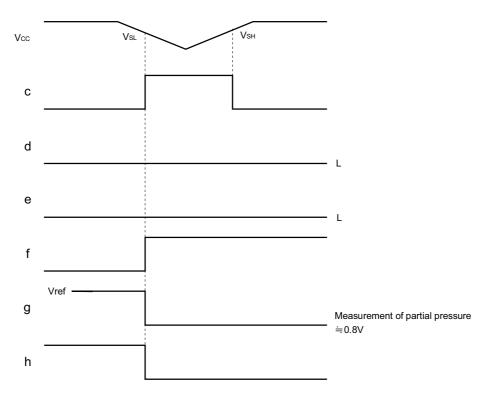

| Figure 3.8-3  | What takes place internally when VCC is reduced with switch on                                                              | 68  |

| Figure 3.9-1  | Operations timing of comparator and latch                                                                                   | 69  |

| Figure 4.1-1  | Equivalent circuit (for producing alarms during battery replacement)                                                        | 76  |

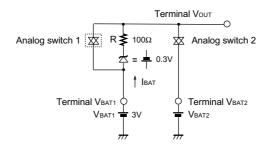

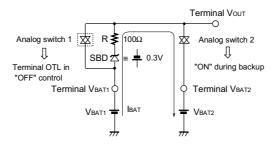

| Figure 4.2-1  | Equivalent circuit (for primary and secondary batteries)                                                                    | 77  |

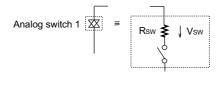

| Figure 4.2-2  | Equivalent circuit for analog switch 1                                                                                      | 77  |

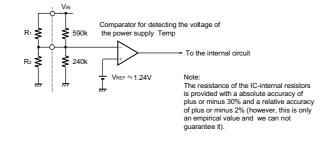

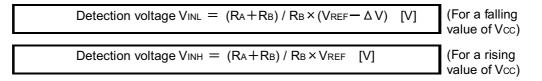

| Figure 4.3-1  | Equivalent circuit (for fine-tuning power voltage detection level)                                                          | 79  |

|               |                                                                                                                             |     |

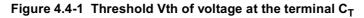

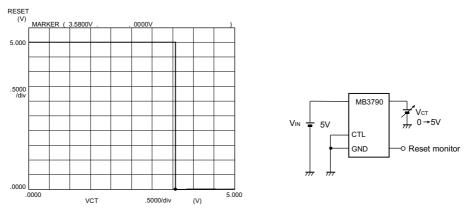

| Figure 4.4 | -1 Threshold Vth of voltage at the terminal CT                                                                                   | 80        |

|------------|----------------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 4.4 | -2 Relationship between leak current and voltage at the terminal CT                                                              | 80        |

| Figure 4.5 | -1 Equivalent circuit (for adjusting the time for detecting the voltage of the power supply)                                     | 81        |

| Figure 4.5 | -2 Change in the voltage at terminal VSENSE                                                                                      | 81        |

| Figure 4.7 | -1 Equivalent circuit [for calculating the reset pulse width (tPO)]                                                              | 85        |

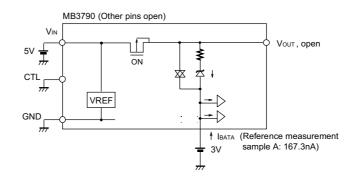

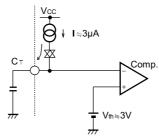

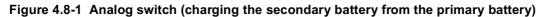

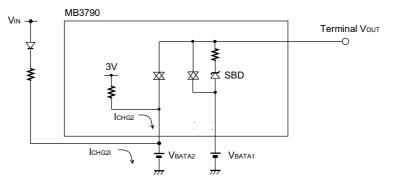

| Figure 4.8 | -1 Analog switch (charging the secondary battery from the primary battery)                                                       | 86        |

| Figure 4.8 | -2 Data obtained for charging the secondary battery from the primary battery                                                     | 86        |

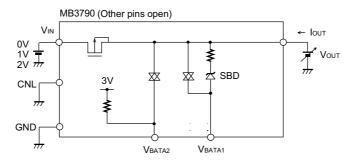

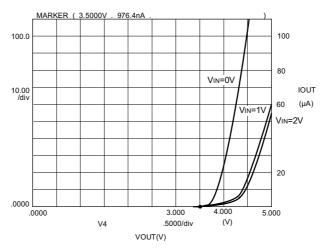

| Figure 4.9 | -1 VOUT in dependence of VIN                                                                                                     | 88        |

| Figure 4.9 | -2 VOUT in dependence of IBAT2                                                                                                   | 89        |

| Figure 4.1 | 0-1 Block diagram of the operation at input pulse width (tPI) of less than 5µs                                                   | 90        |

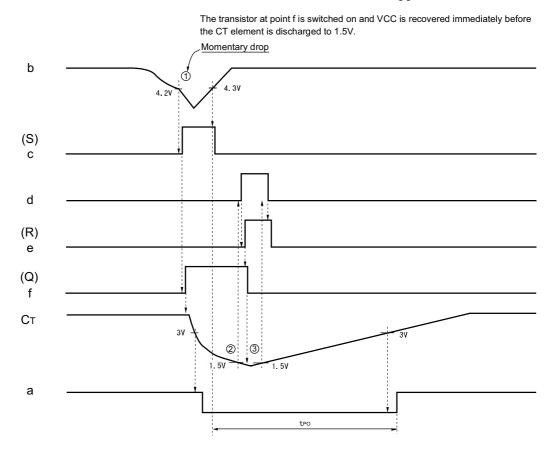

| Figure 4.1 | 0-2 Waveforms for a momentary drop in VCC                                                                                        | 91        |

| Figure 4.1 | <ul> <li>1-1 Equivalent circuit [1] (for implementing a backup by adding a super capacitor to the termina<br/>92</li> </ul>      | IVOUT)    |

| Figure 4.1 | <ul> <li>1-2 Equivalent circuit [2] (for implementing a backup by adding a super capacitor to the termina</li> <li>92</li> </ul> | IVOUT)    |

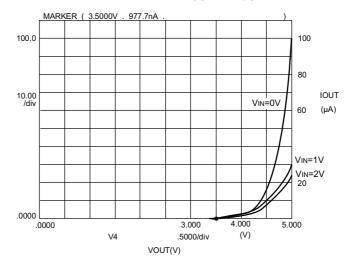

| Figure 4.1 | 1-3 Measured leak current IOUT at VOUT for an input of VIN [1]                                                                   | 93        |

| Figure 4.1 | 1-4 Measured leak current IOUT at VOUT for an input of VIN [2]                                                                   | 93        |

| Figure 4.1 | 2-1 Equivalent circuit (for charging the secondary battery to more than 3V)                                                      | 94        |

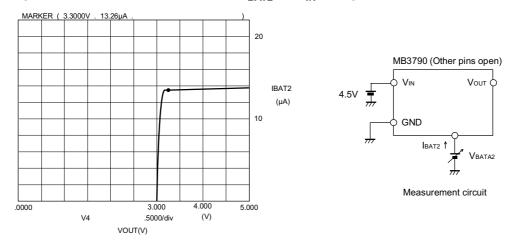

| Figure 4.1 | 2-2 Measured leak current VBAT2 for VIN voltages of more than 4.2V                                                               | 94        |

| Figure 4.1 | 3-1 Equivalent circuit (setting the relationship between capacitance and output delay time)                                      | 95        |

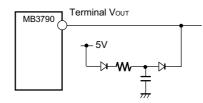

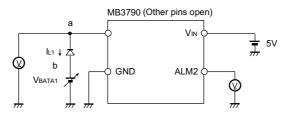

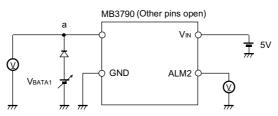

| Figure 4.1 | 4-1 Equivalent circuit [1] (for connecting a diode to the terminal VOUT for power protection)                                    | 96        |

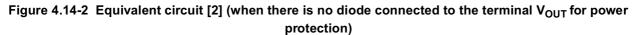

| Figure 4.1 | <ul> <li>4-2 Equivalent circuit [2] (when there is no diode connected to the terminal VOUT for power pro<br/>96</li> </ul>       | otection) |

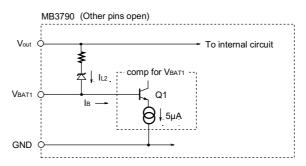

| Figure 4.1 | 4-3 Equivalent circuit (for the input unit of terminal VBAT1)                                                                    | 97        |

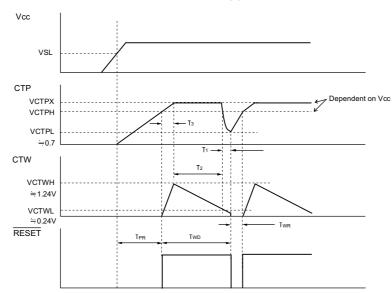

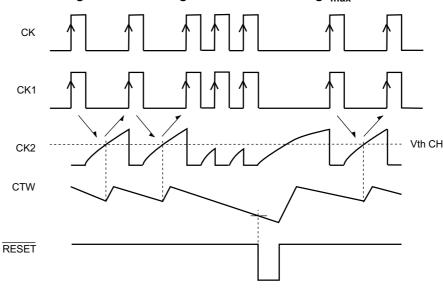

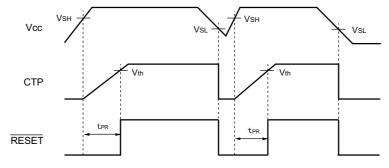

| Figure 5.1 | -1 Chart of the timing for the VCC, CTP, CTW, and RESET signals                                                                  | 104       |

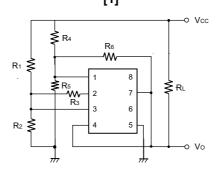

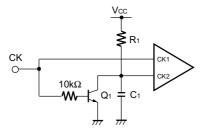

| Figure 5.3 | -1 Equivalent circuit (recommended circuit for limiting fmax)                                                                    | 108       |

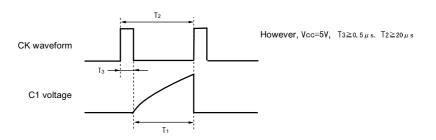

| Figure 5.4 | -1 Equivalent circuit (timing for the circuit limiting fmax)                                                                     | 109       |

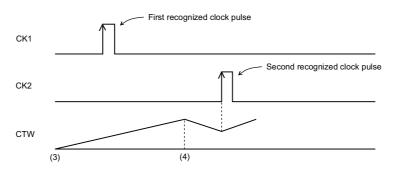

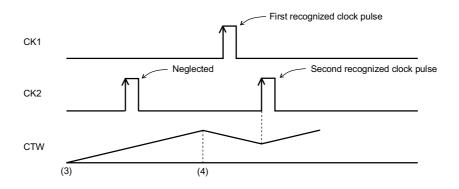

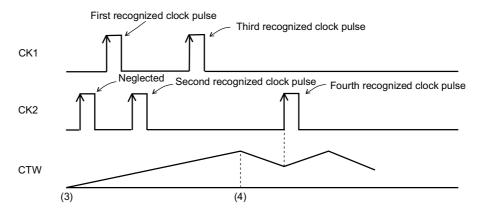

| Figure 5.4 | -2 Timing for the circuit limiting fmax                                                                                          | 109       |

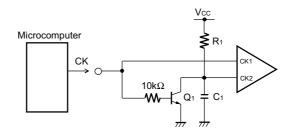

| Figure 5.6 | -1 Typical circuit for monitoring only the voltage of the power supply                                                           | 112       |

| Figure 5.6 | -2 Chart of the timing of a circuit for monitoring only the voltage of the power supply                                          | 112       |

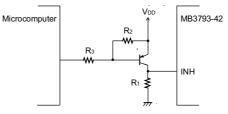

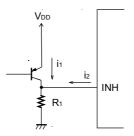

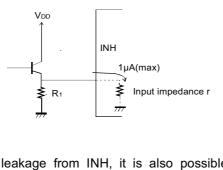

| Figure 5.7 | -1 Example of an external circuit for INH input                                                                                  | 113       |

# TABLES

| Table 2.1-1  | Details of calculating external fine-tuning types (calculating maximum value) | . 31 |

|--------------|-------------------------------------------------------------------------------|------|

| Table 2.11-1 | Handling unused terminals in the MB3771                                       | . 48 |

| Table 3.3-1  | Typical values                                                                | . 59 |

| Table 3.11-1 | Handling unused terminals in the MB3773                                       | . 71 |

| Table 4.15-1 | Handling unused terminals in the MB3790                                       | . 98 |

| Table 4.17-1 | Comparison between the MB3780A and the MB3790                                 | 101  |

| Table 5.5-1  | Handling unused terminals in the MB3793                                       | 110  |

## CHAPTER 1 MB3761 Applications

This chapter provides applications regarding the MB3761.

- 1.1 How to Produce Hysteresis Characteristics

- 1.2 How to Add Hysteresis Characteristics

- 1.3 How to Search for Power Voltage Malfunctions [1]

- 1.4 How to Search for Power Voltage Malfunctions [2]

- 1.5 Programmable Zener diodes

- 1.6 Calculation in Sample Circuit for Resetting Reduced Voltage

- 1.7 How to Search for Malfunctions in Power Voltage with Hysteresis Characteristics [1]

- 1.8 How to Search for Malfunctions in Power Voltage with Hysteresis Characteristics [2]

- 1.9 How to Troubleshoot the MB3761

- 1.10 Q&A Set Regarding the MB3761

## **1.1 How to Produce Hysteresis Characteristics**

## Using an external circuit, it is possible to add hysteresis characteristics to Comparators A and B (Comp. A and Comp. B) that are housed in the MB3761. • Related data sheet(s): Operational Definitions (Page 4)

### Hysteresis characteristics for Comp. A

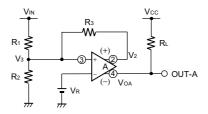

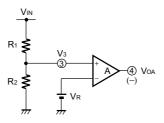

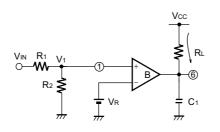

Comp. A shows different values of detection, depending on whether there is a current flow through  $R_3$  (refer to Figure 1.1-1).

## Figure 1.1-1 Comp. A equivalent circuit

## $\bigcirc$ At the time of a V<sub>IN</sub> rise

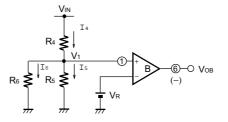

As shown in Figure 1.1-1, set an equivalent circuit. If the pin 3 terminal voltage (V<sub>3</sub>) is lower than V<sub>R</sub>, the internal circuit operates as shown in Figure 1.1-3; the transistors at pins (2 and 4) are off. Because of an R<sub>L</sub> pull-up, pin 4 provides an H output, which corresponds to the [1] range in Figure 1.1-2.

There is no current flow at point P, so that no current will flow out from pin (2). Therefore, there is no current flow at  $R_3$ . This means that the Figure 1.1-1 and Figure 1.1-4 circuits are equivalent.

#### Figure 1.1-2 Output operation of Comp. A (during a V<sub>IN</sub> rise)

Figure 1.1-3 Circuit operation of Comp. A with pin 3 terminal voltage lower than  $V_R$

Figure 1.1-4 Equivalent circuit of Comp. A under  $V_3 < V_R$  condition

The pin 3 terminal voltage  $(V_3)$  may be calculated from the following equation.

$$V_3 = \frac{R_2}{R_1 + R_2} V_{IN}$$

the detection voltage,  $V_{IN}$  (A), will reach the value of  $V_{IN}$  available when  $V_3 = V_R$ . Therefore, the following equation applies.

$$V_{H}(A) = \frac{R_1 + R_2}{R_2} VR$$

$$= (1 + \frac{R_1}{R_2}) VR$$

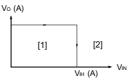

This reverses the output, resulting in the [2] range in Figure 1.1-2.

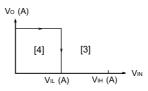

## $\bigcirc\,$ At the time of a V\_{IN} fall

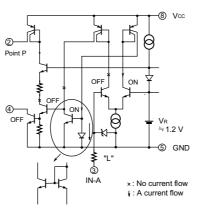

As the value of V<sub>IN</sub> is decreased gradually, the internal circuit operates as shown in Figure 1.1-6, when the pin 3 terminal voltage is higher than V<sub>R</sub> (this corresponds to the [3] range in Figure 1.1-5. The internal transistors at pins 2 and 4 are turned on. This changes the output at pin 4 to the L level, so that a current begins to flow at the pin 2 terminal (refer to Figure 1.1-7).

Figure 1.1-5 Output operation of Comp. A (during a V<sub>IN</sub> fall)

Figure 1.1-6 Circuit operation of Comp. A with pin 3 terminal voltage higher than V<sub>R</sub>

Figure 1.1-7 Equivalent circuit of Comp. A under V<sub>3</sub> > V<sub>R</sub> condition

As shown in Figure 1.1-7, there is a current flow (I<sub>3</sub>) through R<sub>3</sub>, thus increasing the value of current I<sub>2</sub> flowing through R<sub>2</sub>. This, in turn, increases the voltage drop through R<sub>2</sub> and increases the V<sub>3</sub> voltage level. To meet the V<sub>3</sub> = V<sub>R</sub> relationship, the increase in the V<sub>3</sub> voltage level requires a lower V<sub>IN</sub> value, which is lower than the value of V<sub>IN</sub> available during the change from [1] to [2] in Figure 1.1-2 (refer to the description of hysteresis characteristics).

Under these conditions, the following equations apply.

$$\frac{V_2 - V_3}{R_3} + \frac{V_{1N} - V_3}{R_1} = \frac{V_3}{R_2} - \dots (a)$$

$$V_2 = V_{CC} - \dots (b)$$

Substituting equation (b) into equation (a) provides the  $V_{\text{IN}}$  equation as follows.

$$V_{IN} = V_3 (1 + \frac{R_1}{R_2 / / R_3}) - \frac{R_1}{R_3} V_{CC}$$

### 1.1 How to Produce Hysteresis Characteristics

The detection voltage,  $V_{IL}(A)$ , will reach the value of  $V_{IN}$  available when  $V_3 = V_R$ .

Therefore, the following equation applies.

$$V_{IL}(A) = V_{R}(1 + \frac{R_{1}}{R_{2}//R_{3}}) - \frac{R_{1}}{R_{3}}V_{CC}$$

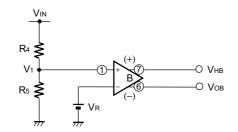

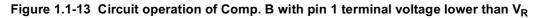

### Hysteresis characteristics for Comp. B

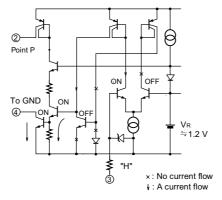

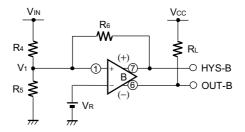

Comp. B shows different values of detection, depending on whether there is a current flow through  $R_6$  (refer to Figure 1.1-8 ).

## Figure 1.1-8 Comp. B equivalent circuit

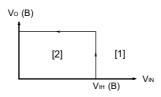

## $\bigcirc\,$ At the time of a $V_{IN}$ fall

As shown in Figure 1.1-8, set an equivalent circuit. If the pin 1 terminal voltage (V<sub>1</sub>) is higher than V<sub>R</sub>, the internal circuit operates as shown in Figure 1.1-10; the transistor at pin 6 is turned on. V<sub>O</sub> (B) provides an L output, which corresponds to the [1] range in Figure 1.1-9.

The transistor at pin 7 is turned off, so that no current will flow at point P of  $R_6$ . In this case, the Figure 1.1-8 and Figure 1.1-11 circuits are equivalent.

## Figure 1.1-9 Output operation of Comp. B (during a $V_{IN}$ fall)

## Figure 1.1-10 Circuit operation of Comp. B with pin 1 terminal voltage higher than V<sub>R</sub>

Figure 1.1-11 Equivalent circuit of Comp. B under  $V_1 > V_R$  condition

From Figure 1.1-11 the threshold voltage,  $V_{\text{IL}}$  (B), may be expressed as follows.

$$V_{IL}(B) = (1 + \frac{R_4}{R_5})V_R$$

## $\bigcirc$ At the time of a V<sub>IN</sub> rise

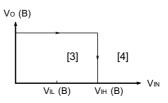

As the value of V<sub>IN</sub> is increased gradually, the internal circuit operates as shown in Figure 1.1-13, when the pin 1 terminal voltage is lower than V<sub>R</sub> (this corresponds to the [3] range in Figure 1.1-12). This turns off the internal transistor at pin 6 and turns on the internal transistor at pin 7. In this case, the Figure 1.1-8 and Figure 1.1-14 circuits are equivalent.

## Figure 1.1-12 Output operation of Comp. B (during a VIN rise)

## Figure 1.1-14 Equivalent circuit of Comp. B under V<sub>1</sub> < V<sub>R</sub> condition

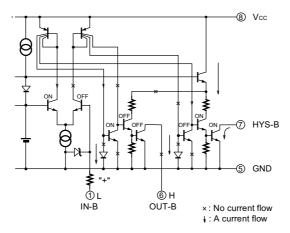

As shown in Figure 1.1-14 , when pin 7 changes to the L level, current  $I_4$  flowing through  $R_4$  branches into current I6 flowing through  $R_6$  and current  $I_5$  flowing through  $R_5$ . This reduces the R5-based voltage drop by the  $I_6$  equivalent, thus lowering the  $V_1$  voltage level.

Causing another output reverse under the V<sub>1</sub> > V<sub>R</sub> condition requires a much higher value of V<sub>IN</sub>, which is higher the value of V<sub>IN</sub> available during the change from [1] to [2] in Figure 1.1-9, resulting in the V<sub>1</sub> = V<sub>R</sub> relationship (refer to the description of hysteresis characteristics).

Under these conditions, the following equation applies.

$$\frac{V_{1N} - V_1}{R_4} = \frac{V_1}{R_6} + \frac{V_1}{R_5}$$

When  $V_1 = V_R$ ,  $V_{IN}$  satisfies the  $V_{IN} = V_{IH}$  (B) relationship. As the value of  $V_{IN}$  undergoes a gradual increase, therefore, the value of detection value,  $V_{IH}$  (B), may be expressed by the following equation.

$$V_{IH}(B) = (1 + \frac{R_4}{R_5 / / R_6}) \times V_R$$

## 1.2 How to Add Hysteresis Characteristics

It is possible to add hysteresis characteristics to Comparators A and B (Comp. A and Comp. B) that are housed in the MB3761.

- Related data sheet(s): Application Examples Addition of Hysteresis (Page 6)

- How to add hysteresis characteristics to Comp. A

## $\bigcirc$ When V<sub>3</sub> < V<sub>R</sub>

There is no current flowing out at pin (2) because the internal transistor at pin (2) shown in Figure 1.2-1 is off. This is equivalent to the Figure 1.2-2 circuit; therefore, the detection voltage may be expressed by the following equation.

$$V_{IH}(A) = (1 + \frac{R_1 + R_2}{R_3})V_R$$

## $\bigcirc$ When V<sub>3</sub> > V<sub>R</sub>

The internal transistor at pin (2) shown in Figure 1.2-1 is turned on, so that  $V_2$  is nearly equal to  $V_{CC}$ . This is equivalent to the Figure 1.2-3 circuit; therefore, the detection voltage may be expressed by the following equation.

$$V_{IL}(A) = (1 + \frac{R_2}{R_3})V_R$$

Figure 1.2-3 Equivalent circuit of Comp. A under V<sub>3</sub> > V<sub>R</sub> condition

■ How to add hysteresis characteristics to Comp. B

## $\bigcirc$ When V<sub>1</sub> > V<sub>R</sub>

The internal transistor at pin (7) shown in Figure 1.2-4 is off and an equivalent circuit is given in Figure 1.2-5. When the internal output transistor at pin (6) is turned on, the output level changes to L.

The detection voltage may be expressed by the following equation.

$$V_{IL}(B) = (1 + \frac{R_1}{R_2 + R_3})V_R$$

## $\bigcirc$ When V<sub>1</sub> < V<sub>R</sub>

Because the internal transistor at pin (7) shown in Figure 1.2-4 is on, the output level changes to L; an equivalent circuit is given in Figure 1.2-6. When the internal output transistor at pin (6) is turned off, the output level changes to H.

The detection voltage may be expressed by the following equation.

$$V_{IH}(B) = (1 + \frac{R_1}{R_2})V_R$$

Figure 1.2-6 Equivalent circuit of Comp. B under  $V_1 < V_R$  condition

## **1.3** How to Search for Power Voltage Malfunctions [1]

This section explains how to search for malfunctions in power voltage using the MB3761.

Related data sheet(s): Application Examples - Voltage Detection for Alarm (Page 7)

■ How to search for power voltage malfunctions [1]

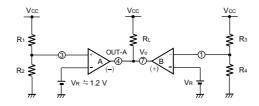

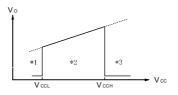

## \*1: When V<sub>CC</sub> < V<sub>CCL</sub>

When the output at pin (4) in Comp. A changes to H, VO changes to L. When the output at pin (7) in Comp. B changes to L,  $V_O$  changes to L.

As the detection voltage in Comp. B,  $V_{CCL}$  may be expressed by the following equation.

$$V_{\text{CCL}} = (1 + \frac{R_3}{R_4})V_{\text{R}}$$

## \*2: When V<sub>CC</sub> < V<sub>CCL</sub> <V<sub>CCH</sub>

When the output at pin (4) in Comp. A changes to H,  $V_{\rm O}$  changes to H.

When the output at pin (7) in Comp. B changes to H, V<sub>O</sub> changes to H.

## \*3: When $V_{CC} > V_{CCH}$

When the output at pin (4) in Comp. A changes to L,  $V_O$  changes to L.

When the output at pin (7) in Comp. B changes to H,  $V_O$  changes to L.

As the detection voltage in Comp. A,  $V_{CCH}$  may be expressed by the following equation.

$$V_{CCH} = (1 + \frac{R_1}{R_2})V_R$$

## 1.4 How to Search for Power Voltage Malfunctions [2]

This section explains how to search for malfunctions in power voltage using the MB3761.

- Related data sheet(s): Application Examples Voltage Detection for Alarm (Page 7)

- How to search for power voltage malfunctions [2]

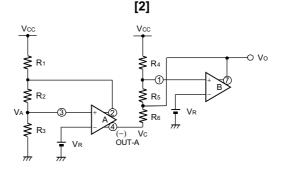

## [1]:

At a high value of V<sub>CC</sub>, if the V<sub>R</sub> < V<sub>A</sub> relationship is met, the output of Comp. A changes to the L level and the value of V<sub>B</sub> depends on the R<sub>3</sub> and R<sub>4</sub> combination.

## [2]:

When  $V_B < V_R$ , the output of Comp. B changes to the L level.

## [3]:

If the value of  $V_{CC}$  decreases and the  $V_R > V_A$  relationship is met, the OUT-A output changes to H and the output of Comp. B also changes to H.

## 1.4 How to Search for Power Voltage Malfunctions [2]

[How Comp. B works]

○ When pin (4) of OUT-A is at the L level

\*1:  $V_{CC} > \frac{R_3 + R_4}{R_4} \times V_R$  --- Theoutput Vo changes to the H level. \*1:  $V_{CC} < \frac{R_3 + R_4}{R_4} \times V_R$  --- Theoutput Vo changes to the L level.

## ○ When pin (4) of OUT-A is at the H level

The output Vo changes to the H level.

## [How Comp. A works]

- \*2:  $V_{CC} > \frac{R_1 + R_2}{R_2} \times V_R$  --- TheOUT A output changes to the L level. \*2:  $V_{CC} < \frac{R_1 + R_2}{R_2} \times V_R$  --- TheOUT A output changes to the H level.

## 1.5 Programmable Zener

## This section explains programmable Zener that use the MB3761.

- Related data sheet(s): Application Examples Programmable Zener (Page 8)

- Programmable Zener

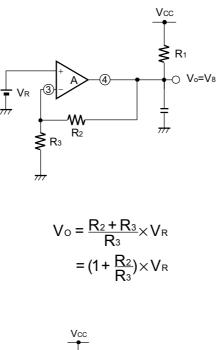

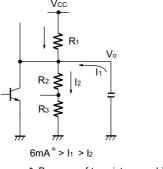

# 1.6 Calculation in Sample Circuit for Resetting Reduced Voltage

This section explains equations regarding a sample circuit used for resetting reduced voltage using the MB3761.

- Related data sheet(s): Application Examples Recovery Reset Circuit (Page 8)

- Calculation in sample circuit used for resetting reduced voltage

[How to calculate  $V_{CC}$  (H) and  $V_{CC}$  (L)]

## CHAPTER 1 MB3761 Applications

How to calculate  $V_{CC}$  (H):

$$\frac{(R_2 + R_3)//R_4}{R_1 + (R_2 + R_3)//R_4} V_{CC} = V_X \quad \dots \quad (a)$$

From (a) and (b), you get the following equation

$$\frac{\frac{(R_2+R_3)R_4}{R_2+R_3+R_4}}{R_1+\frac{(R_2+R_3)R_4}{R_2+R_3+R_4}}V_{\text{CC}} = \frac{R_2+R_3}{R_3}V_{\text{TH}}$$

$$\frac{(R_2 + R_3)R_4}{R_1(R_2 + R_3 + R_4) + (R_2 + R_3)R_4}V_{CC} = \frac{R_2 + R_3}{R_3}V_{TH}$$

$$V_{\rm CC}(H) = \frac{R_1(R_2 + R_3 + R_4) + (R_2 + R_3)R_4}{R_3R_4} V_{\rm TH}$$

$$= \frac{R_1(R_2 + R_3)}{R_3R_4} V_{\rm TH} + \frac{(R_1 + R_2 + R_3)R_4}{R_3R_4} V_{\rm TH}$$

$$= \frac{R_1(R_2 + R_3)}{R_3R_4} V_{\rm TH} + V_{\rm CC}(L)$$

How to calculate V<sub>CC</sub> (L):

$$\frac{R_3}{R_1 + R_2 + R_3} V_{CC} = V_{TH} \quad ---(C)$$

From (c), you get the following equation

$$V_{\rm CC}(L) = \frac{R_1 + R_2 + R_3}{R_3} V_{\rm TH}$$

## 1.7 How to Search for Malfunctions in Power Voltage with Hysteresis Characteristics [1]

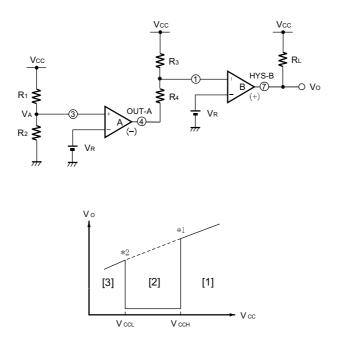

This section explains how to search for malfunctions in power voltage with hysteresis characteristics using the MB3761.

- Related data sheets: Operational Definitions (Page 4) Application Examples - Voltage Detection for Alarm (Page 7)

- How to search for malfunctions in power voltage with hysteresis characteristics [1]

See Figure 1.7-1 , which is a combination of the circuits in the Operational Definitions and Application Examples - Voltage Detection for Alarm data sheets. The detection voltage may be expressed by the following equation.

$$V_{IL}(B) = (1 + \frac{R_4}{R_5}) \times V_R$$

$$V_{IL}(B) = (1 + \frac{R_4}{R_5//R_6}) \times V_R$$

$$V_{IL}(A) = (1 + \frac{R_4}{R_2//R_3}) \times V_R - \frac{R_4}{R_3} \times V_{CC}$$

$$V_{IL}(A) = (1 + \frac{R_1}{R_2}) \times V_R$$

Note:

Check for proper operation by considering factors such as current consumption, each terminals' maximum rating, and recommended operating conditions. Then, set the resistance values.

# Figure 1.7-1 Sample circuit detecting for malfunctions in power voltage with hysteresis characteristics [1]

## 1.8 How to Search for Malfunctions in Power Voltage with Hysteresis Characteristics [2]

This section explains how to search for malfunctions in power voltage with hysteresis characteristics using the MB3761.

- Related data sheets: Application Examples-Addition of Hysteresis (Page 6)

Application Examples-Voltage Detection for Alarm (Page 7)

- How to search for malfunctions in power voltage with hysteresis characteristics [2]

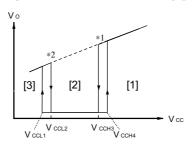

See Figure 1.8-1 , which is a modification of the circuits in the Addition of Hysteresis and Application Examples - Voltage Detection for Alarm data sheets. Comp. A detects for malfunctions in V<sub>CCL1</sub> and V<sub>CCL2</sub>; and Comp. B for V<sub>CCH3</sub> and V<sub>CCH4</sub>.

The detection voltage may be expressed by the following equations.

$$V_{CCL1} = (1 + \frac{R_2}{R_3}) \times V_R$$

$$V_{CCL2} = (1 + \frac{R_1 + R_2}{R_3}) \times V_R$$

$$V_{CCH3} = (1 + \frac{R_4}{R_5 + R_6}) \times V_R$$

$$V_{CCH4} = (1 + \frac{R_4}{R_5}) \times V_R$$

Note:

If the desired detection voltage is relatively high, the voltage at pin (7) is small, depending on the resistance ratio. Therefore, the above method is not applicable when it is not possible to detect the system side as H level at the specified smoll voltage.

For more details, refer to the section 1.2, "How to Add Hysteresis Characteristics" and section 1.4, "How to Search for Power Voltage Malfunctions [2]."

## Figure 1.8-1 Sample circuit detecting for malfunctions in power voltage with hysteresis characteristics

Figure 1.8-2 Output operation of sample circuit detecting for malfunctions in power voltage with hysteresis characteristics [2]

## 1.9 How to Troubleshoot the MB3761

## This section explains how to troubleshoot the MB3761.

### ■ How to troubleshoot the MB3761

- 1. If there are output fluctuations

- You may encounter output fluctuations when the input change speed is low. For details, refer to the sub section 1.9.1, "If there are output fluctuations."

- 2. If hysteresis characteristics are not appropriate

- Depending on the setting of resistance values, the measurement of the lower detection voltage may be higher than the setting. For details, refer to the sub section 1.9.2, "If hysteresis characteristics are not appropriate."

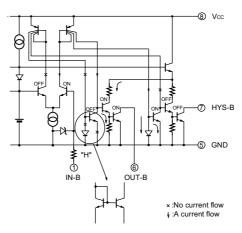

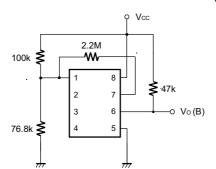

## **1.9.1** If there are output fluctuations

## You may encounter output fluctuations when the input change speed is low.

### If there are output fluctuations

#### [Probable causes]

- Because of the offset between the output OUT-B and HYS-B in comparator B (Comp. B), OUT-B may change to the H level before HYS-B changes to the L level at the falling edge of the input IN-B.If this occurs, the OUT-B output will become unstable because of noise to IN-B or the "2." reason below.By contrast, the circuit configuration of comparator A (Comp. A) will cause little output offset.

- A switch between the outputs of Comp. B or Comp. A will cause a slight fluctuation in the internal reference voltage or comparator offset. The fluctuation in an extremely narrow voltage range in IN-B or IN-A is attributable to the common impedance inside the ICs.

### [Corrective action]

- Such an unstable output will usually take place in a slight input voltage range. Therefore, this

phenomenon is not seen if the input change speed is high (refer to Figure 1.9-1). At a low

input change speed, it is recommended that you use Comp. A; refer to "1." in [Probable

causes]. Even when you use Comp.A, however, you may encounter a similar phenomenon if

the speed is extremely high. Careful experimentation and validation is necessary.

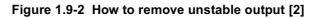

- 2. In case you use Comp.B with signals whose input change speed is low, it is recommended that you reverse OUT-B through an external transistor for hysteresis characteristics (refer to the Figure 1.9-2).

### Figure 1.9-1 How to remove unstable output [1]

3. When you remove any unstable output resulting from "2." in [Probable causes] above, it is recommended that you insert a capacitor into the output in order to acquire sufficient time for hysteresis to work, and to eliminate the unstable output.

## 1.9.2 If hysteresis characteristics are not appropriate

When you set the resistance values according to the Application Examples data sheets, the measurement of the lower detection voltage may be higher than the setting, depending on the setting of resistance values.

• Related data sheet(s): Application Examples - Addition of Hysteresis (Page 6)

#### ■ If hysteresis characteristics are not appropriate

#### [Probable cause and corrective action]

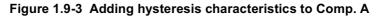

See Figure 1.9-3 , which shows the operating principle of comparator A (Comp. A) in the Addition of Hysteresis data sheet. Depending on whether or not there is current I from pin 2, the value of V<sub>2</sub> voltage switches to produce hysteresis characteristics. The equation regarding V<sub>IL</sub> (A) shown in the particular data sheet neglects any voltage drop through R<sub>1</sub>. In reality, however, there is a small current of approximately 80µA and the R<sub>1</sub>-based voltage drop cannot be neglected depending on the resistance value. There may be difference between the calculated and measured values. (When V<sub>3</sub> is greater than V<sub>R</sub>, the internal transistor at pin (2) is turned on. The value of V<sub>IL</sub> (A) is calculated assuming that V<sub>2</sub> is nearly equal to V<sub>CC</sub>.

Tip:

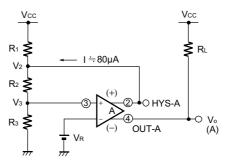

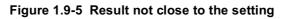

When the values of detection are set as  $V_{IH}$  (A) = 36V and  $V_{IL}$  (A) = 30V, resistance selection reveals differences in detection measurement, as shown in Figure 1.9-4 and Figure 1.9-5. The width of hysteresis is seen to become smaller as the resistance changes.

Figure 1.9-4 Result close to the setting

(R1=100k, R2=480k, R3=20k, RL=11k)

(R1=11k, R2=4.7k, R3=200W, RL=11k)

# 1.10 Q&A Set Regarding the MB3761

This section provides a set of questions and answers regarding the MB3761.

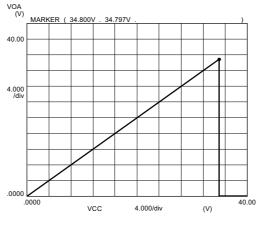

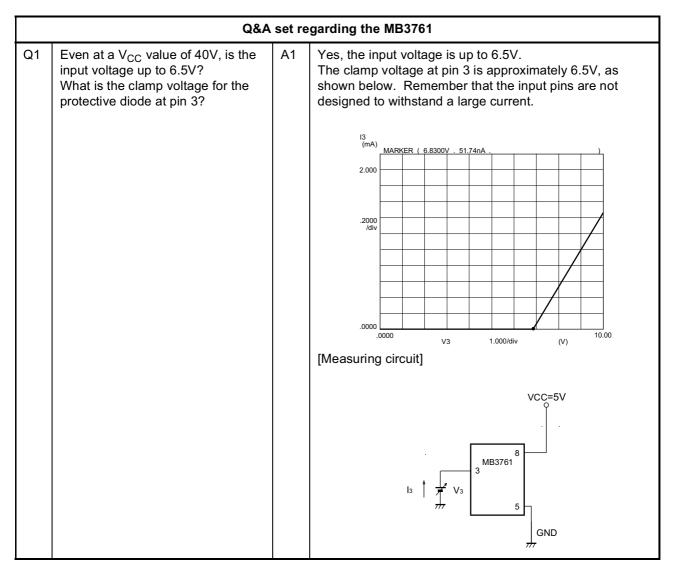

### Q&A set regarding the MB3761

#### 1.10 Q&A Set Regarding the MB3761

CHAPTER 1 MB3761 Applications

# CHAPTER 2 MB3771 Applications

### This chapter provides applications regarding the MB3771.

- 2.1 Equations for Calculating External Fine-tuning Types

- 2.2 Monitoring Arbitrary Power Voltage (for Vcc smaller than or equal to 18V Relationship )

- 2.3 Monitoring Arbitrary Power Voltage (for 5V constant voltage output)

- 2.4 Monitoring Power Voltages of 5V and 12V

- 2.5 Monitoring Power Voltage with Delayed Trigger

- 2.6 Monitoring Negative Power Supply

- 2.7 Generating Reference Voltage and Monitoring Voltage Drops [1]

- 2.8 Generating Reference Voltage and Monitoring Voltage Drops [2]

- 2.9 Detecting Low Voltage and Excess Voltage

- 2.10 Reset Output

- 2.11 Handling Unused Terminals

- 2.12 Q&A Set Regarding the MB3771

- 2.13 Equivalent Circuits for MB3771 Input/output Unit

## 2.1 Equations for Calculating External Fine-tuning Types

It is possible to externally adjust the VSA detection voltage.

Related data sheet(s): Application Examples-Power Supply Monitor with External Adjust (Page 7)

#### Equations for calculating external fine-tuning types

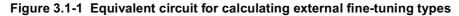

#### Figure 2.1-1 Equivalent circuit for calculating external fine-tuning types

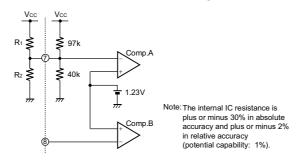

In Figure 2.1-1 , R<sub>A</sub> is a combined resistance between the 97k $\Omega$  and external R<sub>1</sub> resistance; R<sub>B</sub> is a combined resistance between the 40k $\Omega$  and external R<sub>2</sub> resistance.

$$R_{A} = R_{1} \times 97 k\Omega / (R_{1} + 97 k\Omega) [\Omega]$$

$$R_{B} = R_{2} \times 40 k\Omega / (R_{2} + 40 k\Omega) [\Omega]$$

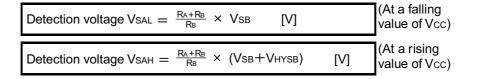

The detection voltage may be calculated as follows.

The above calculation assumes that the threshold level of comparator B is  $V_{SB}$  equal to 1.230V (typ.) and that the width of hysteresis is  $Y_{HSYB}$  equal to 28mV (typ.).

If you choose appropriate values of  $R_1$  and  $R_2$  so that they meet the  $R_1 \ll 97k$  and  $R_2 \ll 40k$  relations, you get simpler equations for determining the detection voltage.

| Detection voltage V <sub>SAL</sub> $\doteq \frac{R_A + R_B}{R_B} \times V_{SB}$ [V] |     | (At a falling value of Vcc) |

|-------------------------------------------------------------------------------------|-----|-----------------------------|

| Detection voltage VsAH $\doteq \frac{RA+RB}{RB} \times (V_{SB}+V_{HYSB})$           | [V] | (At a rising value of Vcc)  |

#### Note:

The minimum of power voltage for the MB3771 is 3.5V. Therefore, you must set a detection value higher than 3.5V. The method of external adjustment using either  $R_1$  or  $R_2$  is not recommended because of poor accuracy in detection voltage.

#### 2.1 Equations for Calculating External Fine-tuning Types

#### ■ Details of calculating external fine-tuning types (calculating maximum value)

|                     | Parameter                                                                                                              |    | Тур.   | Numerical values for maximum calculation            |

|---------------------|------------------------------------------------------------------------------------------------------------------------|----|--------|-----------------------------------------------------|

| Resistance          | R <sub>1</sub>                                                                                                         |    | 9.1k   | 9.191k(+1%)                                         |

|                     | R <sub>2</sub>                                                                                                         |    | 3.3k   | 3.267k(-1%)                                         |

|                     | R'                                                                                                                     |    | 97k    | 126.1k(30%)                                         |

|                     | R"                                                                                                                     |    | 40k    | 51.2k (28%) Relative accuracy of at least 2%        |

| Combined resistance | $R_{A} = \frac{R_{1 \times R'}}{R_{2} + R'}$                                                                           | *1 | 8.3195 | $\frac{9.191 \times 126.1}{9.191 + 126.1}$ = 8.5666 |

|                     | $\mathbf{R}_{\mathrm{B}} = \frac{\mathbf{R}_{2\times\mathbf{R}^{\mathrm{m}}}}{\mathbf{R}_{2}+\mathbf{R}^{\mathrm{m}}}$ | *2 | 3.0485 | $\frac{3.267 \times 51.2}{3.267 + 51.2} = 3.0710$   |

|                     | Ra + RB<br>RB                                                                                                          | *3 | 3.7290 | $\frac{8.5666 \times 3.0710}{3.0710} = 3.7895$      |

| Reference           | V <sub>SB</sub> (Reference)                                                                                            |    | 1.230V | 1.248V(Standard value)                              |

| voltage             | V <sub>HYSB</sub> (Hysteresis)                                                                                         |    | 0.028V | 0.042V(Standard value)                              |

| Detection           | V <sub>SAL</sub>                                                                                                       |    | 4.59V  | 3.7895×1.248= <b>4.729V</b>                         |

| voltage *4          | V <sub>SAH</sub>                                                                                                       |    | 4.69V  | 3.7895×(1.248?0.042)= <b>4.888V</b>                 |

Table 2.1-1 Details of calculating external fine-tuning types (calculating maximum value)

\*1: RA becomes the maximum when R1 and R' are the maximum.

\*2:  $R_B$  becomes the minimum when  $R_2$  and R'' are minimum.

\*3:  $\frac{R_{A}+R_{B}}{R_{B}}$  becomes the maximum when  $R_{A}$  is the maximum, and  $R_{B}$  is minimum.

\*4: If fluctuations in reference and hysteresis are not considered, the values of  $V_{\text{SAL}}$  and  $V_{\text{SAH}}$

may be calculated as follows.

Vsal=3.7895 × 1.23=4.66V Vsah=3.7895 × (1.23+0.028)=4.77V

# 2.2 Monitoring Arbitrary Power Voltage (for V<sub>CC</sub> smaller than or equal to 18V Relationship)

This section describes how to monitor the power voltage in the V<sub>CC</sub> smaller than or equal to 18V range by means of the MB3771. As the boundary is V<sub>CC</sub> = 4.45V, pin 7 is handled differently in the following method.

Related data sheet(s): Application Examples-Arbitrary Voltage Supply Monitor Case (V<sub>CC</sub> smaller than or equal to 18V) (Page 7)

#### Monitoring arbitrary power voltage (for V<sub>CC</sub> smaller than or equal to 18V relationship)

Figure 2.2-1 Equivalent circuit for monitoring arbitrary power voltage

Only when outputs from comparators A and B (Comp. A and Comp. B) are both at the L level, the reset will provide an H output. When monitoring arbitrary power voltage under the  $V_{CC}$  smaller than or equal to 18V relationship, you should set the output of Comp. A so that it will always remain at the L level; Comp. B is responsible for monitoring the voltage.

The value of V<sub>SAH</sub> is required to be 4.45V (maximum) under the temperature conditions: Ta = -40°C to + 85°C. At a V<sub>CC</sub> value of at least 4.45V, Comp. A will always provide an output at the L level, even if temperature fluctuations are taken into account (this means that at V<sub>CC</sub> smaller than or equal to 4.45V, Comp. A will be ineffective). Therefore, pin 7 can be made open if the detection voltage is set at 4.45V or a higher value.

In case the detection voltage is lower than 4.45V, it is necessary to connect pin 7 to  $V_{CC}$  so that only the output of Comp. B will be effective (The output of Comp. A may be nullified by setting pin 7 at a value higher than the  $V_{SA}$  voltage).

The detection voltage may be calculated as follows.

| Detection voltage = $\frac{R_1 + R_2}{R_2} \times V_{SB}$ [V] |                    |  |  |  |  |

|---------------------------------------------------------------|--------------------|--|--|--|--|

| VsB : At a falling value of Vcc 1.23V(Typ.)                   |                    |  |  |  |  |

| At a rising value of Vcc 1.23V(Typ.)+28mV(Hyst                | eresis equivalent) |  |  |  |  |

Note:

The minimum of power voltage for the MB3771 is 3.5V. Therefore, you must set a detection value higher than 3.5V.

# 2.3 Monitoring Arbitrary Power Voltage (for 5V constant voltage output)

This section describes how to provide an output of 5V constant voltage by means of the MB3771.

- Related data sheet(s): Application Examples Arbitrary Voltage Supply Monitor Case (V<sub>CC</sub> > 18V) (Page 8)

- Monitoring arbitrary power voltage (for 5V constant voltage output)

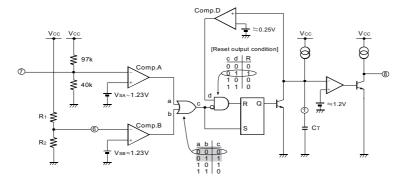

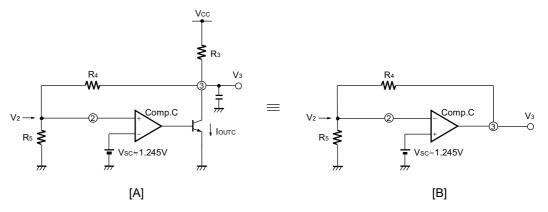

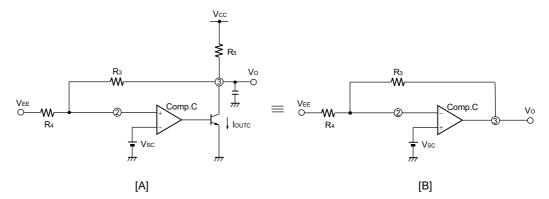

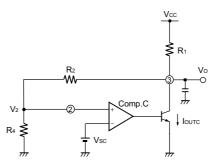

In Figure 2.3-1 [A], comparator C (Comp. C) is used as an operational amplifier to produce a constant voltage output. Because of an open collector output, the transistor is given an  $R_3$  pull-up. The output capacitor is used to reduce ripples.

See Figure 2.3-1 [B], which shows an equivalent circuit of [A]; it is a constant voltage power circuit (By equivalent, it means that pin 3 provides an output at the L level when the voltage at pin 2 is higher than  $V_{SC}$ ). The relationship between  $V_2$ , the voltage at pin 2 and  $V_3$ , the voltage at pin 3, is as follows.

$$V_3 = V_2 \times (1 + \frac{R_4}{R_5})$$

[V]

For example, when  $R_4$  is  $100k\Omega$  and R5 is  $100k\Omega$ ,  $V_3$  is nearly equal to 5V. The value of  $V_3$  is usually used as the power voltage for the MB3771.

#### How to determine R3 (when V<sub>CC</sub> = 140V)

In Figure 2.3-1 [A], the transistors output current  $I_{OUTC}$  is set at a maximum of 6mA. It is necessary to determine a resistance value that will prevent the output current from exceeding the maximum value even at a maximum value of  $V_{CC}$

$$(140V - 5V) / 6mA = 22.5 [k\Omega]$$

Therefore, the value of  $\mathsf{R}_3$  should be set to at least 22.5k $\Omega.$

Because the maximum of resistance depends on the output current, you should consider load conditions when attempting to set an optimum value.

When  $R_3$  is 110k $\Omega$ , for example, the value of a current flowing through  $R_3$  is as follows.

$$(140V - 5V) / 110k\Omega = 1.2 \text{ [mA]}$$

To obtain constant voltage on a stable basis, it is also necessary to set the current flowing out at pin 3 to a value not higher than 0.2mA by considering the values of  $I_{OUTC}$  and  $I_{CC}$ .

### 2.4 Monitoring Power Voltages of 5V and 12V

This section describes how to monitor the power voltages of 5V and 12V by means of the MB3771.

- Related data sheet(s): Block Diagram (Page 3); Application Examples 5V and 12V Power Supply Monitor (Page 9)

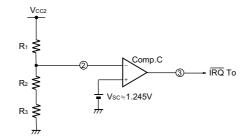

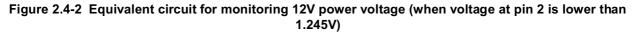

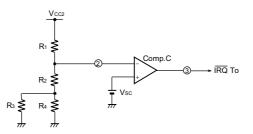

- Monitoring 12V power voltage

Figure 2.4-1 Equivalent circuit for monitoring 12V power voltage (when voltage at pin 2 is higher than 1.245V)

When the voltage at pin 2 is higher than 1.245V, the output of Comp. C in the Diagram data sheet changes to the H level. Because the internal transistor at pin 3 is turned on, the output at pin 3 changes to the L level. In this case, the external transistor shown in the Application Examples data sheet is turned off and an equivalent circuit shown in Figure 2.4-1 is applicable.

The detection voltage may be expressed by the following equation.

$$V_{SCL} = \frac{R_1 + R_2 + R_3}{R_2 + R_3} \times V_{SC}$$

When the voltage at pin 2 is lower than 1.245V, the output of Comp. C in the Diagram data sheet changes to the L level. Because the internal transistor at pin 3 is turned off, the output at pin 3 changes to the H level. In this case, the external transistor shown in the Application Examples data sheet is turned on and an equivalent circuit shown in Figure 2.4-2 is applicable.

The detection voltage may be expressed by the following equation.

#### CHAPTER 2 MB3771 Applications

$$V_{SCH} = \frac{R_1 + R_2 + R_3 //R_4}{R_2 + R_3 //R_4} \times V_{SC}$$

The hysteresis width  $\mathrm{V}_{\mathrm{HYSC}}$  may be expressed by the following equation.

$$V_{HYSC} = V_{SCH} - V_{SCL}$$

$$= \frac{R_4(R_3 - R_3 / / R_4)}{(R_1 + R_2) (R_2 + R_3 / / R_4)} \times V_{SC}$$

### ■ Monitoring 5V power voltage

Comp. A is responsible for monitoring the 5V power voltage.

### Figure 2.4-3 Equivalent circuit for monitoring 5V power voltage

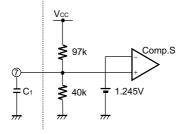

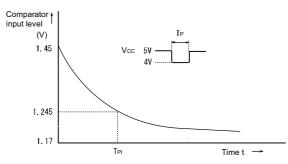

### 2.5 Monitoring Power Voltage with Delayed Trigger

This section describes how to monitor the power voltage with a delayed trigger by means of the MB3771.

- Related data sheet(s): Application Examples Power Supply Monitor with Delayed Trigger (Page 10)

- Monitoring power voltage with delayed trigger

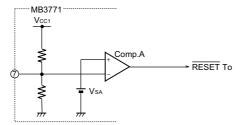

Figure 2.5-1 Equivalent circuit for monitoring power voltage with delayed trigger

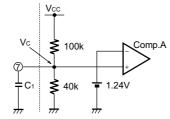

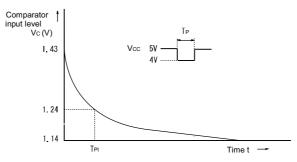

When the value of V<sub>CC</sub> changes from 5V to 4V, a part of the charge stored in capacitor C is discharged to GND through the 40k $\Omega$  resistor (refer to Figure 2.5-1).

The voltage level at pin 7 changes as shown in Figure 2.5-2 . The detection time  $T_{PI}$  may be determined by equation (b).

It is possible to calculate the comparators input voltage V<sub>C</sub> from equation (a).

$$V_{c} = \left(\frac{40k}{100k + 40k} \times 5V - \frac{40k}{100k + 40k} \times 4V\right) \times e^{-tpl/40k.C1} + \frac{40k}{100k + 40k} \times 4V \quad ---(a)$$

Using equation (a), TPI may be expressed as follows.

$T_{PI}[\mu s] = 4 \times 10^{-2} \times C_1$  ---(b)

#### [Example]

When  $C_1$  is 1000pF,  $T_{PI}$  is equal to 40µs.

#### Tip:

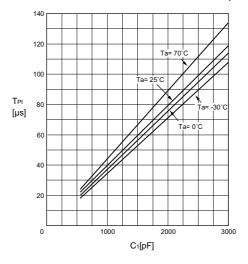

Measurements of detection time  $T_{PI}$  are plotted below. It should be noted that these are for reference only; they are not guaranteed values.

(Potentially, the diffused resistor has a fluctuation of plus or minus 20% and the reference voltage has a fluctuation of plus or minus 5%; therefore, it is necessary to allow  $T_{Pl}$  a fluctuation of plus or minus 30% in addition to the  $C_1$  fluctuation).

Figure 2.5-3 Measurements of detection time TPI (reference only)

# 2.6 Monitoring Negative Power Supply

This section describes how to monitor the negative power supply by means of the MB3771.

- Related data sheet(s): Application Examples 5V and Arbitrary Negative Voltage Monitor (Page 10)

- Monitoring negative power supply

Figure 2.6-1 Equivalent circuit for monitoring negative power supply [1]

Figure 2.6-2 Equivalent circuit for monitoring negative power supply [2]

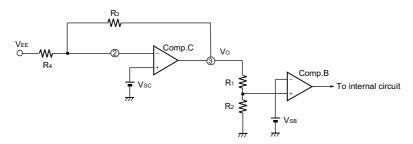

In Figure 2.6-1 [A], Comp. C is used as an operational amplifier. Because of an open collector output, the transistor is given an  $R_5$  pull-up. The output capacitor is used to reduce ripples.

See Figure 2.6-1 [B], which shows an equivalent circuit of [A]; it is a reverse amplifier circuit. Using V<sub>SC</sub> as the threshold voltage of Comp. C and V<sub>SL</sub> as the detection value for the negative power supply V<sub>EE</sub>, the output V<sub>O</sub> (voltage at pin 3) of Comp. C may be expressed by the following equation.

$$V_{o} = V_{sc} - \frac{(V_{sL} - V_{sc})}{R_4} \cdot R_3 \quad [V] \quad \dots \quad (a)$$

### CHAPTER 2 MB3771 Applications

As shown in Figure 2.6-2,  $R_1$  and  $R_2$  are used to divide the  $V_O$  voltage and the resulting values are detected by Comp. B. Using  $V_{SB}$  as the threshold voltage of Comp. B,  $V_O$  may be expressed as follows.

$$V_0 = \frac{R_1 + R_2}{R_2} \cdot V_{SB} [V] --- (b)$$

Lets assume that  $R_1 = R_2 = R_3$  and that  $V_{SB}$  is nearly equal to  $V_{SC}$ . From equations (a) and (b),  $V_{SL}$  may be expressed as follows.

| $V_{SL} = V_{SB} (1 - R_4 / R_3)$ | [V]        |

|-----------------------------------|------------|

| VsB : At a falling value of Vcc   | 1.23V      |

| At a rising value of Vcc          | 1.23V +28m |

#### [Example]

Lets use the following conditions:  $R_1 = R_2 = R_3 = 20k\Omega$ ;  $R_4 = 183k\Omega$ ; and  $V_{SB} = 1.23V$ . In this case, the detection voltage  $V_{SL}$  is equal to -10V.

# 2.7 Generating Reference Voltage and Monitoring Voltage Drops [1]

This section describes how to generate reference voltage and monitor voltage drops by means of the MB3771.

- Related data sheet(s): Application Examples Reference Voltage Generation

- and Voltage Sagging Detection 9V Reference Voltage Generation and 5V/9V Monitoring (Page 11) Application Examples - Reference Voltage Generation and Voltage Sagging Detection - 5V Reference Voltage Generation and 5V Monitoring (Page 12)

- Generating 9V and monitoring 5V/9V

Figure 2.7-1 Equivalent circuit for reference voltage generation and voltage drop detection [1] (generating 9V and monitoring 5V/9V)

Figure 2.7-2 Equivalent circuit for reference voltage generation and voltage drop detection [2] (generating 9V and monitoring 5V/9V)

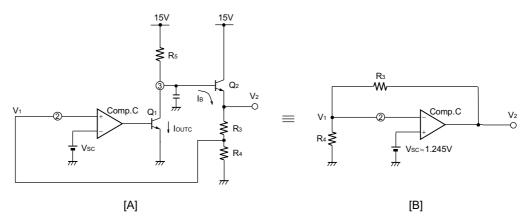

In Figure 2.7-1 [A], Comp. C is used as an operational amplifier to produce an constant voltage output. Because of an open collector output, the transistor  $(Q_1)$  at pin 3 is given an  $R_5$  pull-up. The external capacitor at pin 3 is used to reduce ripples.

$I_{OUTC}$  is specified up to 6mA. Therefore,  $R_5$  should be set to higher than 25k $\!\Omega$  resistor under 15V/6mA condition.

See Figure 2.7-1 [B], which shows a simpler equivalent circuit of [A]; it is a low voltage power circuit. Using  $V_1$  as the voltage at pin 2 and  $V_2$  as the output voltage, the following equation applies.

$$V_2 = V_1 \times (1 + R_3 / R_4)$$

[V]

#### [Example]

Lets use the following conditions:  $R_3 = 7.5$ kW;  $R_4 = 1.2$ k $\Omega$ ; and  $V_{SC} = 1.245$ V. Because  $V_2$  is nearly equal to 9V, the value of  $V_2$  gives a 9V output.

See Figure 2.7-1 , in which Comp. B is used to detect divided voltage of the V<sub>2</sub> output from the constant voltage power circuit shown in Figure 2.7-1 [B]. The detection voltage V<sub>2SL</sub> for V<sub>2</sub> may be expressed as follows.

$$V_{2SL} = (R_1 + R_2) \times V_{SB} / R_2 [V]$$

#### [Example]

When  $R_1 = 300k\Omega$  and  $R_2 = 60k\Omega$ ,  $V_{2SL}$  is nearly equal to 7.2V.

#### Regarding the output current

The voltage at pin 3 is equal to the sum of the V<sub>2</sub> voltage and the V<sub>BE</sub> voltage at Q<sub>2</sub>: that is, 9V + 0.7V (assumed value). Therefore, it is nearly equal to 9.7V. As a result, the voltage drop by R5 is as follows.

15V-9.7V=5.3 [V]

The current flowing through R<sub>5</sub> (=  $3k\Omega$ ) is equal to 1.7mA by calculating  $5.3V/3k\Omega$ . Therefore, the current available from V<sub>2</sub> may be calculated as follows.

Output current from V2  $\doteq$  Base current IB at Q2  $\times$  Q2hFE - V2/(R3 + R4) - V2/(R1 + R2)

Assuming that the value of  $h_{FE}$  at  $Q_2$  is nearly equal to 100, the output current from  $V_2$  may be calculated as follows.

Output current from V2  $\approx$  1.76mA × 100-9V/(8.7k $\Omega$ )-9V/(62.3k $\Omega$ )  $\approx$  175 [mA]

#### Note:

For the sake of stable supply, the output current from  $V_2$  should be up to 50mA by considering fluctuations of the external transistor  $Q_2$ .

#### ■ Generating 5V and monitoring 5V (No. 1)

If you give the  $R_3 = 3.6k\Omega$  and  $R_4 = 3.6 k\Omega$  relationships to the explanation under the item, " Generating 9V and monitoring 5V/9V", you find that V<sub>2</sub> is a 5V output.

#### Note:

For the sake of stable supply, the output current from  $V_2$  should be up to 50mA by considering fluctuations of the external transistor  $\mathsf{Q}_2$

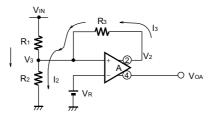

# 2.8 Generating Reference Voltage and Monitoring Voltage Drops [2]

This section describes how to generate reference voltage and monitor voltage drops by means of the MB3771.

• Related data sheet(s): Application Examples - Reference Voltage Generation and

Voltage Sagging Detection 5V Reference Voltage Generation and 5V Monitoring (No. 2) (Page 11) Application Examples - Reference Voltage Generation and Voltage Sagging Detection - 1.245V Reference Voltage Generation and 5V Monitoring (Page 12)

■ Generating 5V and monitoring 5V (No. 2)

Figure 2.8-1 Equivalent circuit for reference voltage generation and voltage drop detection [1] (generating 5V and monitoring 5V)

Figure 2.8-2 Equivalent circuit for reference voltage generation and voltage drop detection [2] (generating 1.245V and monitoring 5V)

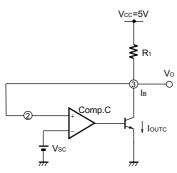

In Figure 2.8-1 , Comp. C is used as an operational amplifier to produce the constant voltage output. Because of the open collector output, the transistor ( $Q_1$ ) at pin 3 is given an  $R_1$  pull-up. The output capacitor is used to reduce ripples.

Using  $V_2$  as the voltage at pin 2 and Vo as the output voltage, the following equation applies.

$$V_0 = V_2 \times (1 + R_2 / R_3)$$

[V]

Let's use the following conditions:  $R_2 = 100k\Omega$ ;  $R_3 = 33k\Omega$ ; and  $V_{SC} = 1.245V$ . Because  $V_{SC}$  is nearly equal to  $V_2$ , the value of  $V_2$  is nearly equal to 5V.

#### [Example]

The value of  $I_{OUTC}$  is up to 6mA according to the standard. When  $V_{CC}$  = 40V, the value of  $R_1$  is as follows.

$$R_1 \ge (40V-5V)/6mA = 5.8 [k\Omega]$$

Taking the margin into consideration, use  $R_1 = 11K\Omega$ , the output current I is as follows.

$$I = (40V - 5V)/6k\Omega = 3.2 \text{ [mA]}$$

For the sake of stable supply, the output current should meet the I < 1.6mA relationship.

#### ■ Generating 1.245V and monitoring 5V

See Figure 2.8-2 , which shows a voltage follower circuit. In this case, output Vo is equal to  $V_{SC}$ .

#### [Example]

The value of  $I_{OUTC}$  is up to 6mA according to the standard. When  $V_{CC}$  = 5V, the value of  $R_1$  is as follows.

$$R_1 \ge (5V - 1.245V)/6mA = 0.6 [k\Omega]$$

#### Note:

See the data sheet: Application Examples - Reference Voltage Generation and Voltage Sagging Detection - 1.245V Reference Voltage Generation and 5V Monitoring. The  $0.47\mu$ F capacitor at pin 3 in the data sheet is intended to reduce ripples. Depending on the system, you should modify the capacitance.

### 2.9 Detecting Low Voltage and Excess Voltage

This section describes how to detect any low voltage or excess voltage by means of the MB3771.

- Related data sheet(s): Application Examples Detecting Low Voltage and Excess Voltage (V<sub>CC</sub> = 5V) (Page 12)

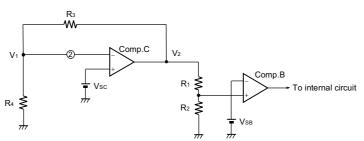

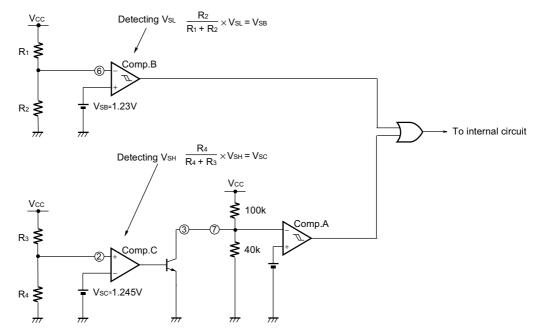

- Detecting Low Voltage and Excess Voltage

Figure 2.9-1 Equivalent circuit for detecting low voltage and excess voltage

$R_1$  and  $R_2$  are used to determine the value of  $V_{SL}.\ R_3$  and  $R_4$  are used to determine the value of  $V_{SH}.$

Comp. C has no hysteresis characteristics so that no hysteresis is given to  $V_{SH}$ .

When outputs from Comp. A and Comp. B are both at the L level, the reset will provide an H output. This assumes the  $V_{SL} < V_{CC} < V_{SH}$  relationship.

When V<sub>CC</sub> exceeds the value of V<sub>SH</sub>, Comp. C turns on the transistor at pin 3, reduces the voltage at pin 7 to a value close to GND, reverses the output of Comp. A, and changes the reset to the L level. If V<sub>CC</sub> is not higher than the value V<sub>SH</sub>, the transistor at pin 3 is off, so that pin 7 is essentially open. At a rising value of V<sub>CC</sub>, therefore, you should take care when making the value of V<sub>SL</sub> lower than V<sub>CC</sub> (4.2V typically), which is detected by the 100k $\Omega$  and 40k $\Omega$  resistors.

### 2.10 Reset Output

This section describes how to determine the timing for rest output, as well as related fluctuations.

Reset output

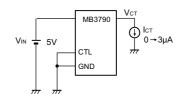

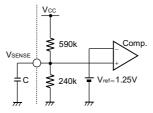

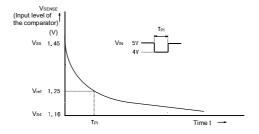

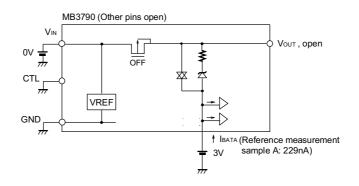

The width  $(T_{PO})$  of the RESET output pulse may be determined as follows.

$$T_{PO} = C_T \times V_1 / I_{CT}$$

You can get the following equation if you use typical values: that is, the threshold value (V<sub>1</sub>) is nearly equal to 1.24V and the charging current ( $I_{CT}$ ) at C<sub>T</sub> is nearly equal to 1.2µA.

$$T_{PO}[ms] = 100 \times C_T [\mu F]$$

Assuming that the value of  $C_T$  is constant, it is possible to determine the fluctuations of  $T_{PO}$  from the charging/discharging current  $I_{CT}$  and threshold voltage  $V_1$ . Fluctuations in charging/ discharging current are dependent mainly on fluctuations in the diffused resistance R inside the IC and fluctuations in reference voltage, as well as errors in the hfe value of the transistors comprising the current mirror.

Meanwhile, fluctuations in threshold voltage are dependent mainly on fluctuations in resistance and reference voltage. Generally speaking, fluctuations in TC resistance are plus or minus 20% (or 30%) when Ta =  $25^{\circ}$ C; they are plus or minus 40% when Ta is between minus 40°C and plus 85°C. The relative error of the transistor's hfe is approximately plus or minus 10%. For the MB3771, fluctuations in reference voltage are plus or minus 1.6% when Ta =  $25^{\circ}$ C; they are approximately plus or minus 3.2% when Ta is between minus 40°C and plus 85°C.

Assuming that the value of C<sub>T</sub> is constant, the values of T<sub>PO</sub> may be determined as follows.

$$T_{PO}(min.) \quad [ms] \doteq (100 \times 0.5) \times C_{T} \quad [\mu F]$$

$$T_{PO}(max.) \quad [ms] \doteq (100 \times 1.5) \times C_{T} \quad [\mu F]$$

If the value of  $C_{\rm T}$  has a fluctuation of plus or minus 20%, the values of  $T_{\rm PO}$  are as follows.

$$T_{PO}(\text{min.}) \quad [\text{ms}] \doteq (100 \times 0.5) \times (\text{C}_{T} \times 0.8) \quad [\mu\text{F}]$$

$$T_{PO}(\text{max.}) \quad [\text{ms}] \doteq (100 \times 1.5) \times (\text{C}_{T} \times 1.2) \quad [\mu\text{F}]$$

#### Note:

If the value of  $C_T$  is decreased to reduce the time setting, it will be impossible to neglect the delay time (approximately 2µs) occurring inside the IC. You should choose an appropriate  $C_T$  value that will involve no influence on delay time.

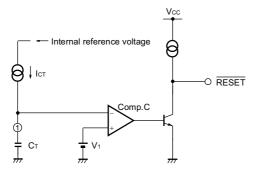

# 2.11 Handling Unused Terminals

How to handle unused terminals in the MB3771 is summarized in Table 2.11-1 .

#### Handling unused terminals

| Terminal name                    | Description     |

|----------------------------------|-----------------|

| C <sub>T</sub> terminal          | OPEN            |

| V <sub>SC</sub> terminal         | GND             |

| OUT <sub>C</sub> terminal        | OPEN            |

| V <sub>SA</sub> / RESIN terminal | V <sub>CC</sub> |

| V <sub>SA</sub> terminal         | OPEN            |

| RESET terminal                   | OPEN            |

Table 2.11-1 Handling unused terminals in the MB3771

# 2.12 Q&A Set Regarding the MB3771

### This section provides a set of questions and answers regarding the MB3771.

### ■ Q&A set regarding the MB3771

|    | Q&A set regarding the MB3771                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |