# LM4830 **Two-Way Audio Amplification System** with Volume Control

# **General Description**

The LM4830 is an integrated solution for two-way audio amplification. It contains a bridge-connected audio power amplifier capable of delivering 1W of continuous average power to an  $8\Omega$  load with less than 1% THD from a 5V power supply. It also has the capability of driving 100 mW into a single-ended 32 $\Omega$  impedance for headset operation. There is a 30 dB attenuator in front of a bridged power amplifier with 6 dB of gain. The attenuation is controlled through 4 bits of parallel digital control; 15 steps of 2 dB each.

The device also contains a microphone preamp with two selectable inputs. Mic1 is selected when HS is high and A1 is in single-ended mode. Mic2 is selected when HS is low and A1 is in bridged mode. This configuration is optimum for switching between an internal system speaker and external headset with microphone. The device also incorporates a buffer used for driving capacitive loads.

The LM4830 also provides a low-current consumption shutdown mode making it optimally suited for low-power portable systems. In addition, the device has an internal thermal shutdown protection mechanism.

## **Key Specifications**

■ THD at 1W cont. avg P<sub>O</sub> into 8Ω

1% (max)

Instantaneous peak output power

1.4W

Shutdown current

0.5 μA (typ)

Supply voltage range

$2.7V \leq V_{DD} \leq 5.5V$

## **Features**

- 4-bit digital control for 30 dB of volume attenuation

- Two selectable microphone inputs

- High performance microphone preamp

- Extra buffer for driving long cables

- No bootstrap capacitors or snubber circuits are necessary

- Small Outline (SO) packaging

- Thermal shutdown protection circuitry

# **Applications**

- Hands-free systems

- Mobile phone accessories

- Desktop conference phones

- Portable computers

- Teleconference computer applications

# Typical Application

# LM4830 R1 40k TL/H/12677-1

**FIGURE 1. Typical Application Circuit**

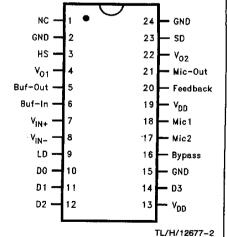

Connection Diagram

#### **Dual-In-Line and Small Outline Packages**

**Top View** Order Number LM4830M See NS Package Number M24B for SO

**Order Number LM4830N** See NS Package Number N24A for DIP

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage 6.0V

Storage Temperature -65°C to +150°C

Input Voltage -0.3V to V<sub>DD</sub> + 0.3V

Power Dissipation (Note 3) Internally Limited

ESD Susceptibility (Note 4) 2000V

ESD Susceptibility (Note 5) 250V

ESD Susceptibility (Note 5)

Junction Temperature

Soldering Information

Small Outline Package Vapor Phase (60 sec.) Infrared (15 sec.) See AN-450 "Surface Mounting and their Effects on Product Reliability" for other methods of soldering surface mount devices.

# **Operating Ratings**

Temperature Range

$\begin{array}{lll} T_{MIN} \leq T_{A} \leq T_{MAX} & -40^{\circ}\text{C} \leq T_{A} \leq 85^{\circ}\text{C} \\ \text{Supply Voltage} & 2.7\text{V} \leq \text{V}_{DD} \leq 5.5\text{V} \\ \theta_{JC} \text{ (typ)} & 32^{\circ}\text{C/W} \\ \theta_{JA} \text{ (typ)} & 79^{\circ}\text{C/W} \\ \theta_{JC} \text{ (typ)} & 24\text{A} \\ \theta_{JA} \text{ (typ)} & 61^{\circ}\text{C/W} \\ \end{array}$

## **Electrical Characteristics** (Notes 1, 2)

The following specifications apply for  $V_{DD} = 5V$ , unless otherwise specified. Limits apply for  $T_A = 25$ °C.

150°C

215°C

220°C

| Symbol          | Parameter                      | Conditions                                                                                                                                                                             | LM4830              |                   |                      |

|-----------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|----------------------|

|                 |                                |                                                                                                                                                                                        | Typical<br>(Note 6) | Limit<br>(Note 7) | Units<br>(Limits)    |

| OWER AN         | IPLIFIER, A1                   |                                                                                                                                                                                        |                     |                   |                      |

| I <sub>DD</sub> | Quiescent Power Supply Current | $V_O = 0V$ , $I_O = 0A$ , $R_L = \infty$                                                                                                                                               | 11.0                | 5.8<br>20.0       | mA (min)<br>mA (max) |

|                 |                                | Bridged $R_L = 8\Omega$<br>HS = 5V, SD = 0V, $V_{O1}$ On Only                                                                                                                          | 11.4<br>7.9         |                   | mA<br>mA             |

| I <sub>SD</sub> | Shutdown Current               | HS = 5V, SD = 5V, IC Off                                                                                                                                                               | 0.5                 | 2.0               | μΑ (max)             |

| Vos             | Output Offset Voltage          | $V_{IN} = 0V$                                                                                                                                                                          | 0.7                 | 50.0              | mV (max)             |

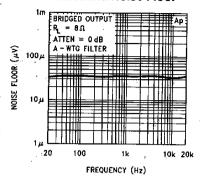

| elN             | Input Noise                    | IHF-A Weighting Filter, $R_S=25\Omega$<br>Bridged Output, $V_{O1}-V_{O2}$ , $R_L=8\Omega$<br>Single-Ended Output, $V_{O1}$ , $R_L=32\Omega$                                            | 30<br>16            |                   | μV<br>μV             |

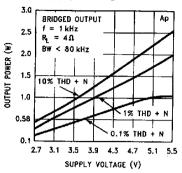

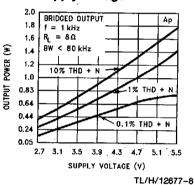

| Po              | Output Power, Bridged          | THD = 1% (max); f = 1 kHz<br>THD + N = 10%; f = 1 kHz, $R_L = 8\Omega$<br>THD + N = 10%; f = 1 kHz, $R_L = 4\Omega$                                                                    | 1.15<br>1.4<br>2    | 1.0               | W (min)<br>W<br>W    |

| THD             | Total Harmonic Distortion      | $ f = 1 \text{ kHz, Attenuation @ 0 dB} $ $ P_O = 1.5 \text{W, R}_L = 4 \Omega $ $ P_O = 1 \text{W, R}_L = 8 \Omega $ $ V_{O1} \text{ On Only, V}_O = 60 \text{ mV, R}_L = 32 \Omega $ | 0.2<br>0.2<br>0.06  |                   | %<br>%<br>%          |

|                 | Attenuation Step Size Error    | 0 dB to -30 dB                                                                                                                                                                         | ±0.5                |                   | dB                   |

|                 | Absolute Attenuation           | Attenuation @ 0 dB<br>Attenuation @ -30 dB                                                                                                                                             | ±0.5<br>±1.0        |                   | dB<br>dB             |

| R <sub>IN</sub> | Power Amp Input Resistance     |                                                                                                                                                                                        | 40                  |                   | kΩ                   |

| IGITAL IN       | PUTS                           |                                                                                                                                                                                        |                     |                   |                      |

| V <sub>IH</sub> | High Input Voltage             | CMOS Compatible Only                                                                                                                                                                   |                     | 4.5               | ٧                    |

| V <sub>IL</sub> | Low Input Voltage              | CMOS Compatible Only                                                                                                                                                                   |                     | 0.5               | V                    |

**Electrical Characteristics** (Notes 1, 2) The following specifications apply for  $V_{DD}=5V$ , unless otherwise specified. Limits apply for  $T_A=25^{\circ}C$  (Continued)

| Symbol          | Parameter                      |                                                                                                                               | LM4830           |                   | Unito             |

|-----------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-------------------|

|                 |                                | Conditions                                                                                                                    | Typical (Note 6) | Limit<br>(Note 7) | Units<br>(Limits) |

| PREAMP          | , A2                           |                                                                                                                               |                  |                   |                   |

| R <sub>IN</sub> | Mic1 and Mic2 Input Resistance |                                                                                                                               | 21.5             |                   | kΩ                |

| Vos             | Output Offset Voltage          | $V_{IN} = 0V$                                                                                                                 | 2.0              |                   | mV                |

| eIN             | Input Noise                    | IHF-A Weighting Filter, $R_S = 25\Omega$                                                                                      | 1.3              | 10.0              | بر (max)          |

| THD             | Total Harmonic Distortion      | $A_{VCL}=100,V_{IN}=10\text{mVrms},f=1\text{kHz}$ $A_{VCL}=-1,P_O=50\text{mW},f=1\text{kHz},R_L=32\Omega$ (Refer to Figure 2) | 0.06<br>0.02     |                   | %                 |

| Xtalk           | Crosstalk                      | $A_{VCL}=$ 100, Power Amp: $P_{O}=$ 1W, $R_{L}=8\Omega$ , f = 1 kHz                                                           | -72              |                   | dB                |

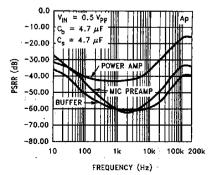

| PSRR            | Power Supply Rejection Ratio   | $V_{DDAC} = 0.5 V_{PP}, f = 1 kHz$                                                                                            | 60               |                   | dВ                |

| MICROPI         | HONE BUFFER, A3                |                                                                                                                               |                  |                   |                   |

| RIN             | Buffer Input Resistance        |                                                                                                                               | 17               |                   | kΩ                |

| Vos             | Output Offset Voltage          | $V_{IN} = 0V$                                                                                                                 | 2.0              |                   | m∨                |

| e <sub>IN</sub> | Input Noise                    | IHF-A Weighting Filter, $R_S=25\Omega$                                                                                        | 5.8              |                   | μV                |

| THD             | Total Harmonic Distortion      | $P_O = 50$ mW, $f = 1$ kHz, $R_L = 32\Omega$                                                                                  | 0.5              |                   | %                 |

| Xtalk           | Crosstalk                      | Power Amp: $P_0 = 1W$ , $R_L = 8\Omega$ , $f = 1 \text{ kHz}$                                                                 | -76              |                   | dB                |

Note 1: All voltages are measured with respect to the ground pins (Pins 2, 15, and 24), unless otherwise specified.

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

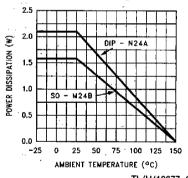

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub> - T<sub>A</sub>)/θ<sub>JA</sub> or the number given in the Absolute Maximum Ratings, whichever is lower. For the LM4830M, T<sub>JMAX</sub> = +150°C, and the typical junction-to-ambient thermal resistance, when board mounted, is 79°C/W.

Note 4: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 5: Machine model, 200 pF-240 pF discharged through all pins.

Note 6: Typicals are measured at 25°C and represent the parametric norm.

Note 7: Limits are guarantees that all parts are tested in production to meet the stated values.

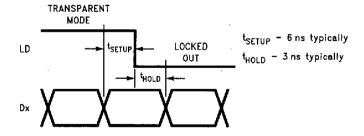

# **Timing Diagram**

TL/H/12677-3

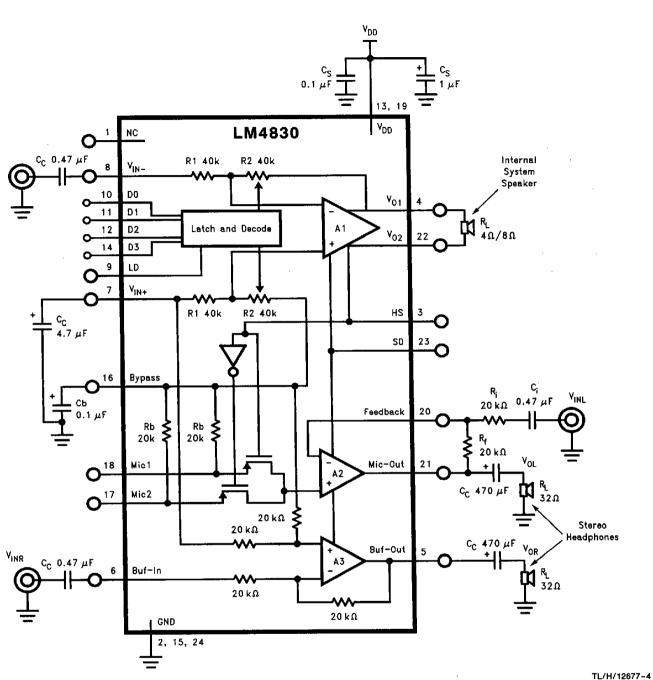

**Computer Application Circuit**

FIGURE 2

5-21

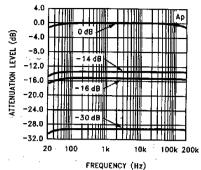

# Typical Performance Characteristics (Power Amp-Bridged)

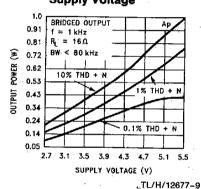

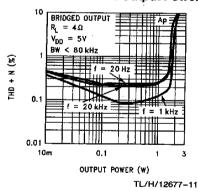

#### Output Power vs Supply Voltage

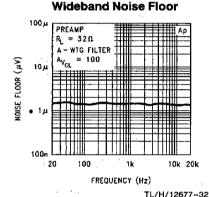

#### Wideband Noise Floor

Frequency Response vs Attenuation Level

TL/H/12677-7

#### Output Power vs Supply Voltage

TL/H/12677-5

Output Power vs Supply Voltage

TL/H/12677--6

Output Power vs Supply Voltage

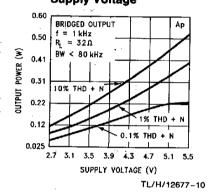

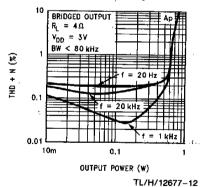

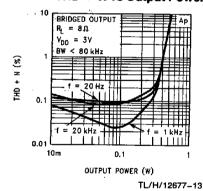

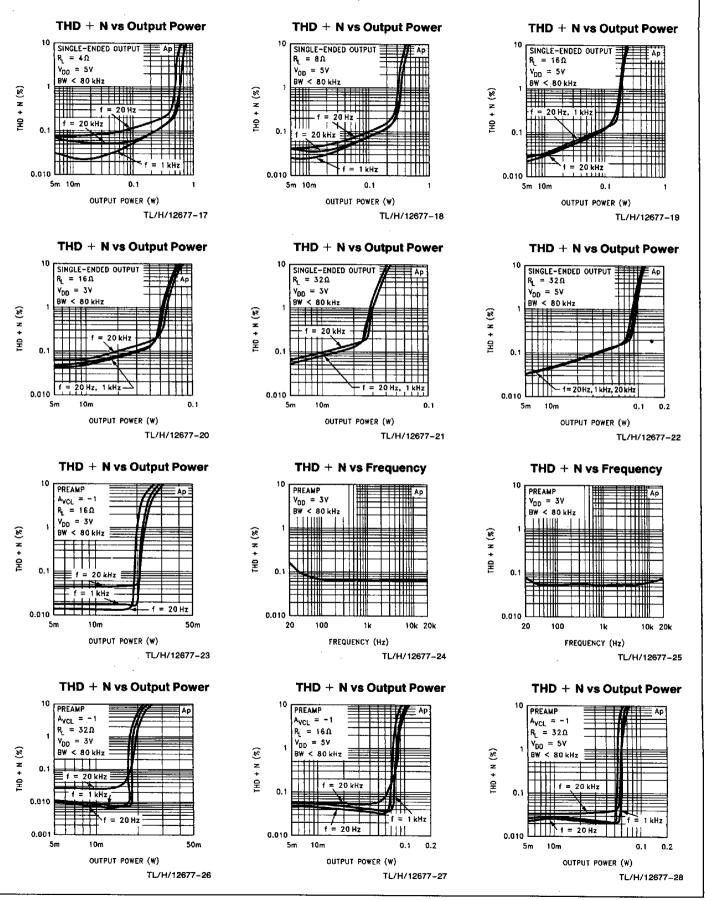

#### THD + N vs Output Power

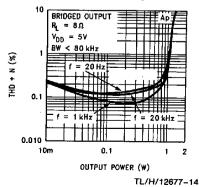

THD + N vs Output Power

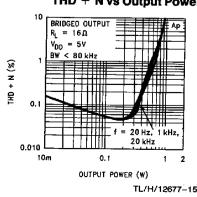

THD + N vs Output Power

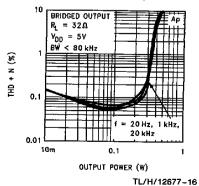

THD + N vs Output Power

THD + N vs Output Power

THD + N vs Output Power

# **Typical Performance Characteristics (Continued)**

# **Typical Performance Characteristics (Continued)**

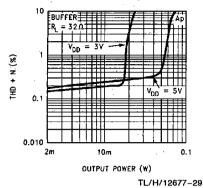

#### THD + N vs Output Power

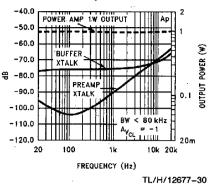

# Power Amp Crosstalk to Preamp and Buffer

# Power Amp Crosstalk to Preamp

TL/H/12677-31

#### ....

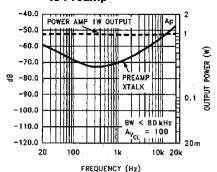

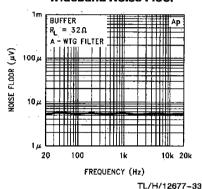

#### **Wideband Noise Floor**

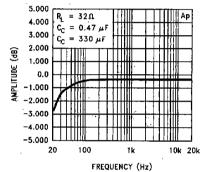

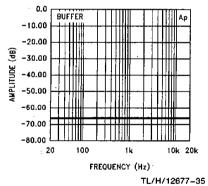

**Buffer** Frequency Response

TL/H/12677-34

# Output Attenuation in Shutdown Mode

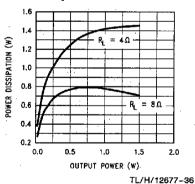

#### Power Dissipation vs Output Power

TL/H/12677-37

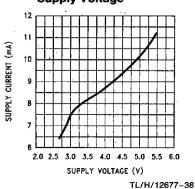

#### Supply Current vs Supply Voltage

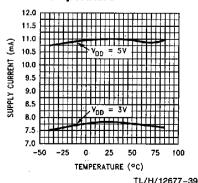

#### Supply Current vs Temperature

Power Supply Rejection Ratio

TL/H/12677-40

## **Application Information**

#### **POWER AMPLIFIER HANDSFREE MODE**

As shown in Figure 1, amplifier A1 can be used in one of two modes, bridged output or single-ended output. This IC was intended to be used in systems requiring both internal speaker drive and external mono-headphone drive capability. Headphones generally have a much higher impedance than that of speakers since headphones don't require as much output power. This also allows headphones to be driven single-endedly. Shown in Figure 1, the output can be automatically switched from bridged speaker drive to singleended headphone drive using a control pin in the headphone jack that is tied to the Headset (HS) pin, pin 3. When the voltage at the HS pin input changes from 0V to 5V, VO2 of the bridged amplifier output is put into high impedance. This allows the permanently connected internal speaker of the system to be disabled when a headphone is plugged into the headphone jack. Output VO1 then drives the headphone single-endedly through the output coupling cap, C<sub>C</sub>. C<sub>C</sub> should be chosen to allow the full audio bandwidth to be amplified. Since CC and RL create a high-pass filter, CC must be big enough to allow frequencies down to 20 Hz to be amplified. The following equation should be used for proper component selection.

$$C_C = 1/(2\pi(20 \text{ Hz})(R_L)) \text{ where } 16\Omega \le R_L \le 600\Omega$$

(1)

As usual, the output drive limitations are the maximum supply voltage swing, current drive capability, and power dissipation. In bridged-output drive mode, the power amplifier will drive  $4\Omega$  or  $8\Omega$  with normal music signals over time. However, trying to put a sinewave through the amplifier at the worst case power dissipation point could cause the amplifier to go into thermal shutdown.

In single-ended drive mode, the amplifier is intended to drive  $32\Omega$  headphones. It will drive lower impedances with the limitations of voltage swing and current drive capability. The result of driving lower impedance loads single-endedly is lower achievable output power.

#### Headset and Shutdown Pin Table

| HS Pin | SD Pin | IC Operation              | Microphone |

|--------|--------|---------------------------|------------|

| Low    | Low    | All Outputs On            | MIC2 On    |

| High   | Low    | 1/2 A1 On                 | MIC1 On    |

|        |        | (V <sub>O1</sub> On Only) |            |

| X      | High   | Whole IC Off              | NA         |

X---"Don't Care" NA-Not Applicable

#### **POWER DISSIPATION**

Power dissipation is a major concern when using any power amplifier and must be thoroughly understood to ensure a successful design. Equation 2 states the maximum power dissipation point for a bridged amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX} = 4(V_{DD})^2/(2\pi^2 R_L)$$

(2)

Although the LM4830 has three amplifiers in the package, the bridged amplifier produces the majority of the power dissipation because it supplies the largest amount of output

power. If each of the amplifiers in the LM4830 were of the same power level, each of their power dissipations would need to be taken into account. However, this is not the case and the bridged power amplifier is the only major power dissipation contributor.

Even with the large internal power dissipation created by the bridged amplifier, the LM4830 does not require heatsinking over a large range of ambient temperatures. Using Equation 2, assuming a 5V power supply and a  $8\Omega$  load, the maximum power dissipation point is 633 mW.

$$P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$$

(3)

For the LM4830 surface mount package,  $\theta_{JA} = 79^{\circ}C/W$ and T<sub>JMAX</sub> = 150°C. Depending on the ambient temperature, TA, of the system surroundings, Equation 3 can be used to find the maximum internal power dissipation supported by the IC packaging. If the result of Equation 2 is greater than that of Equation 3, then either the supply voltage must be decreased, the load impedance increased, or the ambient temperature reduced. For the typical application of a 5V power supply, with a bridged  $8\Omega$  load, the maximum ambient temperature possible without violating the maximum junction temperature is approximately 100°C provided that device operation is around the maximum power dissipation point. The average power dissipation caused by typical music material played at a reasonable level is generally lower than the maximum power dissipation point. Refer to the Typical Performance Characteristics curves for power dissipation information for lower output powers.

#### **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. The capacitor location on both the half-supply bypass and power supply pins should be as close to the device as possible. The effect of a larger half-supply bypass capacitor is improved low frequency PSRR due to increased half-supply stability. Typical applications employ a 5V regulator with 10  $\mu\text{F}$  and a 0.1  $\mu\text{F}$  bypass capacitors which aid in supply stability, but do not eliminate the need for bypassing the supply nodes of the LM4830. The selection of bypass capacitors, especially  $C_{b}$ , is thus dependent upon desired low frequency PSRR, system cost, and size constraints.

#### **GROUNDING**

In order to achieve the best possible performance, there are certain grounding techniques that should be followed. All input reference grounds should be tied with their respective source grounds and brought back to the power supply ground separately from the output load ground returns. Those input grounds should also be tied in with the half-supply bypass ground, pin 16. As an example, the AC input ground reference for the power amplifier, A1, is  $\rm V_{IN+}$ , pin 7. This ground should be tied as close as possible to the Bypass ground (pin 16), as shown in Figure 1. In order to tie in the signal source ground, the audio jack ground on  $\rm V_{IN-}$  should also be tied to the Bypass ground.

## **Application Information (Continued)**

As stated above, the ground returns for the output loads should be brought back to the supply ground individually. This will keep large signal currents on those ground lines from interfering with the stable AC input ground references. In addition, the signal ground reference for the preamp, A2, (the ground end of capacitor C<sub>I</sub>) should be tied together with the mic inputs' signal ground reference from the microphone.

#### **LAYOUT ISSUES**

As stated in the Grounding section, placement of ground return lines is imperative in maintaining the highest level of system performance. It is not only important to route the correct ground return lines together, but also equally important to be aware of where those ground return lines are routed in conjunction with each other. As an example, the output load ground return lines should not be tied together with AC input reference ground return lines. In addition, the layout of these ground lines should be physically located as far as reasonably possible from each other so that large signal coupling cannot occur. To further exemplify this point, the outputs and output load returns for the power amplifier, which have volts of signal on them, should be physically isolated from the sensitive inputs and AC input ground returns associated with the preamp. It is easy for large signals to couple into the sensitive low voltage microphone preamp inputs.

**TABLE I. 4-Bit Attenuation Control**

| LD<br>Pin | Input Bits<br>msb Isb<br>D3-D0 | Attenuation<br>Level (dB) | Bridge<br>Amplifier<br>Gain (dB) |

|-----------|--------------------------------|---------------------------|----------------------------------|

| 1         | . 0000                         | 0 dB                      | 6 dB                             |

| 1 1       | 0001                           | - 2 dB -                  | 4 dB                             |

| 1 .       | 0010                           | −4 dB                     | 2 dB                             |

| 1         | 0011                           | −6 dB <sup>**</sup>       | 0 dB                             |

| 1 1       | 0100                           | −8 dB                     | −2 dB                            |

| 1         | 0101                           | −10 dB                    | -4 dB                            |

| 1         | 0110                           | −12 dB                    | −6 dB                            |

| : 1       | 0111                           | −14 dB                    | −8 dB                            |

| 1         | 1000                           | -16 dB                    | -10 dB                           |

| 1         | 1001                           | −18 dB                    | -12 dB                           |

| ] 1       | 1010                           | −20 dB                    | 14 dB                            |

| 1         | 1011                           | -22 dB                    | -16 dB                           |

| 1         | 1100                           | -24 dB                    | - 18 dB                          |

| 1         | 1101                           | −26 dB                    | −20 dB                           |

| 1         | 1110                           | −28 dB                    | ·· −22 dB                        |

| : 1.      | - 1111                         | −30 dB                    | 24 dB                            |

| 0         | XXXX                           | NC                        | -NC                              |

#### Key:

0-Logic Low (0V)

1-Logic High (5V)

X-Don't Care

NC-No Change

#### DIGITAL ATTENUATION CONTROL

The Load (LD) pin, pin 9, has two modes of operation. When this input pin is a logic high, 5V, the power amp's attenuation control is in "transparent mode" where the voltages on bits D0-D3 will cause the appropriate attenuation level to be latched and decoded within the IC. For normal attenuation, pin 9 should be at 5V. When the LD input pin is a logic low, 0V, the power amp's attenuation control is "locked-out" so that any change in the input bits will not cause a subsequent change in the amp's attenuation level.

The attenuation level is preset to -16 dB when the IC is first powered up, assuming that LD is a logic low until the IC is fully biased up.

To provide the best click and pop performance when changing attenuation levels, each step should be utilized. If a mute-type function is desired, it is recommended that each of the attenuation steps be "ramped through" quicker than the normal attenuation ramp.

To ensure that attenuation steps are flawless when data is transitioning with load, refer to the timing diagram for proper setup and hold times.

#### **SELECTION OF EXTERNAL CAPACITORS**

The IC's low frequency power supply rejection can be improved by using a larger bypass capacitor,  $C_{b}.$  By increasing this capacitor value, the THD performance at low frequencies will also be improved. For cost sensitive designs, 0.1  $\mu\text{F}$  is recommended, however, for best performance at least 1  $\mu\text{F}$  should be used.

The selection of the microphone input coupling capacitors should be based on desired low frequency coupling. Since the input resistance for those inputs is around 20 k $\Omega$ , the coupling cap should be 0.47  $\mu F$  for 17 Hz coupling or 0.047  $\mu F$  for 170 Hz coupling.

Similarly, the selection of the power amplifier input coupling capacitors should be based on an input resistance of 40 k $\Omega$ , so for flatband 20 Hz reproduction, 0.47  $\mu$ F caps or larger should be used.

#### **VOICE-BAND DESIGN**

The preamp on this IC is intended to be used for microphone amplification. Depending upon the frequency response of the microphone, the preamplifier's response can be configured to fit the microphone. Simple capacitors can be used to bandwidth limit the frequency response of the preamplifier and improve the system's performance. Once the gain of the preamp is chosen, the values for the resistors and capacitors can be selected based upon desired cutoff frequencies using the equations below.

$$A_{VCL} = 1 + R_f/R_i \qquad (4)$$

$$flp = 1/(2\pi R_f C_f)$$

(5)

$$fhp = 1/(2\pi R_i C_i)$$

(6)

As an example, lets assume that the desired closed-loop gain is 40 dB and the desired voice-band is 300 Hz to 3 kHz. Using Equation 4, we choose  $R_f=100~k\Omega$  and  $R_i=1~k\Omega$ . The desired value in dB is equal to 20 log (A<sub>VCI</sub>). Then,

### Application Information (Continued)

solving for  $C_f$  and  $C_i$  using flp = 3 kHz, fhp = 300 Hz,  $R_f$  = 100  $k\Omega$ , and  $R_i$  = 1  $k\Omega$  we get the following:  $C_f$  = 530 pF and  $C_i$  = 0.53  $\mu F$ .

#### **COMPUTER APPLICATION CIRCUIT**

The LM4830 can also be used to drive both an internal system speaker and stereo headphones simultaneously, as shown in *Figure 2*. The internally configured unity-gain buffer requires the preamp to also be set up in an inverting unity-gain fashion to maintain proper signal phase between channels for the stereo headphone amplifier. The unity-gain configured circuit also requires that the AC input signal dynamic range be properly conditioned for the 2.5 V<sub>PK</sub> signal swing.

Please refer to the **Typical Performance Characteristics** curves for THD+N vs  $P_O$  and frequency of the MIC preamp and buffer.

#### SHUTDOWN FUNCTION

In order to reduce current consumption while not in use, the LM4830 contains a shutdown pin to externally turn off the IC's bias circuitry. This shutdown feature turns the IC off when a logic high is placed on the shutdown pin. The trigger

point between a logic low and logic high is typically half-supply. Quiescent current consumption will depend upon the value of this voltage. It is best for this voltage to be forced to  $V_{DD}$  to obtain the guaranteed shutdown current. The shutdown feature reduces quiescent supply current consumption from a typical 11 mA to under 2  $\mu$ A for the whole IC. This feature is especially useful when the IC is used in portable battery operated systems where energy conservation is imperative.

In many applications, a microcontroller or microprocessor output interfaces to the LM4830 shutdown pin, providing a quick, smooth transition into shutdown. Another solution is to use a single-pole, single-throw switch in conjunction with an external pull-up resistor. When the switch is closed, the shutdown pin is connected to ground and enables the amplifier. If the switch is open, the external pull-up resistor disables the LM4830 by bringing the shutdown pin up to  $V_{DD}$ . This scheme guarantees that the shutdown pin will not float, preventing unwanted state changes.

Additionally, when the IC comes out of shutdown the IC's volume attenuation setting will remain unchanged.