### **Preliminary Data Sheet**

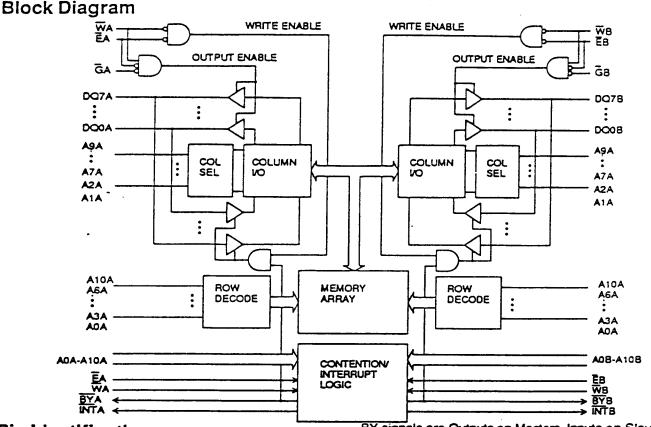

#### **Functional Description**

The LH5911, LH5912 and LH5914 are dual port static RAMs that use true dual port memory cells to allow each port to independently access any location in memory. The LH5911 and LH5912 are "Master" devices which may be used alone in a single width configuration, or with one or more LH5914 "Slave" devices in wide word applications.

Each port provides a conventional byte wide interface to the system. Chip Enable  $(\overline{E})$ , Write Enable  $(\overline{W})$ , and Output Enable  $(\overline{G})$  inputs independently control the function of each port. Additionally, Busy  $(\overline{BY})$  and Interrupt  $(\overline{INT})$  flags provide communication between the ports. An asserted  $\overline{BY}$  output indicates that the internal arbitration logic has granted the opposite port access to the desired address. An asserted  $\overline{INT}$  flag indicates the opposite port has requested attention by writing to a specific location.  $\overline{BY}$  and  $\overline{INT}$  are open drain outputs, allowing for wire or-ing of either function.  $\overline{BY}$  is an output on Master type devices and an input on Slave type devices.

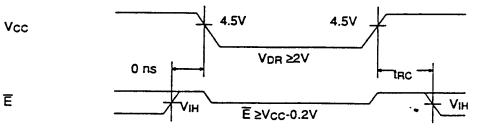

Power reduction circuitry has been designed into each port, controlled by  $\overline{E}$ . Battery backup is possible with data retention at voltages down to 2.0V in the Data Retention mode.

## LH5911/LH5912/LH5914 2K x 8 CMOS Dual Port RAM

#### Features

- Fast Access Times 35/45/55 ns

- True Dual Port Memory Array

- Fully Asynchronous

- LH5911: Master

- LH5912: Master with INT LH5914: Slave

- Busy Output on Master Busy Input on Slave

- Data Retention Mode for Battery

Backup

- 48-Pin DIP, 52-Pin DIP or 52-Pin PLCC

- INT Flag for Inter Port Communication (LH5912 Only)

- E Power Down

- "Transparent" Write

- TTL Compatible I/O

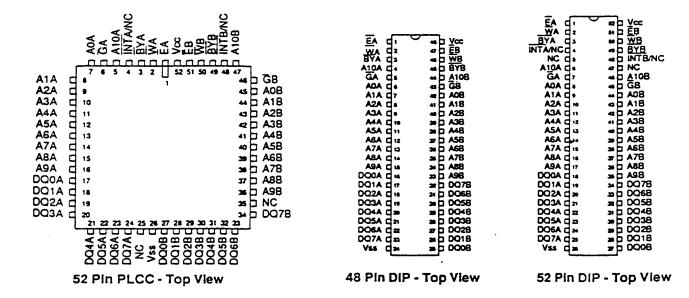

#### **Pinout Diagrams**

## LH5911/LH5912/LH5914

#### **Pin Identification**

BY signals are Outputs on Masters, Inputs on Slaves

| A0-A10   |    |   |   |   |   |   |   |   |      |      |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |   |   |   |   |   |   | _ |   |   |   | Address Inputs       |

|----------|----|---|---|---|---|---|---|---|------|------|---|---|---|---|---|---|---|---|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----------------------|

| DQo-D    | 07 | 1 |   |   |   |   |   |   | <br> | <br> |   |   |   |   |   |   |   |   |    |   | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   | Data inputs/Outputs  |

| <u>E</u> |    |   |   | • | • | • |   |   |      | <br> |   | - |   | • | • |   | • | • | ۰. |   |   |   |   | • |   |   | • |   |   |   | • | • |   |   |   | . Chip Enable Input  |

| <u>w</u> |    | ٠ | • | • |   | • |   |   | <br> | <br> |   |   | • | • |   | • | • | • |    |   | • | • | • |   | • |   | • |   |   | • |   |   | • |   |   | Write Enable Input   |

| <u> </u> |    | • |   | • | • | • | • |   |      | <br> | • |   | • | • | • | • | • | • | •  |   | • | • | • |   |   |   |   |   |   | • | • |   |   |   | • | Output Enable Input  |

|          |    |   |   |   |   |   |   |   |      |      |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | Busy Output (Input)  |

| INT/NC   | ;  | • | • | • | • | ٠ | • |   |      | <br> | • |   | • | • |   | • |   |   | •  | • | • | • |   | • |   | • | • | • |   |   |   | • | • |   |   | Interrupt Output     |

|          |    |   |   |   |   |   |   |   |      |      |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | ositive Power Supply |

|          | •  | • | • |   | • | • | • | • |      | <br> | • | - | • |   | • | • | • | • | •  |   | • | • | • | • | • |   | • | • | • | • |   |   | • | • |   | Ground               |

| Notes:   |    |   |   |   |   |   |   |   |      |      |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                      |

Functions apply equally to Port A and Port B

Vcc and Vss are common to both ports.

$\overrightarrow{BY}$  A and  $\overrightarrow{BY}$  B are outputs on LH5911 and LH5912.  $\overrightarrow{BY}$  A and  $\overrightarrow{BY}$  B are inputs on LH5914. INT A/NC and  $\overrightarrow{INT}$  B/NC are  $\overrightarrow{INT}$  A and  $\overrightarrow{INT}$  B on LH5912, and NC on LH5914

### **Configuration** Table

| Part Number | Package | # of Pins | BY                | ÎNT/NC            | Туре   |

|-------------|---------|-----------|-------------------|-------------------|--------|

| LH5911      | DIP     | 48        | Output            | N/A               | Master |

| LH5912      | DIP     | 52        | Open Drain Output | Open Drain Output | Master |

| LH5912      | PLCC    | 52        | Open Drain Output | N/A               | Master |

| LH5914      | DIP     | 48        | Input             | NC                | Slave  |

| LH5914      | PLCC    | 52        | Input             | N/A               | Slave  |

Preliminary Data Sheet

SHARP

Page 2

## Absolute Maximum Ratings<sup>1</sup>

| Supply Voltage to Ground Potential     |

|----------------------------------------|

| Signal Pin Voltage Range               |

| DC Output Current <sup>2</sup> ± 40 mA |

| Storage Temperature Range              |

| Power Dissipation (Package Limit) 1.0W |

## **Operating Range**

| Symbol | Parameter                 | Min  | Max     | Unit |

|--------|---------------------------|------|---------|------|

| TA     | Temperature, Ambient      | 0    | 70      | °C   |

| Vcc    | Supply Voltage            | 4.5  | 5.5     | V    |

| Vss    | Supply Voltage            | 0    | 0       | v    |

| VIL    | Logic "0" Input Voltage 3 | -0.5 | 0.8     | V    |

| ViH    | Logic "1" Input Voltage   | 2.2  | Vcc+0.5 | V    |

## DC Electrical Characteristics - Over Operating Range

| Symbo        | ol Parameter                   | Test Conditions           | Min | Тур | Max | Unit |

|--------------|--------------------------------|---------------------------|-----|-----|-----|------|

| Icc1         | Operating Current <sup>4</sup> |                           |     |     | 150 | mA   |

| IS81         | Standby Current                | Ē A and Ē B ≥VIH          |     |     | 30  | mA   |

| <b>IS8</b> 2 | Standby Current 4              | Ē ▲ or Ē в ≥ViH           | 1   |     | 75  | mA   |

| IS83         | Standby Current                | E A and E B ≥Vcc-0.2V     |     | 1   | 5   | mА   |

| IS84         | Standby Current 4              | Ē A OF Ē B ≥Vcc-0.2V      |     |     | 65  | mA   |

| lu           | Input Leakage Current          | Vcc=5.5V, Vin = 0V to Vcc | 1   | 1   | 2   | μА   |

| ILO          | I/O Leakage Current            | Vcc=5.5V, Vin = 0V to Vcc |     |     | 2   | μA   |

| Vон          | Output High Voltage            | юн = -4.0mA               | 2.4 | 1   | 1   | V    |

| VOL          | Output Low Voltage             | ю <u>ь</u> = 8.0mA        |     |     | 0.4 | ٦V   |

| VOL          | Output Low Voltage 5           | loL = 16.0mA              |     |     | 0.5 | V    |

| VDR          | Data Retention Voltage         | Ē ≥Vcc-0.2V               | 2.0 |     |     | v    |

| IDA          | Data Retention Current         | VDR = 3.0V                | T   |     | 100 | υA   |

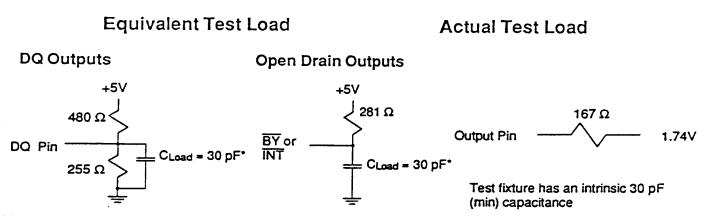

## **AC Test Conditions**

| Input Pulse Levels                  | Vss to 3V          |

|-------------------------------------|--------------------|

| Input Rise and Fall Times           |                    |

| Input and Output Timing Ref. Levels |                    |

| Output Load, Timing Tests           | See Figure, Page 5 |

## Capacitance <sup>6,7</sup>

| CIN (Input Capacitance)                | 7pF |

|----------------------------------------|-----|

| Cpq (Output, Input/Output Capacitance) | 7pF |

See notes following "Switching Characteristics"

## Switching Characteristics - Over Operating Range 8

See Notes on Page 5

٠.

|         | B a sector to a                            | -35 |         | -4  |                                              | -5  |         |      |

|---------|--------------------------------------------|-----|---------|-----|----------------------------------------------|-----|---------|------|

| ymbol   |                                            | Min | Max     | Min | Max                                          | Min | Max     | Unit |

| Read    | Cycle                                      |     |         |     | _                                            |     |         |      |

| tRC     | Read Cycle Timing                          | 35  |         | 45  |                                              | 55  |         | ns   |

| taa     | Address Access Time                        |     | 35      |     | 45                                           |     | 55      | ns   |

| tон     | Output Hold from Address Change            | 3   |         | 3   | T                                            | 3   |         | ns   |

| tea 🛛   | E Low to Valid Data                        |     | 35      | 1   | 45                                           | 1   | 55      | ns   |

| telz    | E Low to Output Active 6.9                 | 5   |         | 5   |                                              | 5   |         | ns   |

| tehz 🛛  | E High to Output High Z 6.9                | 3   | 15      | 3   | 20                                           | 3   | 25      | ns   |

| tgiz"   | G Low to Output Active 6,9,10              | 3   | 15      | 3   | 20                                           | 3   | 25      | กร   |

| lgнz    | G High to Output High Z <sup>6,9</sup>     | 3   | 15      | 3   | 20                                           | 3   | 25      | ns   |

| IPU     | E Low to Power Up Time <sup>6</sup>        | 0   |         | 0   |                                              | 0   |         | ns   |

| IPD     | E High to Power Down Time <sup>6</sup>     |     | 20      |     | 25                                           |     | 30      | ns   |

| Write   | Cycle                                      |     |         |     |                                              |     |         |      |

| twc     | Write Cycle Time                           | 35  |         | 45  |                                              | 55  |         | ns   |

| EW      | E Low to End of Write                      | 30  |         | 35  |                                              | 40  |         | ns   |

| law     | Address Valid to End of Write              | 30  | 1       | 35  |                                              | 40  |         | ns   |

| as      | Address Setup                              | 0   |         | 0   | T                                            | 0   |         | ns   |

| AH      | Address Hold from End of Write             | 0   |         | 0   | 1                                            | 0   |         | ns   |

| WP      | W Pulse Width                              | 30  |         | 35  |                                              | 40  |         | ns   |

| DW      | Input Data Setup Time                      | 15  |         | 20  |                                              | 25  |         | ns   |

| DH      | Input Data Hold Time                       | 0   |         | 0   |                                              | 0   |         | ns   |

| WHZ     | W Low to Output High Z 6,9                 |     | 15      |     | 20                                           |     | 25      | ns   |

| wlz     | W High to Output Active 6.9                | 3   |         | 3   |                                              | 3   |         | ns   |

| Conte   | ntion Timing                               |     |         |     |                                              |     |         |      |

| BL      | Contention Exists to BY Low                | 0   | 20      | 0   | 25                                           | 0   | 30      | ns   |

| вн      | Contention Ends to BY High                 | 0   | 20      | 0   | 25                                           | 0   | 30      | ns   |

| wi      | W High Prior to BY High to Inhibit Write   | 15  |         | 15  |                                              | 15  |         | ns   |

| 000     | Data Flow Through Time (Transparent Write) |     | 40      |     | 45                                           |     | 55      | ns   |

| WDD     | Write LOW to Data Valid (Opposite Port)    |     | 50      |     | 55                                           |     | 65      | ns   |

| APS     | Arbitration Priority Setup Time            | 10  |         | 10  |                                              | 10  |         | ns   |

| WRD     | W Low to Read Data Invalid                 | 5   |         | 5   |                                              | 5   |         | ns   |

| BW      | BY Low to W Low for Slave                  | 0   |         | 0   |                                              | 0   |         | ns   |

| w       | BY High to W High for Valid Write          | 15  |         | 20  |                                              | 25  |         | ns   |

| BDD     | BY High to Valid Data                      |     | Note 11 |     | Note 11                                      |     | Note 11 | ns   |

| Interru | pt Timing                                  | i   |         |     | <u>.                                    </u> |     | <u></u> |      |

| NS      | Write Cycle begin to INT Low               | T   | 25      |     | 30                                           |     | 35      | ns   |

| MNS     | W Low to INT Low                           |     | 25      |     | 30                                           |     | 35      | ns   |

| NR      | Read Cycle Begin to INT High               |     | 25      |     | 30                                           |     | 35      | пѕ   |

| SINR    | G Low to INT High                          |     | 25      |     | 30                                           |     | 35      | ns   |

Preliminary Data Sheet

## 2K x 8 Dual Port RAM

#### Notes:

1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Outputs should not be shorted for more than 30 seconds. No more than one output should be shorted at any time.

3. Negative undershoots of up to 3.0V are permitted once per cycle.

4. Icc and Isa are dependent upon actual output loading and cycle rates. Specified values are with outputs open, operating at specified cycle times.

5. Open Drain outputs only (INT and BY).

6. Sample tested only.

7. Capacitances are maximum values at 25°C measured at 1.0 MHz with Vin=0V and Vcc=5.0V.

8. Switching Characteristics measurements performed at \*AC Test Condition\* levels.

9. Active output to High-Z and High-Z to active output tests specified for a 500mV transition from steady state levels into the test load.  $C_{\rm Load}$  is 5 pF for these tests.

10. touz (max) will result in Valid Data Out given that both tax and tex have been met.

11. topo is determined by the greater of 0, twoo - two(actual) or topo - tow(actual).

Includes scope and jig capacitance.

### **Data Retention Timing**

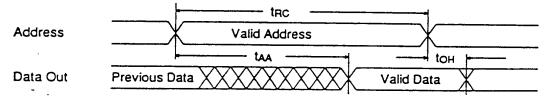

### Switching Waveforms - Read Cycle

#### Read Cycle No. 1 - Either Port

Chip is in Read mode:  $\overline{W}$  is HIGH and  $\overline{E}$  is LOW. Read cycle timing is referenced from when all addresses are stable until the first address transition. Crosshatched portion of I/O implies that data lines are in the Low-Z state and that Data-out may not be valid.

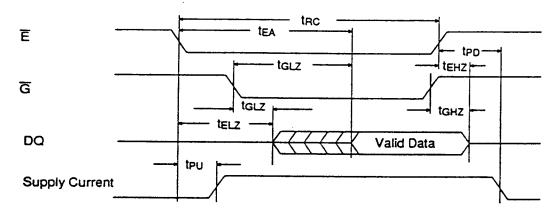

#### Read Cycle No. 2 - Either Port

Chip is in Read mode:  $\overline{W}$  is HIGH. Timing illustrated for the case where addresses are valid before  $\overline{E}$  goes LOW. Data-out is not specified to be valid until the latter of tEA or tGLZ(min), but may become valid as soon as tELZ or tGLZ(max). Outputs will transition from high-Z to valid Data-out.

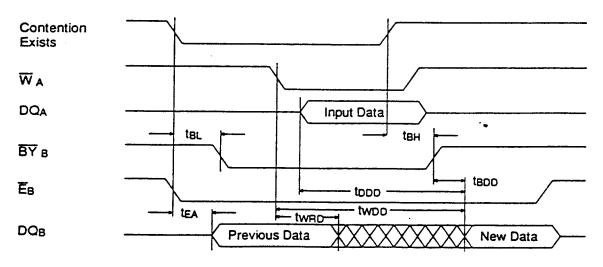

#### Read Cycle No. 3 - Read While BY (Transparent Write)

Contention occurs with Port A winning. Port A performs a Write (which is shown as a delayed Write in this example for illustration purposes). Port B performs a Read. Port B's DQ lines will follow the contents of the memory location, even as Port A changes it. DQs becomes indeterminate twnp after  $\overline{W}$  A goes low. DQs will reflect the new data topp after it is presented to DQA. The new data on DQs will be guaranteed to be valid tgpp after  $\overline{BY}$  B returns HIGH.

#### **Preliminary Data Sheet**

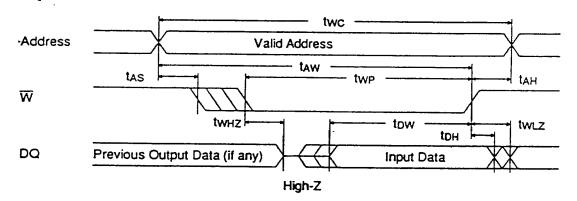

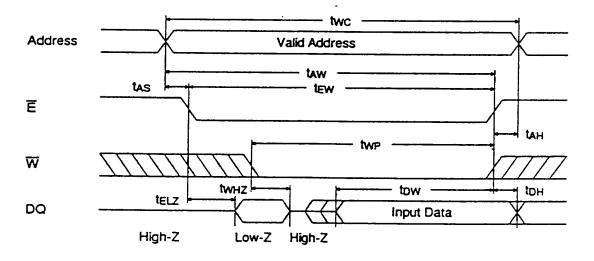

## Switching Waveforms - Write Cycle

Addresses must be stable during Write Cycles. The outputs will remain in the high Z state if  $\overline{W}$  is low when  $\overline{E}$  goes low. If  $\overline{G}$  is high, the outputs will remain in the high Z state. Although these examples illustrate timing with  $\overline{G}$  active, it is recommended that  $\overline{G}$  be held high for all write cycles. This will prevent the outputs from becoming active during write cycles, preventing bus contention, thereby reducing system noise.

#### Write Cycle No. 1 (W Controlled)

Chip is selected:  $\vec{E}$  is low. The data bus may become driven twill after the rising edge of  $\overline{W}$ . Given that the addresses have not changed, the output data will be identical to the data previously written into the same location.

#### Write Cycle No. 2 (E Controlled)

DQ lines may transition to low Z if the falling edge of  $\overline{W}$  occurs after telz from the falling edge of  $\overline{E}$ .

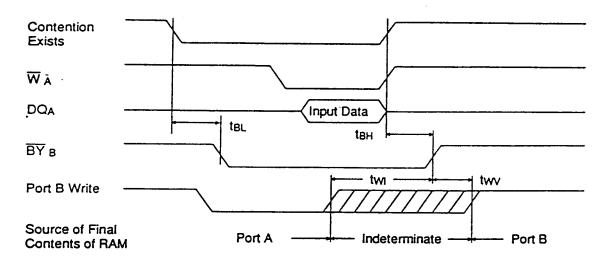

#### Write Cycle No. 3 - Write While Busy

This cycle demonstrates contention occurring with Port A winning. Port A performs a Write. Port B performs a Write. The Write on Port A will occur normally. The Write on Port B will be inhibited while  $\overrightarrow{BY}$  B is LOW. If the Write on Port B is terminated prior to two, it will have been completely inhibited. If the Write on Port B ends later than two after  $\overrightarrow{BY}$  B returns HIGH, the data on DQB will have been written into the location. If the Write on Port B ends after two but before two, the data left in the addressed location may be indeterminate.

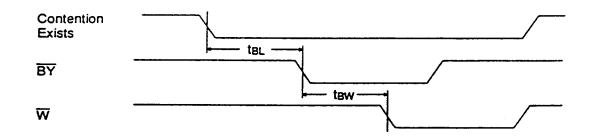

#### Width Expansion - Use of the Slave LH5914

Systems wider than 8 bits will need to use dual port RAMs in parallel. Slave LH5914 chips should be used for word width expansion to prevent the multiple dual port RAMs from resolving contention situations in favor of different ports. Systems which have the potential for contention to exist should use LH5912 52-pin Masters with BY outputs instead of LH5911 48pin Standalone devices, which do not have BY outputs.

Slave device's  $\overline{BY}$  pins are Inputs. Systems should connect the Master's  $\overline{BY}$  open drain outputs to every Slave's  $\overline{BY}$  inputs, with a pull up resistor to Vcc.

Slaves depend upon the Master to determine which port should be the winner in the event of contention. Read cycle timing is not effected, however special considerations must be made in Write cycle timing. To assure that the Slave has sufficient time to inhibit Write cycles on the losing port, the falling edge of  $\overline{W}$  must occur at least tew after  $\overline{BY}$  for that port goes low. Delaying the falling edge of  $\overline{W}$  by teL+tew from the falling edge of  $\overline{E}$  will meet this constraint.

The same constraints apply with respect to properly ending Write cycles in Slaves as it does in Masters. Refer to the next section.

#### **Contention** Operation

Contention occurs when both ports attempt to address the same location at the same time. Proper system operation can be insured if each port's Busy output is used to generate wait states, stretching the cycle for the duration of the Busy condition.

In these examples, assume that Port A arrives first, so  $\overline{BY}$  B is asserted. All cycles on Port A will occur normally. Read cycles on Port B will occur normally, but Write cycles on Port B will be inhibited until its  $\overline{BY}$  flag returns HIGH.

Port A Read; Port B Read. Reads to the same location will yield valid data on both ports.

Port A Write; Port B Read. The Write cycle on Port A will be successfully completed. The Read on Port B will follow the changing contents of the RAM location. Read Cycle 3 illustrates this operation. The assertion of  $\overline{BY}$  g during Port B's Read cycle signals that the data may be changing, and that Port B must wait for tgoo for that data to be assured of being valid. Port A Write; Port B Write. The winning port will successfully complete its Write, however the final contents of the location will depend upon the timing of the losing port. Port B's Write will be inhibited for the duration of the contention. If Port B's Write ends prior to two of the rising edge of  $\overline{BY}_B$ , Port B's write will have been inhibited and Port A's data will remain in the RAM. If Port B extends its Write past two after the rising edge of  $\overline{BY}_B$ , Port B's Write will be complete, and Port B's data will be left in the RAM. If Port B's data will be left in the RAM. If Port B's data will be left in the RAM. If Port B's data will be left at the addressed byte.

Port A Read; Port B Write. The Read on Port A will inhibit the Write on Port B for the duration of the contention. The outcome of the inhibited Write on Port B will be determined in the same way as the case of "Port A Write; Port B Write", described above.

#### Switching Waveforms - Contention

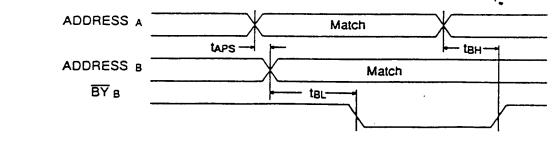

#### Addresses Match; E Arbitration

Both port's addresses match prior to  $\vec{E}$  being asserted. If the falling edges of the  $\vec{E}$ s are within taps, the contention logic will determine which port's  $\vec{BY}$  flag is asserted.

#### Both Ports Enabled; Address Arbitration

Both ports are enabled prior to the addresses matching. If the addresses are valid within tAPS, the contention logic will determine which port's  $\overline{BY}$  flag is asserted.

## LH5911/LH5912/LH5914

## 2K x 8 Dual Port RAM

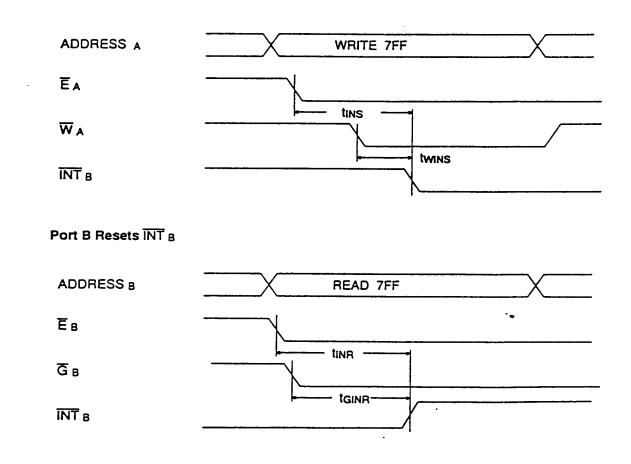

#### Interrupt Operation - LH5912

LH5912s are 52 pin Masters that provide an interport communication scheme through the use of interrupt latches. Each port is assigned a unique "mailbox" within the memory address space. When a port writes to its own mailbox, the opposite port's latch is set, and its INT output goes LOW.

When Port A wants to send Port B a message, Port A writes to its own mailbox at memory location 7FF (A0-A10 = HIGH). This will cause  $\overline{INT}$  B to be set. Port B can then reset that interrupt by reading Port A's mailbox at location 7FF.  $\overline{G}$  B must be active during Port B's Read cycle for  $\overline{INT}$  B to be reset.

Port B's mailbox is at memory location 7FE (A0 = LOW, A1-A10 = HIGH). Port B sends a mes-

sage to Port A by writing to its own mailbox, which sets  $\overline{INT}_A$ . Port A resets  $\overline{INT}_A$  by reading Port B's mailbox.  $\overline{G}_A$  must be active during Port A's Read cycle for  $\overline{INT}_A$  to be reset.

The mailboxes are normal memory locations. Contention effects Read and Write operations to the mailbox locations in the same way it effects any other memory address.

The INT outputs are active LOW open drain outputs. They should be pulled up to Vcc with a resistor, and may be wire ORed together. Systems not using the INT functions may leave the INT pins open. The INT latches should be reset upon power-up to assure they were not set during power-up.

### Switching Waveforms - Interrupt

SHARP

#### Port A Sets INT<sub>B</sub>

Preliminary Data Sheet

## 2K x 8 Dual Port RAM

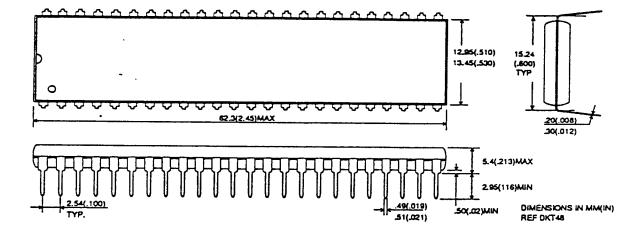

## Package Diagram - 48-Pin Plastic DIP

## LH5911/LH5912/LH5914

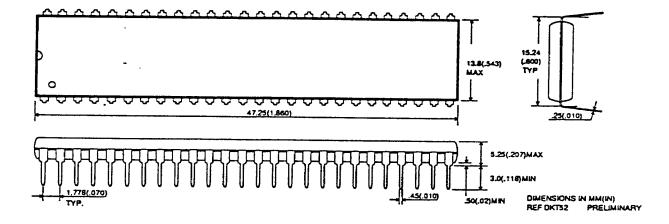

## Package Diagram - 52-Pin Plastic DIP

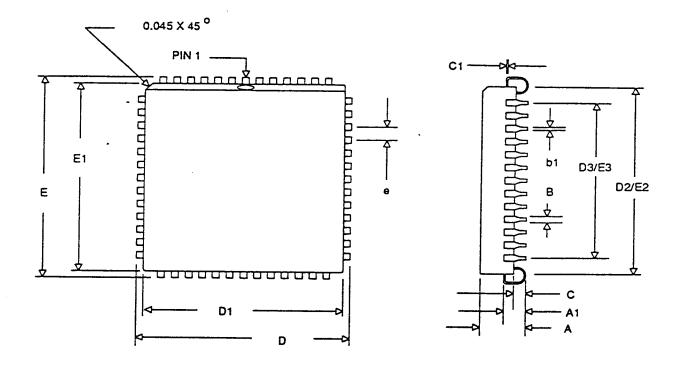

Package Diagram - 52-Pin PLCC

|        | inc   | hes   | millin | neters |

|--------|-------|-------|--------|--------|

| Symbol | Min   | Max   | Min    | Max    |

| A      | 0.165 | 0.180 | 4.19   | 4.57   |

| A1     | 0.090 | 0.120 | 2.29   | 3.05   |

| 8      | 0.026 | 0.032 | 0.66   | 0.82   |

| b1     | 0.013 | 0.021 | 0.33   | 0.53   |

| C      | 0.020 | 0.040 | 0.51   | 1.02   |

| C1     | 0.008 | 0.012 | 0.20   | 0.30   |

| D      | 0.785 | 0.795 | 19.94  | 20.19  |

| D1     | 0.750 | 0.756 | 19.05  | 19.20  |

| D2/E2  | 0.690 | 0.756 | 17.53  | 19.20  |

| D3/E3  | 0.600 | REF   | 15.24  | REF    |

| E      | 0.785 | 0.795 | 19.94  | 20.19  |

| E1     | 0.750 | 0.756 | 19.05  | 19.20  |

| 0      | 0.050 | BSC   | 1.27   | BSC    |

## Ordering Information

| Ordering Code | Туре   | Speed | # Pins | Package Type        |

|---------------|--------|-------|--------|---------------------|

| LH5911-35     | Master | 35ns  | 48     | 600-Mil Plastic DIP |

| LH5911-45     | Master | 45ns  | 48     | 600-Mil Plastic DIP |

| LH5911-55     | Master | 55ns  | 48     | 600-Mil Plastic DIP |

| LH5912-35     | Master | 35ns  | 52     | 600-Mil Plastic DIP |

| LH5912-45     | Master | 45ns  | 52     | 600-Mil Plastic DIP |

| LH5912-55     | Master | 55ns  | 52     | 600-Mil Plastic DIP |

| LH5912U-35    | Master | 35ns  | 52     | PLCC                |

| LH5912U-45    | Master | 45ns  | 52     | PLCC                |

| LH5912U-55    | Master | 55ns  | 52     | PLCC                |

| LH5914-35     | Slave  | 35ns  | 48     | 600-Mil Plastic DIP |

| LH5914-45     | Slave  | 45ns  | 48     | 600-Mil Plastic DIP |

| LH5914-55     | Slave  | 55ns  | 48     | 600-Mil Plastic DIP |

| LH5914U-35    | Slave  | 35ns  | 52     | PLCC                |

| LH5914U-45    | Slave  | 45ns  | 52     | PLCC                |

| LH5914U-55    | Slave  | 55ns  | 52     | PLCC                |

## Sales Representatives, Distributors, and Regional Sharp Offices

AL, Huntsville . . . . Interep Assoc. (205) 881-1096 AL, Mobile ..... Interep Assoc. (205) 478-1036 AZ, Scottsdale . . . . . T.D.S.I., Inc. (602) 998-2444 CA, Newport Beach . . . . Plustronics (714) 476-8009 CA, Ojai · · · · · Plustronics (805) 646-1950 CA, San Diego . . Mesa Components (619) 278-8021 CA, Technical Sales . . Quorum Technical Sales (408) 980-0812 CA, Sherman Oaks . . . . Plustronics (818)995-8908 CT, Southington . Orion/DSA Group (203) 621-8371 CO, Denver . . . . . . Seale & Assoc. (303) 756-8855 FL, Boca Raton . . . Lawrence Assoc. (407) 368-7373 FL, Paim Bay .... Lawrence Assoc. (407) 951-0901 FL, Palm Harbor . . . Lawrence Assoc. (813) 787-2773 FL, Winter Springs. . . Lawrence Assoc. (407) 365-1945 GA, Norcross · · · · · · · Interep (404) 449-8680 IL, Des Plaines . . Electron Marketing (312) 298-2330

IN, Indianapolis (317) 844-9227 KS, Wichita. ···· Baka Corp. (316) 682-8411 MA, Mariboro . . . Orion/DSA Group (508) 480-0516 MA, Peabody . . . . Orion/DSA Group (508) 532-6266 MD, Towson . . . . . . . . . . . ATS (301) 296-9360 MI, Grand Rapids . . . DEM Sales, Inc. (616) 364-4024 MI, St. Clair Shores. . . DEM Sales, Inc. (313) 777-1750 MN, Minneapolis . . . Comstrand, Inc. (612) 788-9234 MO, St. John . . . . . . Baka Corp. (314) 429-2252 NJ, Allendale .... Eastec Assoc (201) 934-7135 (716) 586-9002 NC, Raleigh .... Zucker Assoc. Inc. (919) 782-8433 OH, Dayton . . 5 Star Electronics, Inc. (513) 299-1718 OH, Solon . . . . . 5 Star Electronics (216) 349-1611 OR, Beaverton . . . . . Blair Hirsh Co. (503) 641-1875 PA, Erdenheim 5 Star Electronics, Inc. (215) 233-4600 TN. Greeneville . . · · · · · Interep (615) 639-3491

TX, Austin . . . . . Impaq Sales Co. (512) 474-1125 TX, Carrollton . . . . Impag Sales Co. (214) 247-3300 TX, Houston . . . . . Impaq Sales Co. (713) 820-0288 UT, Salt Lake City . . . Seale & Assoc. (801) 266-9056 VA, Richmond . . . Advanced Tech. (804) 320-8756 WA, Lynnwood . . . Blair Hirsh Co. (206) 774-8151 Canada, Surrey, BC . . . . . . . . · · · · · . . . . Enerlec Sales, Ltd (604) 888-1667 Canada, Mississauga, Ont. . . . . . High Tech Sales, Ltd. (416) 672-0284

#### Distributors:

| • • • • • | . Added Value Electronics   |

|-----------|-----------------------------|

| • • • • • | Marshall Industries         |

|           | · · · · · · · · · · Milgray |

|           | Space Electronics           |

| ••••      | Western Micro Technology    |

#### Sharp Regional Offices:

| Carson, CA        | .(213) 637-9488 |

|-------------------|-----------------|

|                   | .(508) 975-1979 |

| Lawrenceville, GA | .(404) 995-0717 |

| Dailas, TX        | .(214) 991-5185 |

| Mahwah, NJ        | .(201) 529-8758 |

| Santa Clara, CA   | .(408) 727-7914 |

Specifications are subject to change without notice. Preliminary data sheets contain minimum and maximum limits based upon design objectives, which are subject to change upon full characterization over the specified operating conditions.

# SHARP

#### In North America

#### In Europe

#### In Asia

Sharp Corporation IC Group 2613-1 Ichinomoto-Cho Tenri City, Nara 632, Japan Phone . . . . . (07436)5-1321 Telex . 5522-364(SHARPEL J)

Ref Code SMT88012B CSharp Corp. June 11, 1989 Printed in USA

| Slow 128Kx8 (0.8 um CMOS TFT)                                                                            | Slow 32Kx8 (1.0 um CMOS)                         |                        |                        |                        | 8Kx8 (1.2 um CMOS) | 16Kx1 (1.2um CMOS) |           |                        | 2Kx8 w/ WE, CE1, CE2 (1.2um CMOS) |           |                        |           | 2Kx8 w/ CE, CS, WE (1.2um CMOS) |           |                        |           | 2Kx8 w/ CE, OE, WE (1.2um CMOS) |           |           | 2Kx8 w/ CE, OE, WE (1.2um CMOS) | 1Kx4 (3.5 um CMOS) | 256x4 (3.5 um CMOS) | Slow Static RAMs<br>Low-Low Power Full CMOS | Organizational<br>Structure P | SHARP Static F                                             |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------|------------------------|------------------------|--------------------|--------------------|-----------|------------------------|-----------------------------------|-----------|------------------------|-----------|---------------------------------|-----------|------------------------|-----------|---------------------------------|-----------|-----------|---------------------------------|--------------------|---------------------|---------------------------------------------|-------------------------------|------------------------------------------------------------|

| LH511000<br>LH511000N<br>LH511000T<br>LH511000TR                                                         | LH51256<br>LH51256N                              | LH5160N<br>LH5160HN    | LH5160HD               | LH5160D                | LH5160             | LH5167             | LH5118N   | LH5118H                | LH5118                            | LH5117N   | LH5117H                | LH5117D   | LH5117                          | LH5116N   | LH5116H                | LH5116D   | LH5116                          | LH5115N   | LH5115D   | LH5115                          | LH5114H            | LH5101              |                                             | SHARP<br>Part Number          | RAM & Dual Po                                              |

| 100/120 ns<br>100/120 ns<br>100/120 ns<br>100/120 ns                                                     | 100/120 ns<br>100/120 ns                         | 100 ns<br>100 ns       | 100 ns<br>100 ns       | 100 ns                 | 100 ns             | 55/70 ns           | 100 ns    | 100 ns                 | 100 ns                            | 100 ns    | 100 ns                 | 100 ns    | 100 ns                          | 100 ns    | 100 ns                 | 100 ns    | 100 ns                          | 55/70 ns  | 55/70 ns  | 55/70 ns                        | 150 ns             | 300/450 ns          |                                             | Access<br>Time                | SHARP Static RAM & Dual Port Static RAM Availability Guide |

| 1 uA<br>1 uA<br>1 uA<br>1 uA                                                                             | 1 uA<br>1 uA                                     | 1 uA<br>1 uA           | 1 uA<br>1 uA           | 1 uA                   | 1 uA               | 1 uA               | 1 uA      | 1 uA                   | 1 uA                              | 1 uA      | 1 uA                   | 1 uA      | 1 uA                            | 1 uA      | 1 uA                   | 1 uA      | 1 uA                            | 10 uA     | 10 uA     | 10 uA                           | 5 uA               | 10 uA               |                                             | Standby<br>Current            | ailability Gui                                             |

| 0.6" DIP<br>0.525" SOP<br>TSOP<br>reverse TSOP                                                           | 0.6" DIP<br>0.45"SOP                             | 0.45" SOP<br>0.45" SOP | 0.6" UIP<br>0.3" SDIP  | 0.3" SDIP              | 0.6" DIP           | 0.3" DIP           | 0.45" SOP | 0.6" DIP               | 0.6" DIP                          | 0.45" SOP | 0.6" DIP               | 0.3" SDIP | 0.6" DIP                        | 0.45" SOP | 0.6" DIP               | 0.3" SDIP | 0.6" DIP                        | 0.45" SOP | 0.3" SDIP | 0.6" DIP                        | 0.3" DIP           | 0.4" DIP            |                                             | Package<br>Options            |                                                            |

| Jan '91<br>Jan '91<br>Apr '91<br>Apr '91                                                                 | Nov '90<br>Oct '90                               | now                    | now                    | now                    | NOM                | call               | call      | call                   | call                              | call      | call                   | call      | call                            | now       | Aug '90                | now       | now                             | call      | call      | call                            | now                | NOM                 |                                             | Sample<br>Avail               | {7/13/90 update}                                           |

| Apr '91<br>Apr '91<br>Jul '91<br>Jul '91                                                                 | Jan '91<br>Dec '90                               | now                    | now<br>call            | call                   | NOM                | call               | call      | call                   | call                              | call      | call                   | call      | call                            | now       | Sep '90                | now       | NOM                             | call      | call      | call                            | now                | now                 |                                             | Prod<br>Avail                 | Pa                                                         |

| pending<br>pending<br>pending                                                                            | yes<br>yes                                       | yes<br>yes             | yes<br>yes             | yes                    | yes                | yes                | yes       | yes                    | yes                               | yes       | yes                    | yes       | yes                             | yes       | yes                    | yes       | yes                             | yes       | pending   | Ves                             | yes                | yes                 |                                             | Data<br>Sheet                 | Page 1                                                     |

| utilizes TFT technology<br>utilizes TFT technology<br>utilizes TFT technology<br>utilizes TFT technology | industrial temperature<br>Industrial temperature | industrial temperature | industrial temperature | industrial temperature |                    |                    |           | industrial temperature |                                   |           | industrial temperature |           |                                 |           | industrial temperature |           |                                 |           |           |                                 |                    |                     |                                             | Notes and<br>Features         |                                                            |

:

17

|                                      | Feh '01 May '01 | 32Kx8 (0.8 um CMOS) LH52258AD 15/20/25 ns 1 mA 0.3" SDIP 1991 1991 pe<br>LH52258AK 15/20/25 ns 1 mA 0.3" SOJ 1991 1991 pe | LH52258K 35/45 ns 1 mA 0.3" SOJ now Jul '90<br>LH52258N 45 ns 1 mA 0.45" SOP Jun '90 Sep '90 | 1 mA 0.3" SDIP now now | 64Kx4 (0.8 um CMOS) LH52253D 15/20 ns 1 mA 0.3" SDIP Apr '91 May '91 pe<br>LH52253K 15/20 ns 1 mA 0.3" SOJ Apr '91 May '91 pe | 64Kx4 (1.2 um CMOS) LH52255 35/45 ns n/a 0.3" SDIP now now | 64Kx4 (0.8 um CMOS)      LH52252BD      15/20 ns      1 mA      0.3" SDIP      1991      1991      pe        LH52252BK      15/20 ns      1 mA      0.3" SOJ      1991      1991      pe | 64Kx4 (1.0 um CMOS) LH52252AD 25/35 ns 1 mA 0.3" SDIP now now LH52252AK 25/35 ns 1 mA 0.3" SOJ now now | 64Kx4 (1.2 um CMOS) LH52252 35/45 ns 1 mA 0.3" SDIP now now | LH52251AK 25/35 ns 1 mA 0.3" SOJ now now | 1 H52251AD 25/35 ns 1 mA 0.3" SDIP now now | 3) LH52251 35/45 ns 1 mA 0.3" SDIP now now | 64Kx1 (1.2 um CMOS) LH5261 25/35 ns 1 mA 0.3" SDIP now now | Fast Static RAMs | 1991     | 55/70/100 ns 1 mA 0.4" DIP 1991 1991 | Slow 32Kx8 (1.0 um CMOS) LH52250D 55/70/100 ns 1 mA 0.3" SDIP now now | L 70/90 ns 100 uA 0.45" SOP now now | Slow 32Kx8 (1.2 um CMOS) LH52256 120 ns 2 mA 0.6" DIP now now<br>LH52256L 70/90/120 ns 100 uA 0.6" DIP now now | Slow Static RAMs<br>Mixed MOS | Organizational      SHARP      Access      Standby      Package      Sample      Prod      I        Structure      Part Number      Time      Current      Options      Avail      S | al Port Static RAM Availability Guide {7/13/90 update} |

|--------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------|--------------------------------------------|--------------------------------------------|------------------------------------------------------------|------------------|----------|--------------------------------------|-----------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 0.4" SOJ Aug '90<br>0.4" DIP Mar '91 |                 | •                                                                                                                         | ·                                                                                            | -                      | -                                                                                                                             | •                                                          | -                                                                                                                                                                                        | -                                                                                                      | -                                                           |                                          | •                                          | -                                          | -                                                          |                  |          | -                                    |                                                                       | -                                   |                                                                                                                |                               |                                                                                                                                                                                      | {7/13/90 update                                        |

| Aug '90 yes<br>May '91 yes           |                 | 1991 pending<br>1991 pending                                                                                              | ð                                                                                            |                        | May '91 pending<br>May '91 pending                                                                                            | now yes                                                    | 1991 pending<br>1991 pending                                                                                                                                                             | now yes<br>now yes                                                                                     | now yes                                                     |                                          |                                            | now yes                                    | now yes                                                    |                  | 1991 yes |                                      | now yes                                                               |                                     | now yes                                                                                                        |                               | Prod Data<br>Avail Sheet                                                                                                                                                             | Page 2                                                 |

| limited volume til October           | :               |                                                                                                                           |                                                                                              |                        | Output Enable version<br>Output Enable version                                                                                | Chip Select version                                        | Chip Enable version<br>Chip Enable version                                                                                                                                               | Chip Enable version<br>Chip Enable version                                                             | Chip Enable version                                         |                                          |                                            |                                            |                                                            |                  |          |                                      |                                                                       |                                     |                                                                                                                |                               | Notes and<br>Features                                                                                                                                                                |                                                        |

| SHARP Stat                    | SHARP Static RAM & Dual Port Static RAM Availability Guide | ort Static RAM Av                                                       | ailability Gui     | ide (7/13/9               | 90 update)         | Pa                 | Page 3             |                                                |

|-------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------|--------------------|---------------------------|--------------------|--------------------|--------------------|------------------------------------------------|

| Organizational<br>Structure   | SHARP<br>Part Number                                       | Access<br>Time                                                          | Standby<br>Current | Package<br>Options        | Sample<br>Avail    | Prod<br>Avail      | Data<br>Sheet      | Notes and<br>Features                          |

| Dual Port Static RAMs         |                                                            |                                                                         |                    |                           |                    |                    |                    |                                                |

| 2Kx8 Dual Port, Master        | LH5911                                                     | 35/45/55 ns                                                             | 5 mA *             | 48-pin DIP                | Call               | 06, Inf            | yes                | Compatible w/ IDT7132                          |

| 2Kx8 Dual Port, Master w/ Int | LH5912U                                                    | 35/45/55 ns                                                             | 5 mA *             | 52-pin PLCC               | Dec '90            | Feb '91            | yes                | Compatible w/ IDT71321                         |

| 2Kx8 Dual Port, Slave         | LH5914<br>LH5914U                                          | 35/45/55 ns<br>35/45/55 ns                                              | 5 mA *<br>5 mA *   | 48-pin DIP<br>52-pin PLCC | 90, Dec<br>06, Dec | Aug '90<br>Feb '91 | yes<br>yes         | Compatible w/ IDT7142<br>Compatible w/ IDT7142 |

| 4Kx8 Dual Port                | LH5920<br>LH5920U                                          | 35/45/55 ns<br>35/45/55 ns                                              | 5 mA *<br>5 mA *   | 48-pin DIP<br>52-pin PLCC | Nov '90            | Jan '91<br>Jan '91 | yes<br>yes         | Compatible w/ IDT7134<br>Compatible w/ IDT7134 |

| 4Kx8 Dual Port, Master w/ Int | LH5926U                                                    | 35/45/55 ns                                                             | 5 mA *             | 52-pin PLCC               | Sep '90            | Oct '90            | yes                | w/ Arbitration                                 |

| 4Kx8 Dual Port, Slave         | LH5924U                                                    | 35/45/55 ns                                                             | 5 mA *             | 52-pin PLCC               | Oct '90            | Nov '90            | yes                | w/ Arbitration                                 |

| 8Kx8 Dual Port w/ Semaphore   | LH5933U                                                    | 25/35/45 ns                                                             | TBD                | 52-pin PLCC               | Feb '91            | Apr '91            | pending            |                                                |

|                               |                                                            | * Dual Port SRAM Standby Current with both Enable inputs => Vcc - 0.2 V | ndby Current w     | ith both Enable inpu      | ts => Vcc - 0.2    | V                  |                    |                                                |

|                               |                                                            | across the full operating temperature range                             | ting temperature   | a range                   |                    |                    |                    |                                                |

| Wide-Word Static RAMs         |                                                            |                                                                         |                    |                           |                    |                    |                    |                                                |

| Slow 16Kx18 (0.8 um CMOS)     | LH52270<br>LH52270U                                        | 45/55 ns<br>45/55 ns                                                    | TBD<br>TBD         | 48-pin DIP<br>52-pin PLCC | May-91<br>May-91   | Jul-91<br>Jul-91   | pending<br>pending |                                                |

| Fast 16Kx18 (0.8 um CMOS)     | LH52278<br>LH52278U                                        | 20/25/30 ns<br>20/25/30 ns                                              | TBD<br>TBD         | 48-pin DIP<br>52-pin PLCC | May-91<br>May-91   | Jul-91<br>Jul-91   | pending<br>pending |                                                |

| Slow 64Kx18 (0.8 um CMOS)     | LH521020<br>LH521020U                                      | 45/55 ns<br>45/55 ns                                                    | tbd<br>Tbd         | 48-pin DIP<br>52-pin PLCC | Apr-91<br>Apr-91   | Jun-91<br>Jun-91   | pending<br>pending |                                                |

| Fast 64Kx18 (0.8 um CMOS)     | LH521028<br>LH521028U                                      | 20/25/30 ns<br>20/25/30 ns                                              | tbd<br>tbd         | 48-pin DIP<br>52-pin PLCC | Mar-91<br>Mar-91   | May-91<br>May-91   | yes<br>yes         |                                                |

|                               |                                                            |                                                                         |                    |                           |                    |                    |                    |                                                |

19