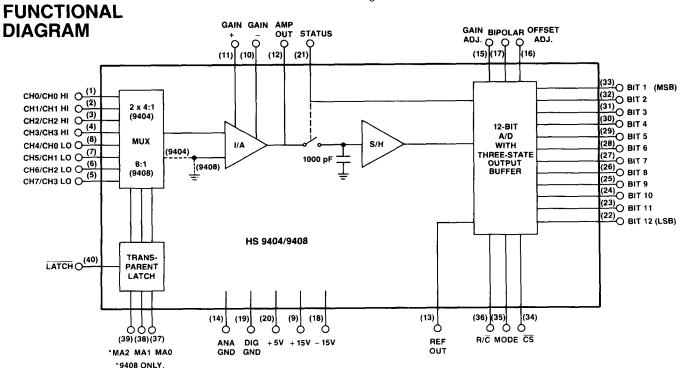

# HS 9404/9408 8-Channel, 12-Bit Data Acquisition System (DAS)

# **FEATURES**

- Complete 12-Bit DAS

8-Channel Multiplexer

Instrumentation Amp with Programmable Gain

Sample/Hold Circuit

12-Bit A/D

3-State Output Buffer

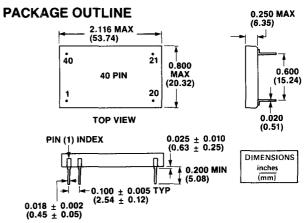

- 40 Pin DIP

- 35 kHz Throughput

- Low Power

# DESCRIPTION

The HS 9404 and HS 9408 are compact, single-package solutions to multichannel acquisition applications. These units are complete data acquisition systems which include input multiplexing, instrumentation amplifier with programmable gain, sample and hold circuit, 12-bit A/D converter, and control logic. Accuracy and linearity are specified for the complete system from analog input to digital output. The need for ordinary component specifications such as instrumentation amp linearity, gain accuracy, and sample-hold pedestal error are eliminated, as they are guaranteed in system specifications.

The HS9404 offers four differential inputs while the HS 9408 provides eight single-ended inputs. Both devices feature overvoltage input protection (to  $\pm$  35V) and the instrumentation amp provides gain ranges of 1 to 100\*. The gain range is selected through the use of a single external resistor and allows a variable

input range of  $\pm$  100 mV to  $\pm$  10V. Expansion to seven differential or fifteen single-ended inputs is easily accomplished with two additional ICs.

Total system linearity is specified as  $\pm\,1/2\,LSB$  at 25 °C and  $\pm\,3/4\,LSB$  is guaranteed over the military operating temperature range. System throughput rates of up to 35 kHz can be achieved, while a three-state output buffer permits easy interface with a microprocessor bus.

The HS 9404 and HS 9408 operate from  $\pm$  15V and  $\pm$  5V with a total power dissipation of 950 mW and 825 mW respectively. Both models are offered in 40-pin ceramic packages and are specified for operation from 0 °C to 70 °C for commercial grades and  $\pm$  55 °C to  $\pm$  125 °C with MIL-STD-883 Rev. C, Levels B or S screening for military grades.

\*Gain can be set to higher values but operation to 12-bit accuracy is not guaranteed.

# PRELIMINARY TECHNICAL DATA

# **SPECIFICATIONS**

(Typical @ +25°C and nominal power supplies unless otherwise specified)

| ANALOG INPUTS                                               |                                             |

|-------------------------------------------------------------|---------------------------------------------|

| Number of Inputs<br>HS 9404<br>HS 9408                      | 4 Differential<br>8 Single-Ended            |

| Input Voltage Range <sup>3</sup><br>Unipolar<br>Bipolar     | 0 to +10V<br>±10V or ±5V1                   |

| Common Mode Voltage Range                                   | ± 10V                                       |

| CMRR <sup>2</sup> G = 1 @ 200 Hz, Vcm = 20 Vpp              | 90 dB                                       |

| Input Bias Current<br>+25°C<br>-55°C to +125°C              | ± 15 nA typ, ± 100 nA max<br>± 200 nA (max) |

| Input Resistance                                            | 10¹2Ω typ                                   |

| Input Capacitance<br>OFF Channel<br>ON Channel 9404<br>9408 | 5 pF<br>10 pF<br>10 pF                      |

| Gain Equation (A <sub>V</sub> )                             | 20K<br>R <sub>G</sub> + 1                   |

| DIGITAL INPUTS                                              |                                             |

| Logic Levels  |                  |

|---------------|------------------|

| Logic "1"     | 2.0V min         |

| Logic "0"     | 0.8V max         |

| Logic Loading | 1 LSTTL load max |

| STATIC PERFORMANCE <sup>3</sup>                        |                                                                                  |

|--------------------------------------------------------|----------------------------------------------------------------------------------|

| Integral Nonlinearity <sup>5</sup> (K)<br>(T)<br>(S,J) | ± ½ LSB over temperature<br>± ¾ LSB over temperature<br>± 1 LSB over temperature |

| Differential Nonlinearity (T,K) (S,J)                  | <ul><li>± 1 LSB over temperature</li><li>± 2 LSB over temperature</li></ul>      |

| No Missing Codes (T,K)<br>(S,J)                        | 12 bits over temperature<br>11 bits over temperature                             |

| Unipolar Offset Error <sup>3,4</sup>                   | ± 0.05% max                                                                      |

| Bipolar Minus Full Scale Error <sup>3,4</sup>          | $\pm 0.05\%$ typ, $\pm 0.1\%$ max                                                |

| Gain Error4                                            | $\pm 0.1\%$ typ, $\pm 0.3\%$ max                                                 |

| Channel to Channel Offset Voltage                      | 1 mV max                                                                         |

### **DYNAMIC PERFORMANCE** Throughput Rate

| Gain = 1                          | 35 kHz |

|-----------------------------------|--------|

| Gain = 10                         | 28 kHz |

| Gain = 100                        | 15 kHz |

| vetem Acquisition Time (201/ eten |        |

System Acquisition (0.01%) to A/D Input

$3.5 \mu$  sec typ,  $10 \mu$  sec max<sup>3</sup> A/D Conversion Time  $25 \mu \text{ sec typ}$ ,  $30 \mu \text{ sec max}$ S/H Feedthrough Attenuation 90 dB

MUX Crosstalk Attenuation (off isolation) 68 dB t Settling, MUX IN to AMP OUT

(0.01%) 2.5 μ sec 10 μ sec 40 μ sec Gain = 1 Gain = 10 Gain = 100 Slew Rate, AMP OUT 13V/µsec

Adjacent Channel Coupling Error<sup>7</sup> (V<sub>IN</sub> = 20 Vp-p sine wave) – 78 dB @ 40 kHz – 90 dB @ 0.5 kHz

### **DRIFT CHARACTERISTICS**

| Integral Nonlinearity        | ±2 ppm/°C   |

|------------------------------|-------------|

| Differential Nonlinearity    | ±2 ppm/°C   |

| Unipolar Offset <sup>6</sup> | ± 10 ppm/°C |

| Bipolar Zero <sup>6</sup>    | ± 10 ppm/°C |

| Gain <sup>6</sup>            | ± 25 ppm/°C |

|                              |             |

# **DIGITAL OUTPUTS**

| narv        |

|-------------|

| roi y<br>TV |

|             |

# **POWER SUPPLIES**

| Power Supply Range  |                            | ± 15V, ± 5%<br>5V, ± 5% |        |       |

|---------------------|----------------------------|-------------------------|--------|-------|

| PSRR (all supplies) | 0.002%/% typ, 0.005%/% max |                         |        |       |

|                     | HS 9                       | 404                     | HS 9   | 408   |

| Current Drain       | TYP                        | MAX                     | TYP    | MAX   |

| + 15V               | 25 mA                      | 42 mA                   | 21 mA  | 37 mA |

| – 15V               | 32 mA                      | 52 mA                   | 28 mA  | 46 mA |

| + 5V                | 16 mA                      | 26 mA                   | 16 mA  | 23 mA |

| Power Dissipation   | 947 mW                     | 1.52W                   | 821 mW | 1.34W |

|                     |                            |                         |        |       |

### **TEMPERATURE RANGE**

| Operating (J,K) | 0°C to +70°C    |  |

|-----------------|-----------------|--|

| Operating (S,T) | -55°C to +125°C |  |

| Storage         | -65°C to +150°C |  |

| PACKAGE         |                 |  |

| Weight          | 15 grams        |  |

### NOTES:

- 1. Input range selected at factory.

- 2. HS 9404 only.

- 3. Unity gain configured.

- Adjustable to zero; see application notes.

- 5. End point definition

- Gain and offset drift specifications as stated in data sheet are maximum (average) limits over the given temperature range, tested at temperature end points.

- For best performance above 1 kHz, connect package lid to analog ground.

NOTE: Initial commercial offerings will be in ceramic with future offerings in plastic.

### **PIN ASSIGNMENTS**

| PIN FUNCTION   |             | PIN | FUNCTION     |

|----------------|-------------|-----|--------------|

| 1              | CH0/CH0 HI  | 40  | LATCH        |

| 2              | CH1/CH1 HI  | 39  | MA2*         |

| 3              | CH2/CH2 HI  | 38  | MA1          |

| 4              | СН3/СН3 Н1  | 37  | MA0          |

| 5              | CH7/CH3 LO  | 36  | R/C          |

| 6              | CH6/CH2 LO  | 35  | MODE         |

| 7              | CH5/CH1 LO  | 34  | <u>CS</u>    |

| 8              | CH4/CH0 LO  | 33  | BIT 1 (MSB)  |

| 9              | + 15V       | 32  | BIT 2        |

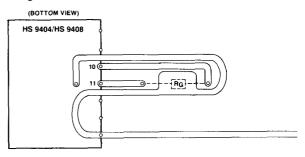

| 10 GAIN (-)    |             | 31  | BIT 3        |

| 11             | 11 GAIN (+) |     | BIT 4        |

| 12             | AMP OUT     | 29  | BIT 5        |

| 13             | REF OUT     | 28  | BIT 6        |

| 14             | ANALOG GND  | 27  | BIT 7        |

| 15 GAIN ADJ    |             | 26  | BIT 8        |

| 16 OFFSET ADJ  |             | 25  | BIT 9        |

| ] 17   BIPOLAR |             | 24  | BIT 10       |

| 18 - 15V       |             | 23  | BIT 11       |

| 19             | DIGITAL GND | 22  | BIT 12 (LSB) |

| 20             | + 5V        | 21  | STATUS       |

<sup>\*</sup>HS 9408 only

# **ABSOLUTE MAXIMUM RATINGS** (HS 9404/HS 9408)

| + 15V (+ V <sub>DD</sub> )                                           | + 16.5V                                    |

|----------------------------------------------------------------------|--------------------------------------------|

| – 15V ( – V <sub>DD</sub> )                                          | - 16.5V                                    |

| +5V (+V <sub>CC</sub> )                                              | + 7V                                       |

| Analog GND to Digital GND                                            | ± 0.5V                                     |

| Digital Inputs to Digital GND                                        | + 5.5V max<br>- 0.5V min                   |

| Analog Inputs to Analog GND Pins 1 through 8 Pins 10, 11, 15, 16, 17 |                                            |

| Amp Out to Analog or Digital GND                                     | Indefinite short circuit                   |

| REFOUT to Analog or Digital GND                                      |                                            |

| Voltage on Digital Ouputs in Tri-State Mode                          | + V <sub>CC</sub> + 0.5V max<br>- 0.5V min |

| Lead Temperature, Soldering                                          | 300°C, 10 sec                              |

282

# **APPLICATIONS INFORMATION**

### **CONTROL FUNCTIONS**

The HS 9404/HS 9408 contains control functions necessary to provide for microprocessor interface. All control functions are defined in Tables 1, 2, and 3.

| FUNCTION      | DEFINITION   | FUNCTION                                                                        |

|---------------|--------------|---------------------------------------------------------------------------------|

| R/C           | Read/Convert | 1 initiates conversion                                                          |

|               |              | High (1) initiates read     along with CS                                       |

| <del>cs</del> | Chip Select  | High (1) disconnects     data bus                                               |

|               |              | Low (0) connects data     bus                                                   |

| Latch         | Latch        | High (1) transparent     Low (0) MUX address     latched                        |

| MA0           | Multiplexer  | Select Channels                                                                 |

| MA1<br>MA2*   | Address      | (see MUX Logic Table 3)                                                         |

| MODE          | 12-bit/8-bit | High (1) indicates 8-bit conversion     Low (0) indicates     12-bit conversion |

<sup>\*</sup>HS 9408 only

Table 1. Defining the Control Functions

| CONTRO | OL INPUTS |                                     |

|--------|-----------|-------------------------------------|

| R/₹    | <u>cs</u> | OPERATION                           |

| 7_     | 0         | Initiates conversion                |

| 1      | 1         | Output goes to high impedance state |

| 1      | 0         | tnitiates read                      |

Table 2. Truth Table - Control Inputs

| MUX ADDRESS INPUTS |     | CHANNEL SELECTED |                |         |

|--------------------|-----|------------------|----------------|---------|

| MA2*               | MA1 | MAO              | HS 9404        | HS 9408 |

| 0                  | 0   | 0                | CH0 HI/CH0 LOW | CH0     |

| 0                  | 0   | 1                | CH1 HI/CH1 LOW | CH1     |

| 0                  | 1   | 0                | CH2 HI/CH2 LOW | CH2     |

| 0                  | 1   | 1                | CH3 HI/CH3 LOW | СНЗ     |

| 1                  | 0   | 0                |                | CH4     |

| 1                  | 0   | 1                | _              | CH5     |

| 1                  | 1   | 0                | _              | CH6     |

| 1                  | 1   | 1                | _              | CH7     |

Table 3. Truth Table - Multiplexer Address

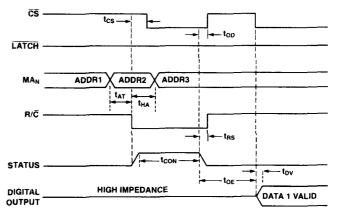

# TIMING

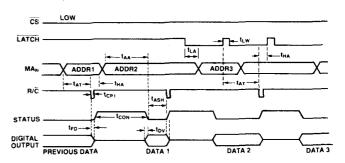

The timing diagram in Figure 1 shows how the HS 9404/HS 9408 works when controlled by a microprocessor. The normal sequence of events is as follows:

- 1. The input signal is acquired by the MUX, AMP and S/H (track mode) after the MUX address is changed.

- 2. A conversion is initiated by the  $R/\overline{C}$  control line going to logic "0". Concurrent with this event, the status line goes to logic "1" to indicate the A/D is

"busy". When the A/D is "busy", the S/H is in the hold mode.

- 3. The A/D indicates completion of the conversion by returning the status line to logic "0".

- 4. Data is placed on the output bus when the R/C control line is set to logic "1" and when the CS line is set to logic "0".

Reference Figure 1 for timing constraints of various operations.

Figure 2 shows the timing requirements for standalone operation. The major difference between stand-alone and bus compatible operation is the use of the CS control line. Since stand-alone operation does not require the output data to arrive at a specified time, the  $\overline{CS}$  line is kept at logic "0". This presents output data immediately after conversion is complete. Reference Figure 2 for timing constraints of various operations.

- CHIP SELECT DELAY TIME - 100 nsec MAX. tes

-- OUTPUT DISABLE DELAY AFTER TO OF STATUS - 35 nsec MAX. top

TOTAL ACQUISITION TIME OF MUX, AMP, S/H (TRACK MODE) — SEE SPECIFICATIONS. TAT

S/H HOLD APERTURE TIME - 500 nsec.

- READ SETUP TIME - 0 need MIN

- OUTPUT ENABLE SETUP TIME - 0 nsec MIN. toE

- DATA VALID TIME - 250 nsec

-- CONVERSION TIME OF A/D -- 25 µsec (12 BITS). 17 µsec (8 BITS).

Figure 1. Timing for Bus Compatible DAS

TOTAL ACQUISITION TIME OF MUX, AMP, S/H (TRACK MODE) -

NEGATIVE CONVERT PULSE WIDTH - 150 nsec MIN., 1 µsec MAX.

- OUTPUT FLOAT DELAY TIME - 150 nsec

- CONVERSION TIME OF A/D - 25 μsec. - S/H HOLD APERTURE TIME - 500 nsec.

- MUX AND AMP ACQUISITION TIME - SEE SPECIFICATIONS.

- S/H ACQUISITION TIME - 3 usec TYP., 7 usec, MAX..

- DATA VALID TIME - 250 nsec

- LATCH TO ADDRESS CHANGE TIME - 30 nsec tLA

- LATCH PULSE WIDTH - 80 nsec MIN.

Figure 2. Timing for Stand-Alone Operation

<sup>\*</sup>Applies to HS 9408 only. Latch high allows MUX address to MUX

Latch low latches the address present during low edge and keeps that channel

### OFFSET AND GAIN CONNECTIONS

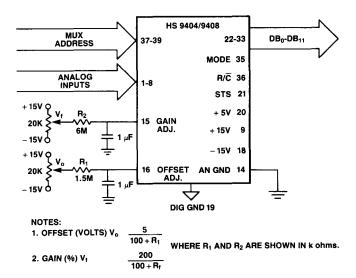

The DAS is normally used with external offset and gain calibration potentiometers. However, if maximum accuracy is not required, they may be omitted. The offset control has a range of about  $\pm 20$  LSB, and the gain control has a range of about  $\pm 13$  LSB.

Proper gain and offset calibration requires great care and the use of extremely sensitive and accurate instruments. The voltage source used as a signal input must be very stable. It also should be capable of being set to within 1/10 LSB at both ends of its range.

The DAS's offset and gain adjustments are independent of each other if the offset adjustment is made first. To minimize transition noise at the gain and offset pins, a 1  $\mu$  F decoupling capacitor should be connected as shown on the diagram of Figure 3.

Figure 3. Gain and Offset Input Connections

# OFFSET ADJUSTMENT PROCEDURE

- 1. For unipolar ranges:

- a) Set input voltage precisely to + 1/2 LSB.

- b) Adjust zero control until converter is switching from 0000000000000 to 00000000001.

- 2. For bipolar ranges:

- a) Set input voltage precisely to 1/2 LSB above \_ FS

- b) Adjust zero control until converter is switching from 0000000000000 to 00000000001.

### **GAIN ADJUSTMENT PROCEDURE**

- 1. Set input voltage precisely to 1/2 LSB less than 'all bits on' value. Note that this is 1-1/2 LSB less than nominal full scale.

- 2. Adjust gain control until converter is switching from 111111111111 to 11111111111.

### GAIN ADJUSTMENT PROCEDURE (continued)

Table 4 summarizes the offset and gain adjustment procedure and shows the proper input test voltages used in calibrating the DAS.

| Input<br>Voltage<br>Range | Adjustment     | Input<br>Voltage    | Adjust input to point<br>where converter is<br>just on the verge of<br>switching between<br>the two codes shown.1 |

|---------------------------|----------------|---------------------|-------------------------------------------------------------------------------------------------------------------|

| 0 to +10V                 | OFFSET<br>GAIN | 1.22 mV<br>9.9963V  | 00000000000<br>000000000001<br>111111111110<br>111111                                                             |

| ± 5V                      | OFFSET<br>GAIN | -4.9988V<br>4.9963V | 00000000000<br>000000000001<br>111111111110                                                                       |

| ±10V                      | OFFSET         | - 9.9976V           | 11111111111<br>000000000000<br>000000000001<br>111111                                                             |

|                           | GAIN           | 9.9927V             | 111111111111111111111111111111111111111                                                                           |

Codes shown are natural binary for unipolar input ranges and offset binary for bipolar ranges.

Table 4. Calibration Data

Note: For bipolar operation, OFFSET adjust sets – full scale (or all zeros out code), not 0V in (midscale code).

The offset and gain adjustments at pins 16 and 15 only affect the A/D converter. The offset adjustment as shown should have enough range to compensate for any internal errors. If the internal amplifier is used at greater than unity gain, a gain adjustment should be added to the RG circuit of the instrumentation amplifier.

# **GROUNDING CONSIDERATIONS**

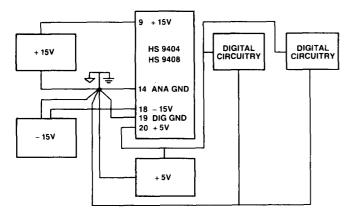

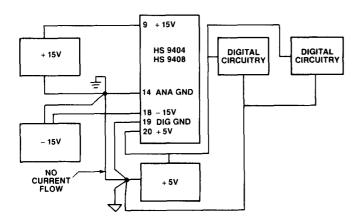

To insure maximum accuracy, the HS 9404/ HS 9408s have a separate analog and digital ground; these two grounds must be routed properly to prevent DC and transient errors.

DC errors can be caused by current flowing through a run resistance between the system ground reference and the DAS ground reference. (One mA through  $2.5\Omega$  will cause an LSB of error.) The best way to prevent this type of error is to connect the digital and analog grounds very close to the HS 9404 or HS 9408 and use this point as the system ground. This can be done as a so-called ''star ground'' as shown in Figure 5a or as shown in Figure 5b. In Figure 5a, the single common ground reference insures no ground current or ground loop errors. The circuit of Figure 5b sends all digital currents to the digital supply reference thereby preventing any digital current flow through a common ground supply return.

# **APPLICATIONS INFORMATION** (continued)

### **GROUNDING CONSIDERATIONS** (continued)

Figure 5a.

Figure 5b.

Since all ground currents are returned to their respective power supplies, no current flows through the connection between analog and digital ground; this causes both ground points to be at the same potential.

To minimize transient-caused errors, decoupling capacitors are recommended between all supplies and their respective grounds. The HS 9404 and HS 9408 have three 0.01 µF ceramic bypass capacitors inside, so an external 10 µF for each supply should be all that is required.

# INSTRUMENTATION **AMPLIFIER & ANALOG FRONT END**

The HS 9404 has a full instrumentation amplifier with high impedance differential inputs and resistor programmable gain. The output of the amplifier is available for driving other analog circuitry or accessing the signal after amplification. Be aware that any loading in excess of 2 K ohms in parallel with 10 pF will adversely affect output voltage swing and settling time.

The formulas for calculating gain and the gain resistor are as follows:

$$AV = \frac{20K}{R_G} + 1 \qquad R_G = \frac{20K}{AV - 1}$$

Some typical values are as follows:

GAIN 5 10 50 100 202.0Ω RG infinite 5.000 K Ω 2.222 K Ω 408.2Ω

Special care must be exercised when operating at high gains (>20) to avoid coupling error signals into the relatively high impedance GAIN (-) and GAIN (+) pins. The gain set resistor should be placed as close to the HS 9404/9408 package as possible and the connections should be guarded with a quiet, low impedance signal trace such as analog ground, REF OUT. + 15V or AMP OUT. The use of a ground plane is preferred. To minimize gain errors due to temperature, a low drift (low temperature coefficient of resistance) resistor should be used for RG with a TCR < 25 ppm/°C over the required temperature range.

Reference output current capability decreases as temperature increases. If REF OUT must supply more than +1 mA above 70°C, an external current buffer is recommended.

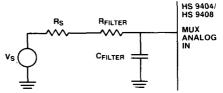

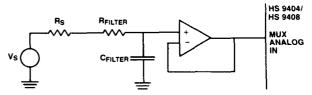

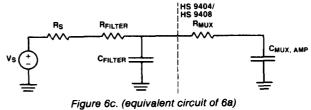

If the circuit is to be used at or near its maximum throughput rate, care must be used to prevent dynamic errors due to source impedance at the multiplexer inputs. If a low-pass anti-alias filter is used at the analog inputs (Figure 6a), it is suggested that a buffer be used (Figure 6b) to eliminate charge-transfer errors between CFILTER and CMUX AMP (Figure 6c).

Figure 6a. (not recommended)

Figure 6b. (recommended)

# **APPLICATIONS INFORMATION** (continued)

# UNIPOLAR/BIPOLAR CONFIGURATION

The HS 9404/HS 9408 - 2 are 20 volt range units which must be operated in bipolar configuration to give a  $\pm$  10V input signal range (for unity gain amplification). The HS 9404/HS 9408 - 1 are 10 volt range units which can be operated in unipolar or bipolar modes.

To connect for bipolar operation, short pin 17 to pin 13. For unipolar operation, short pin 17 to analog ground.

Noise performance is improved in bipolar mode if pin 17 is decoupled to analog ground with a 0.01  $\mu$  F ceramic capacitor. (This value may be inadequate at + 125 °C, causing the reference to oscillate.)

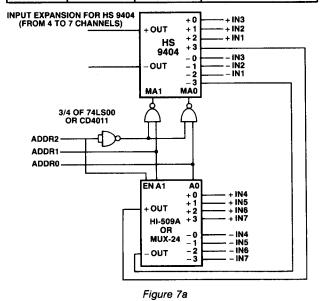

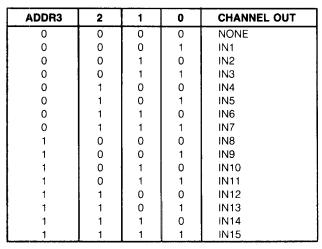

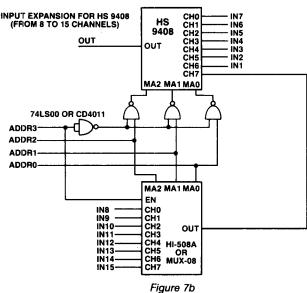

### INPUT EXPANSION

The DAS is configured with either an 8-channel single-ended or 4-channel differential input. This was done to optimize package size and cost. In the event the user wishes to increase the number of input channels, examples of input expansion are shown in Figures 7a and 7b.

| ADDR2 | ADDR1 | ADDR0 | CHANNEL OUT |

|-------|-------|-------|-------------|

| 0     | 0     | 0     | NONE        |

| 0     | 0     | 1     | ±IN1        |

| 0     | 1     | 0     | ± IN2       |

| 0     | 1     | 1     | ± IN3       |

| 1     | 0     | 0     | ± IN4       |

| 1     | 0     | 1     | ± IN5       |

| 1     | 1     | 0     | ± IN6       |

| 1     | 1     | 1     | ±IN7        |

# **ORDERING INFORMATION**

| MODEL<br>NUMBER | INTEGRAL<br>LINEARITY | INPUT<br>RANGE(S) | TEMPERATURE RANGE | SCREENING  |

|-----------------|-----------------------|-------------------|-------------------|------------|

| HS 940X-J1      | ±1 LSB                | ±5V, 0 to +10V    | 0°C to +70°C      | 0.4% AQL   |

| HS 940X-J2      | ±1 LSB                | ± 10V             | 0°C to +70°C      | 0.4% AQL   |

| HS 940X-K1      | ± 1/2 LSB             | ±5V, 0 to +10V    | 0°C to +70°C      | 0.4%AQL    |

| HS 940X-K2      | ± 1/2 LSB             | ± 10V             | 0°C to +70°C      | 0.4% AQL   |

| HS 940X-S/B-1   | ±1 LSB                | ± 5V. 0 to + 10V  | -55°C to +125°C   | 883 Rev. C |

| HS 940X-S/B-2   | ±1 LSB                | ± 10V             | - 55°C to + 125°C | 883 Rev. C |

| HS 940X-T/B-1   | ± 1⁄2 LSB             | ±5V, 0 to +10V    | - 55°C to + 125°C | 883 Rev. C |

| HS 940X-T/B-2   | ± 1⁄2 LSB             | ± 10V             | - 55°C to + 125°C | 883 Rev. C |

| N<br>1. | OTES:<br>H\$     | 940 <u>X</u>      |

|---------|------------------|-------------------|

|         | MIODEL<br>SUFFIX | INPUT<br>CHANNELS |

|         | 4                | 4 DI              |

|         | 8                | 8 SE              |