32,768-word × 8-bit High Speed CMOS Static RAM

# **HITACHI**

ADE-203-135D (Z) Rev. 4.0 Nov. 29, 1995

### **Description**

The Hitachi HM62256B is a CMOS static RAM organized 32-kword  $\times$  8-bit. It realizes higher performance and low power consumption by employing 0.8  $\mu$ m Hi-CMOS process technology. The device, packaged in 8  $\times$  14 mm TSOP, 8  $\times$  13.4 mm TSOP with thickness of 1.2 mm, 450-mil SOP (foot print pitch width), 600-mil plastic DIP, or 300-mil plastic DIP, is available for high density mounting. It offers low power standby power dissipation; therefore, it is suitable for battery back-up systems.

#### **Features**

· High speed

Fast access time: 45/55/70/85 ns (max)

• Low power

Standby: 1.0 µW (typ)

Operation: 25 mW (typ) (f = 1 MHz)

- Single 5 V supply

- Completely static memory

No clock or timing strobe required

- Equal access and cycle times

- Common data input and output

Three state output

- Directly TTL compatible All inputs and outputs

- Capability of battery back up operation

# **Ordering Information**

| Type No.                                                               | Access Time             | Package                               |

|------------------------------------------------------------------------|-------------------------|---------------------------------------|

| HM62256BLP-7                                                           | 70 ns                   | 600-mil 28-pin plastic DIP (DP-28)    |

| HM62256BLP-7SL                                                         | 70 ns                   | _                                     |

| HM62256BLSP-7                                                          | 70 ns                   | 300-mil 28-pin plastic DIP (DP-28NA)  |

| HM62256BLSP-7SL                                                        | 70 ns                   | _                                     |

| HM62256BLFP-7T                                                         | 70 ns                   | 450-mil 28-pin plastic SOP (FP-28DA)  |

| HM62256BLFP-4SLT <sup>-1</sup><br>HM62256BLFP-5SLT<br>HM62256BLFP-7SLT | 45 ns<br>55 ns<br>70 ns | _                                     |

| HM62256BLFP-7ULT                                                       | 70 ns                   | _                                     |

| HM62256BLT-8                                                           | 85 ns                   | 8 mm × 14 mm 32-pin TSOP (TFP-32DA)   |

| HM62256BLT-7SL                                                         | 70 ns                   | _                                     |

| HM62256BLTM-8                                                          | 85 ns                   | 8 mm × 13.4 mm 28-pin TSOP (TFP-28DA) |

| HM62256BLTM-4SL <sup>*1</sup><br>HM62256BLTM-5SL<br>HM62256BLTM-7SL    | 45 ns<br>55 ns<br>70 ns | _                                     |

| HM62256BLTM-7UL                                                        | 70 ns                   |                                       |

Note: 1. Under development

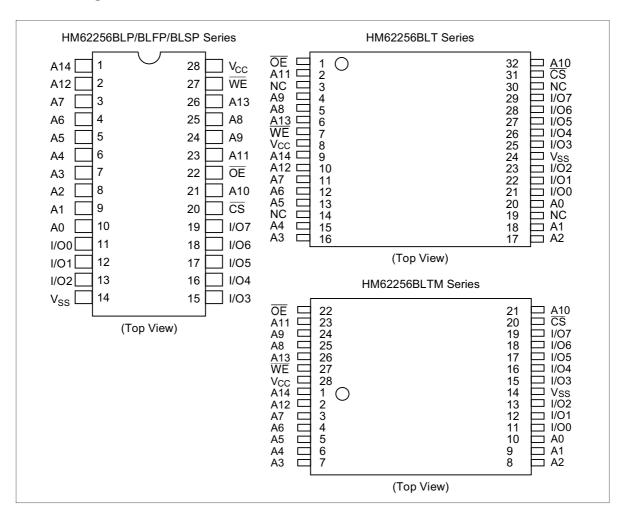

### **Pin Arrangement**

### **Pin Description**

| Symbol          | Function      |

|-----------------|---------------|

| A0 – A14        | Address       |

| 1/00 – 1/07     | Input/output  |

| CS              | Chip select   |

| WE              | Write enable  |

| ŌĒ              | Output enable |

| NC              | No connection |

| V <sub>cc</sub> | Power supply  |

| $V_{ss}$        | Ground        |

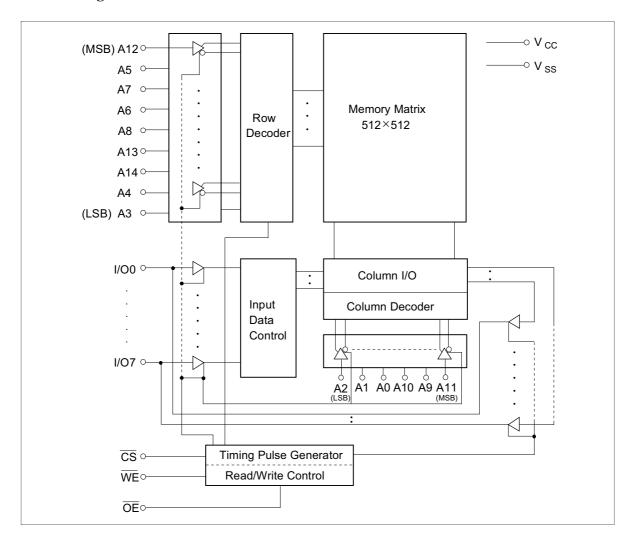

# **Block Diagram**

### **Function Table**

| WE | CS | ŌĒ | Mode           | V <sub>cc</sub> Current            | I/O Pin | Ref. Cycle         |

|----|----|----|----------------|------------------------------------|---------|--------------------|

| X  | Н  | Х  | Not selected   | I <sub>SB</sub> , I <sub>SB1</sub> | High-Z  | _                  |

| Н  | L  | Н  | Output disable | I <sub>cc</sub>                    | High-Z  | _                  |

| Н  | L  | L  | Read           | I <sub>cc</sub>                    | Dout    | Read cycle (1)–(3) |

| L  | L  | Н  | Write          | I <sub>cc</sub>                    | Din     | Write cycle (1)    |

| L  | L  | L  | Write          | I <sub>cc</sub>                    | Din     | Write cycle (2)    |

Note: X: H or L

# **Absolute Maximum Ratings**

| Parameter                          | Symbol          | Value                              | Unit |

|------------------------------------|-----------------|------------------------------------|------|

| Power supply voltage <sup>*1</sup> | V <sub>cc</sub> | -0.5 to +7.0                       | V    |

| Terminal voltage <sup>*1</sup>     | V <sub>T</sub>  | $-0.5^{*2}$ to $V_{CC} + 0.3^{*3}$ | V    |

| Power dissipation                  | P <sub>T</sub>  | 1.0                                | W    |

| Operating temperature              | Topr            | 0 to + 70                          | °C   |

| Storage temperature                | Tstg            | -55 to +125                        | °C   |

| Storage temperature under bias     | Tbias           | -10 to +85                         | °C   |

Notes: 1. Relative to V<sub>ss</sub>

2.  $V_T$  min: -3.0 V for pulse half-width  $\leq 50$  ns

3. Maximum voltage is  $7.0\ V$

# **Recommended DC Operating Conditions** (Ta = 0 to +70°C)

| Parameter                    | Symbol          | Min                | Тур | Max                  | Unit |

|------------------------------|-----------------|--------------------|-----|----------------------|------|

| Supply voltage               | V <sub>cc</sub> | 4.5                | 5.0 | 5.5                  | V    |

|                              | $V_{ss}$        | 0                  | 0   | 0                    | V    |

| Input high (logic 1) voltage | V <sub>IH</sub> | 2.2                |     | V <sub>cc</sub> +0.3 | V    |

| Input low (logic 0) voltage  | V <sub>IL</sub> | -0.5 <sup>*1</sup> | _   | 0.8                  | V    |

Note: 1.  $V_{IL}$  min: -3.0 V for pulse half-width  $\leq 50$  ns

DC Characteristics (Ta = 0 to +70°C,  $V_{CC}$  = 5 V  $\pm 10\%$ ,  $V_{SS}$  = 0 V)

| Parameter                              |            | Symbol           | Min | Typ*1 | Max              | Unit | Test Conditions                                                                                                                                                                                                                            |

|----------------------------------------|------------|------------------|-----|-------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input leakage current                  |            | ILI              | _   | _     | 1                | μΑ   | Vin = V <sub>SS</sub> to V <sub>CC</sub>                                                                                                                                                                                                   |

| Output leakage current                 |            | I <sub>LO</sub>  | _   |       | 1                | μΑ   | $\overline{\text{CS}} = \text{V}_{\text{IH}} \text{ or } \overline{\text{OE}} = \text{V}_{\text{IH}} \text{ or } \overline{\text{WE}} = \text{V}_{\text{IL},}$ $\text{V}_{\text{SS}} \leq \text{V}_{\text{I/O}} \leq \text{V}_{\text{CC}}$ |

| Operating power supply current         |            | I <sub>cc</sub>  | _   | 6     | 15               | mA   | $\overline{\text{CS}} = \text{V}_{\text{IL}}$ others = $\text{V}_{\text{IH}}/\text{V}_{\text{IL}}$<br>$\text{I}_{\text{I/O}} = 0 \text{ mA}$                                                                                               |

| Average operating power supply current | HM62256B-4 | I <sub>cc1</sub> |     |       | 70               | mA   | min cycle, duty = 100 %, $I_{I/O} = 0$<br>$\frac{mA}{CS} = V_{IL}$ , others = $V_{IH}/V_{IL}$                                                                                                                                              |

|                                        | HM62256B-5 | I <sub>CC1</sub> | _   | _     | 60               |      |                                                                                                                                                                                                                                            |

|                                        | HM62256B-7 | I <sub>CC1</sub> | _   | 33    | 60               |      |                                                                                                                                                                                                                                            |

|                                        | HM62256B-8 | I <sub>CC1</sub> | _   | 29    | 50               |      |                                                                                                                                                                                                                                            |

|                                        | -          | I <sub>CC2</sub> | _   | 5     | 15               | mA   | Cycle time = 1 $\mu$ s, $I_{I/O}$ = 0 mA<br>$\overline{CS}$ = $V_{IL}$ , $V_{IH}$ = $V_{CC}$ , $V_{IL}$ = 0                                                                                                                                |

| Standby power supply current           |            | I <sub>SB</sub>  | _   | 0.3   | 2                | mA   | CS = V <sub>IH</sub>                                                                                                                                                                                                                       |

|                                        |            | I <sub>SB1</sub> | _   | 0.2   | 100              | μΑ   | $Vin \geq 0 \ V, \ \overline{CS} \geq V_{\text{CC}} - 0.2 \ V,$                                                                                                                                                                            |

|                                        |            |                  | _   | 0.2*2 | 50 <sup>*2</sup> |      |                                                                                                                                                                                                                                            |

|                                        |            |                  |     | 0.2*3 | 10 <sup>*3</sup> |      |                                                                                                                                                                                                                                            |

| Output low voltage                     |            | V <sub>oL</sub>  | _   | _     | 0.4              | V    | I <sub>OL</sub> = 2.1 mA                                                                                                                                                                                                                   |

| Output high voltage                    |            | V <sub>OH</sub>  | 2.4 | _     | _                | V    | I <sub>OH</sub> = -1.0 mA                                                                                                                                                                                                                  |

Notes: 1. Typical values are at  $V_{cc}$  = 5.0 V, Ta = +25°C and not guaranteed.

- 2. This characteristics is guaranteed only for L-SL version.

- 3. This characteristics is guaranteed only for L-UL version.

# **Capacitance** (Ta = $25^{\circ}$ C, f = 1.0 MHz)\*1

| Parameter                  | Symbol           | Min | Тур | Max | Unit | Test Conditions        |

|----------------------------|------------------|-----|-----|-----|------|------------------------|

| Input capacitance*1        | Cin              | _   | _   | 8   | pF   | Vin = 0 V              |

| Input/output capacitance*1 | C <sub>I/O</sub> | _   |     | 10  | pF   | V <sub>I/O</sub> = 0 V |

Note: 1. This parameter is sampled and not 100% tested.

AC Characteristics (Ta = 0 to +70°C,  $V_{CC}$  = 5 V ± 10%, unless otherwise noted.)

#### **Test Conditions**

• Input pulse levels: 0.8 V to 2.4 V

• Input rise and fall times: 5 ns

• Input and output timing reference level: 1.5 V

• Output load: HM62256B-4: 1 TTL Gate + C<sub>L</sub> (30 pF)(Including scope & jig)

HM62256B-5: 1 TTL Gate +  $C_L$  (50 pF)(Including scope & jig) HM62256B-7/8: 1 TTL Gate +  $C_L$  (100 pF)(Including scope & jig)

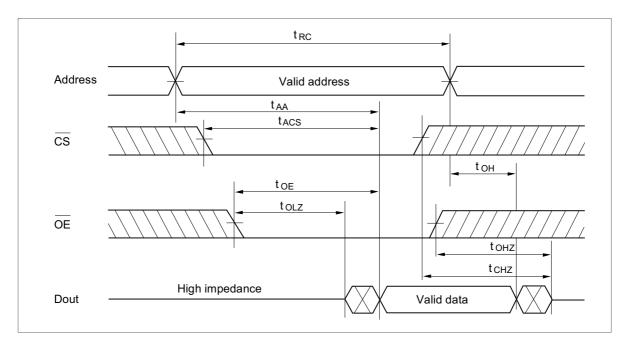

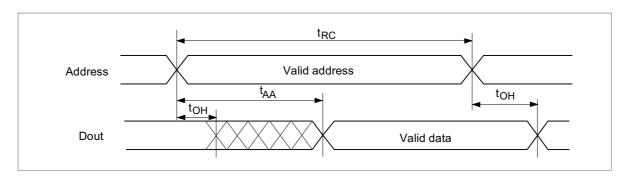

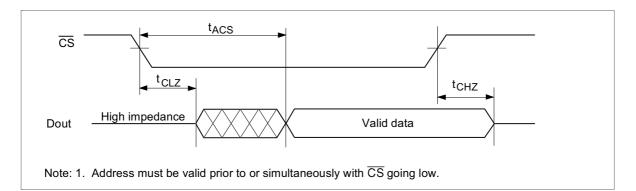

#### **Read Cycle**

#### HM62256B

|                                         |                  | -4  |     | -5  |     | -7  |     | -8  |     |      |       |

|-----------------------------------------|------------------|-----|-----|-----|-----|-----|-----|-----|-----|------|-------|

| Parameter                               | Symbol           | Min | Max | Min | Max | Min | Max | Min | Max | Unit | Notes |

| Read cycle time                         | t <sub>RC</sub>  | 45  | _   | 55  | _   | 70  | _   | 85  | _   | ns   |       |

| Address access time                     | t <sub>AA</sub>  | _   | 45  | _   | 55  | _   | 70  | _   | 85  | ns   |       |

| Chip select access time                 | t <sub>ACS</sub> | _   | 45  |     | 55  | _   | 70  | _   | 85  | ns   |       |

| Output enable to output valid           | t <sub>oe</sub>  |     | 30  | _   | 35  | _   | 40  | _   | 45  | ns   |       |

| Chip selection to output in low-Z       | t <sub>CLZ</sub> | 5   | _   | 5   | _   | 10  | _   | 10  | _   | ns   | 2     |

| Output enable to output in low-Z        | t <sub>oLZ</sub> | 5   | _   | 5   | _   | 5   | _   | 5   |     | ns   | 2     |

| Chip deselection in to output in high-Z | t <sub>CHZ</sub> | 0   | 20  | 0   | 20  | 0   | 25  | 0   | 30  | ns   | 1, 2  |

| Output disable to output in high-Z      | t <sub>OHZ</sub> | 0   | 20  | 0   | 20  | 0   | 25  | 0   | 30  | ns   | 1, 2  |

| Output hold from address change         | t <sub>oh</sub>  | 5   |     | 5   | _   | 5   | _   | 10  | _   | ns   |       |

Notes: 1. t<sub>CHZ</sub> and t<sub>OHZ</sub> defined as the time at which the outputs achieve the open circuit conditions and are not referred to output voltage levels.

<sup>2.</sup> This parameter is sampled and not 100% tested.

# Read Timing Waveform (1) $(\overline{WE}=V_{IH})$

# Read Timing Waveform (2) $(\overline{WE}{=}V_{IH},\overline{CS}{=}V_{IL},\overline{OE}{=}V_{IL})$

# Read Timing Waveform (3) $(\overline{WE} = V_{IH}, \overline{OE} = V_{IL})^{*1}$

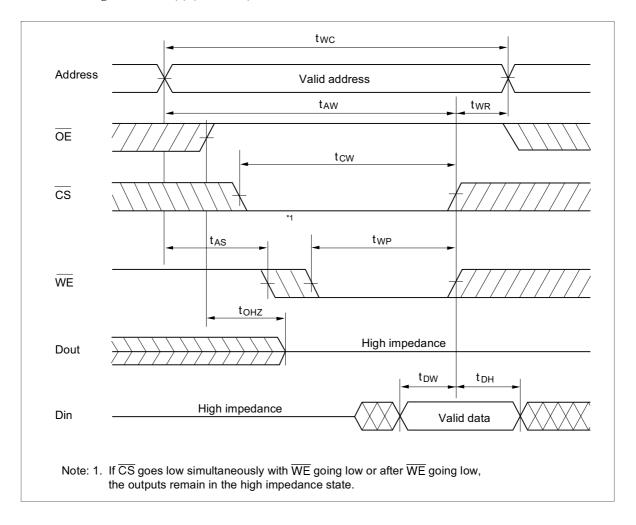

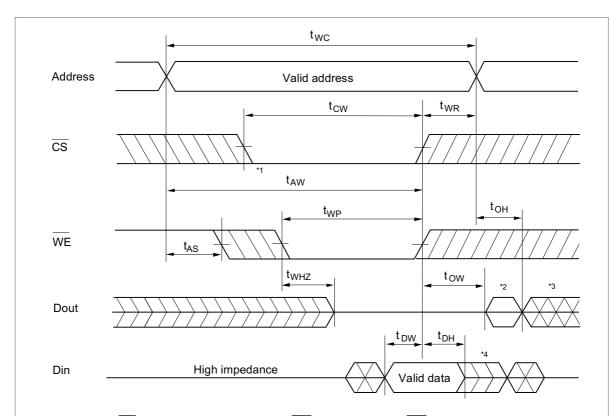

#### Write Cycle

#### HM62256B

|                                    |                  | -4  |     | -5  |     | -7  |     | -8  |     | •    |         |

|------------------------------------|------------------|-----|-----|-----|-----|-----|-----|-----|-----|------|---------|

| Parameter                          | Symbol           | Min | Max | Min | Max | Min | Max | Min | Max | Unit | Notes   |

| Write cycle time                   | t <sub>wc</sub>  | 45  | _   | 55  | _   | 70  | _   | 85  | _   | ns   |         |

| Chip selection to end of write     | t <sub>cw</sub>  | 35  | _   | 40  | _   | 60  | _   | 75  | _   | ns   | 4       |

| Address setup time                 | t <sub>AS</sub>  | 0   | _   | 0   | _   | 0   | _   | 0   | _   | ns   | 5       |

| Address valid to end of write      | t <sub>AW</sub>  | 35  | _   | 40  |     | 60  | _   | 75  | _   | ns   |         |

| Write pulse width                  | t <sub>wP</sub>  | 30  | _   | 35  | _   | 50  | _   | 55  | _   | ns   | 3, 8    |

| Write recovery time                | t <sub>wR</sub>  | 0   | _   | 0   | _   | 0   | _   | 0   | _   | ns   | 6       |

| WE to output in high-Z             | t <sub>whz</sub> | 0   | 20  | 0   | 20  | 0   | 25  | 0   | 40  | ns   | 1, 2, 7 |

| Data to write time overlap         | t <sub>DW</sub>  | 20  | _   | 25  | _   | 30  | _   | 35  | _   | ns   |         |

| Data hold from write time          | t <sub>DH</sub>  | 0   | _   | 0   |     | 0   | _   | 0   | _   | ns   |         |

| Output active from end of write    | t <sub>ow</sub>  | 5   | _   | 5   | _   | 5   | _   | 5   | _   | ns   | 2       |

| Output disable to output in high-Z | t <sub>ohz</sub> | 0   | 20  | 0   | 20  | 0   | 25  | 0   | 40  | ns   | 1, 2, 7 |

Notes: 1. t<sub>OHZ</sub> and t<sub>WHZ</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referred to output voltage levels.

- 2. This parameter is sampled and not 100% tested.

- 3. A write occurs during the overlap  $(t_{WP})$  of a low  $\overline{CS}$  and a low  $\overline{WE}$ . A write begins at the later transition of  $\overline{CS}$  going low or  $\overline{WE}$  going low. A write ends at the earlier transition of  $\overline{CS}$  going high or  $\overline{WE}$  going high.  $t_{WP}$  is measured from the beginning of write to the end of write.

- 4.  $t_{cw}$  is measured from  $\overline{CS}$  going low to the end of write.

- 5.  $\,t_{\mbox{\tiny AS}}$  is measured from the address valid to the beginning of write.

- 6.  $t_{wR}$  is measured from the earlier of  $\overline{WE}$  or  $\overline{CS}$  going high to the end of write cycle.

- 7. Durng this period, I/O pins are in the output state so that the input signals of the opposite phase to the outputs must not be applied.

- In the write cycle with OE low fixed, t<sub>wP</sub> must satisfy the following equation to avoid a problem of data bus contention, t<sub>wP</sub> ≥ t<sub>wHZ</sub> max + t<sub>DW</sub> min.

# Write Timing Waveform (1) (OE Clock)

Write Timing Waveform (2)  $(\overline{OE} \text{ Low Fixed}) (\overline{OE} = V_{IL})$

Notes: 1. If  $\overline{CS}$  goes low simultaneously with  $\overline{WE}$  going low or after  $\overline{WE}$  going low, the outputs remain in the high impedance state.

- 2. Dout is the same phase of the write data of this write cycle.

- 3. Dout is the read data of next address.

- 4. If  $\overline{\text{CS}}$  is low during this period, I/O pins are in the output state. Therefore, the input signals of the opposite phase to the output must not be applied to them.

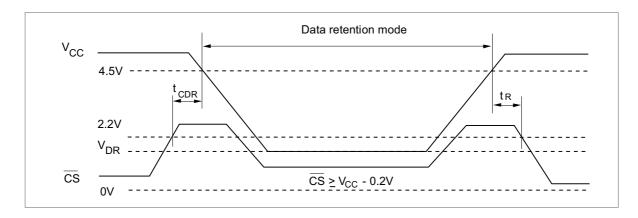

# Low $V_{cc}$ Data Retention Characteristics (Ta = 0 to +70°C)

| Parameter                            | Symbol            | Min                | Typ*1 | Max              | Unit | Test Conditions <sup>*6</sup>                                                                  |

|--------------------------------------|-------------------|--------------------|-------|------------------|------|------------------------------------------------------------------------------------------------|

| V <sub>cc</sub> for data retention   | $V_{DR}$          | 2.0                | _     | 5.5              | V    | $\overline{\text{CS}} \ge \text{V}_{\text{CC}} - 0.2 \text{ V},$ $\text{Vin } \ge 0 \text{ V}$ |

| Data retention current               | I <sub>CCDR</sub> | _                  | 0.05  | 30 <sup>*2</sup> | μΑ   | $V_{cc}$ = 3.0 V, $Vin \ge 0$ V                                                                |

|                                      |                   | _                  | 0.05  | 10 <sup>*3</sup> |      | $\overline{\text{CS}} \ge V_{\text{CC}} - 0.2 \text{ V},$                                      |

|                                      |                   | _                  | 0.05  | 3 <sup>*4</sup>  |      |                                                                                                |

| Chip deselect to data retention time | t <sub>CDR</sub>  | 0                  |       | _                | ns   | See retention waveform                                                                         |

| Operation recovery time              | t <sub>R</sub>    | t <sub>RC</sub> *5 |       |                  | ns   |                                                                                                |

Notes: 1. Typical values are at V<sub>cc</sub> = 3.0 V, Ta = 25°C and not guaranteed.

- 2.  $10 \mu A \text{ max at Ta} = 0 \text{ to} + 40^{\circ} \text{C}.$

- 3. This characteristics guaranteed for only L-SL version. 3  $\mu$ A max at Ta = 0 to +40°C.

- 4. This characteristics guaranteed for only L-UL version. 0.6  $\mu A$  max at Ta = 0 to +40°C.

- 5.  $t_{RC}$  = read cycle time.

- 6.  $\overline{CS}$  controls address buffer,  $\overline{WE}$  buffer,  $\overline{OE}$  buffer, and Din buffer. If  $\overline{CS}$  controls data retention mode, other input levels (address,  $\overline{WE}$ ,  $\overline{OE}$ , I/O) can be in the high impedance state.

### Low $V_{\text{CC}}$ Data Retention Timing Waveform

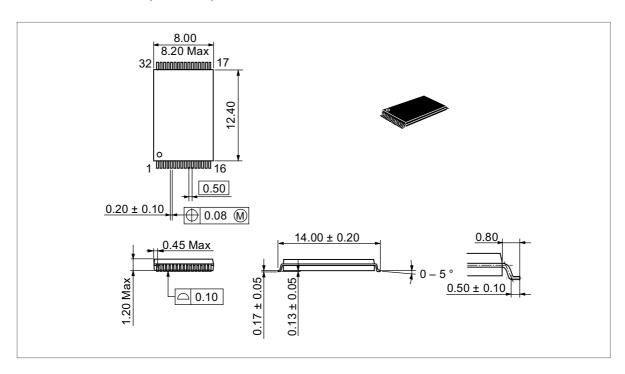

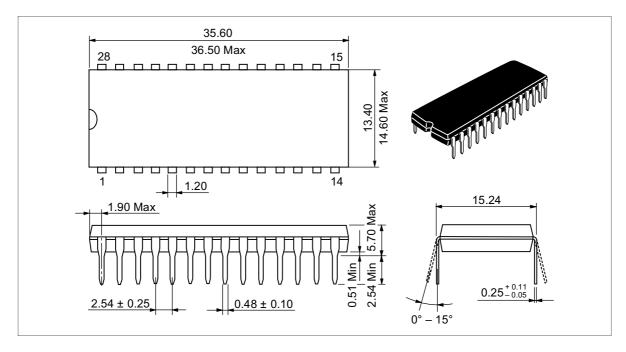

### **Package Dimensions**

HM62256BLP Series (DP-28)

Unit: mm

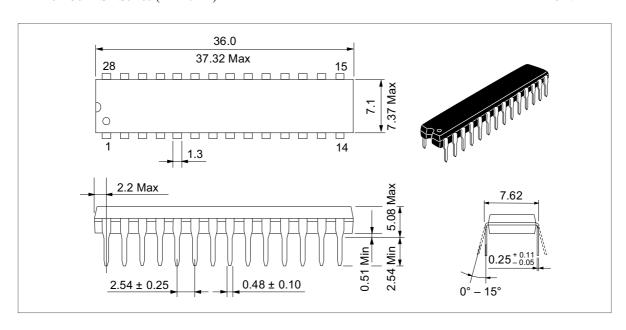

### HM62256BLSP Series (DP-28NA)

Unit: mm

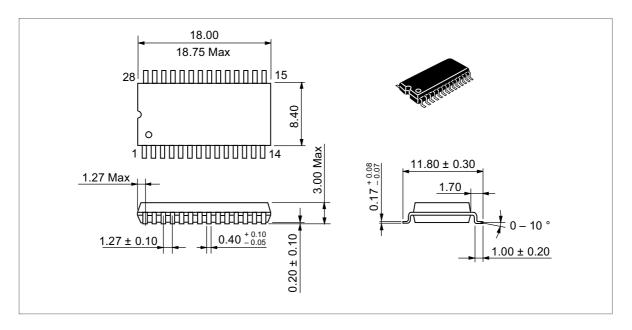

### HM62256BLFP Series (FP-28DA)

Unit: mm

### HM62256BLT Series (TFP-32DA)

Unit: mm