# **MAX 7000**

## Programmable Logic Device Family

#### September 2005, ver. 6.7

#### **Data Sheet**

# Features...

- High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX<sup>®</sup> architecture

- 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in MAX 7000S devices

- ISP circuitry compatible with IEEE Std. 1532

- Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices

- Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells

- Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2)

- 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect)

- PCI-compliant devices available

For information on in-system programmable 3.3-V MAX 7000A or 2.5-V MAX 7000B devices, see the *MAX 7000A Programmable Logic Device Family Data Sheet* or the *MAX 7000B Programmable Logic Device Family Data Sheet*.

| Table 1. MA              | X 7000 Devic | e Features |         |          |          |          |          |

|--------------------------|--------------|------------|---------|----------|----------|----------|----------|

| Feature                  | EPM7032      | EPM7064    | EPM7096 | EPM7128E | EPM7160E | EPM7192E | EPM7256E |

| Usable<br>gates          | 600          | 1,250      | 1,800   | 2,500    | 3,200    | 3,750    | 5,000    |

| Macrocells               | 32           | 64         | 96      | 128      | 160      | 192      | 256      |

| Logic array<br>blocks    | 2            | 4          | 6       | 8        | 10       | 12       | 16       |

| Maximum<br>user I/O pins | 36           | 68         | 76      | 100      | 104      | 124      | 164      |

| t <sub>PD</sub> (ns)     | 6            | 6          | 7.5     | 7.5      | 10       | 12       | 12       |

| t <sub>SU</sub> (ns)     | 5            | 5          | 6       | 6        | 7        | 7        | 7        |

| t <sub>FSU</sub> (ns)    | 2.5          | 2.5        | 3       | 3        | 3        | 3        | 3        |

| t <sub>CO1</sub> (ns)    | 4            | 4          | 4.5     | 4.5      | 5        | 6        | 6        |

| f <sub>CNT</sub> (MHz)   | 151.5        | 151.5      | 125.0   | 125.0    | 100.0    | 90.9     | 90.9     |

## Altera Corporation

| Table 2. MAX             | 7000S Device I | Features |          |          |          |          |

|--------------------------|----------------|----------|----------|----------|----------|----------|

| Feature                  | EPM7032S       | EPM7064S | EPM7128S | EPM7160S | EPM7192S | EPM7256S |

| Usable gates             | 600            | 1,250    | 2,500    | 3,200    | 3,750    | 5,000    |

| Macrocells               | 32             | 64       | 128      | 160      | 192      | 256      |

| Logic array<br>blocks    | 2              | 4        | 8        | 10       | 12       | 16       |

| Maximum<br>user I/O pins | 36             | 68       | 100      | 104      | 124      | 164      |

| t <sub>PD</sub> (ns)     | 5              | 5        | 6        | 6        | 7.5      | 7.5      |

| t <sub>su</sub> (ns)     | 2.9            | 2.9      | 3.4      | 3.4      | 4.1      | 3.9      |

| t <sub>FSU</sub> (ns)    | 2.5            | 2.5      | 2.5      | 2.5      | 3        | 3        |

| t <sub>CO1</sub> (ns)    | 3.2            | 3.2      | 4        | 3.9      | 4.7      | 4.7      |

| f <sub>CNT</sub> (MHz)   | 175.4          | 175.4    | 147.1    | 149.3    | 125.0    | 128.2    |

# ...and More Features

- Open-drain output option in MAX 7000S devices

- Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls

- Programmable power-saving mode for a reduction of over 50% in each macrocell

- Configurable expander product-term distribution, allowing up to 32 product terms per macrocell

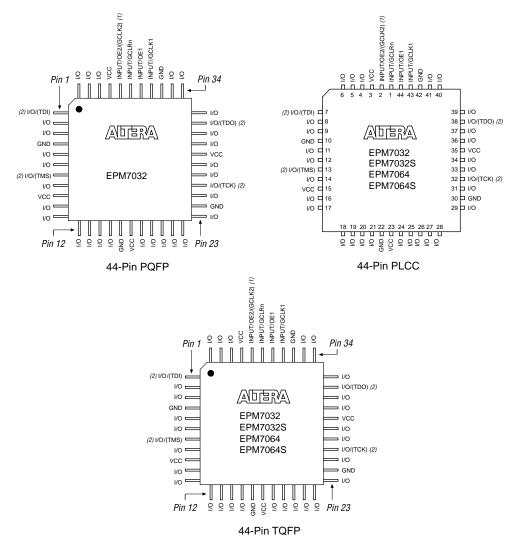

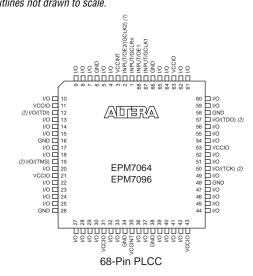

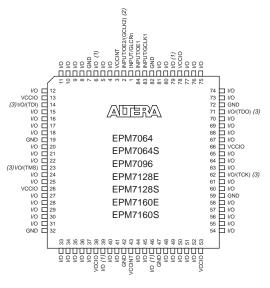

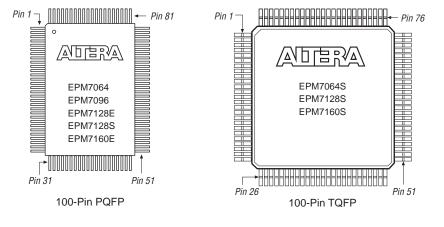

- 44 to 208 pins available in plastic J-lead chip carrier (PLCC), ceramic pin-grid array (PGA), plastic quad flat pack (PQFP), power quad flat pack (RQFP), and 1.0-mm thin quad flat pack (TQFP) packages

- Programmable security bit for protection of proprietary designs

- 3.3-V or 5.0-V operation

- MultiVolt<sup>TM</sup> I/O interface operation, allowing devices to interface with 3.3-V or 5.0-V devices (MultiVolt I/O operation is not available in 44-pin packages)

- Pin compatible with low-voltage MAX 7000A and MAX 7000B devices

- Enhanced features available in MAX 7000E and MAX 7000S devices

- Six pin- or logic-driven output enable signals

- Two global clock signals with optional inversion

- Enhanced interconnect resources for improved routability

- Fast input setup times provided by a dedicated path from I/O pin to macrocell registers

- Programmable output slew-rate control

- Software design support and automatic place-and-route provided by Altera's development system for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations

|                        | <ul> <li>Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, and VeriBest</li> <li>Programming support         <ul> <li>Altera's Master Programming Unit (MPU) and programming hardware from third-party manufacturers program all MAX 7000 devices</li> <li>The BitBlaster<sup>TM</sup> serial download cable, ByteBlasterMV<sup>TM</sup> parallel port download cable, and MasterBlaster<sup>TM</sup> serial/universal serial bus (USB) download cable program MAX 7000S devices</li> </ul> </li> </ul> |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General<br>Description | The MAX 7000 family of high-density, high-performance PLDs is based<br>on Altera's second-generation MAX architecture. Fabricated with<br>advanced CMOS technology, the EEPROM-based MAX 7000 family<br>provides 600 to 5,000 usable gates, ISP, pin-to-pin delays as fast as 5 ns,<br>and counter speeds of up to 175.4 MHz. MAX 7000S devices in the -5, -6,<br>-7, and -10 speed grades as well as MAX 7000 and MAX 7000E devices in<br>-5, -6, -7, -10P, and -12P speed grades comply with the PCI Special Interest<br>Group (PCI SIG) <i>PCI Local Bus Specification, Revision 2.2.</i> See Table 3<br>for available speed grades.                                                                                                         |

| Device   | Speed Grade  |              |              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |              |              |                      |              |  |

|----------|--------------|--------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|--------------|----------------------|--------------|--|

|          | -5           | -6           | -7           | -10P         | -10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -12P | -12          | -15          | -15T                 | -20          |  |

| EPM7032  |              | <b>&gt;</b>  | ~            |              | <b>&gt;</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | >            | ~            | <ul> <li></li> </ul> |              |  |

| EPM7032S | $\checkmark$ | $\checkmark$ | ~            |              | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |              |              |                      |              |  |

| EPM7064  |              | <b>&gt;</b>  | ~            |              | <b>&gt;</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | >            | ~            |                      |              |  |

| EPM7064S | $\checkmark$ | $\checkmark$ | ~            |              | <ul> <li>Image: A set of the set of the</li></ul> |      |              |              |                      |              |  |

| EPM7096  |              |              | $\checkmark$ |              | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | >            | $\checkmark$ |                      |              |  |

| EPM7128E |              |              | ~            | $\checkmark$ | <ul> <li>Image: A set of the set of the</li></ul> |      | <b>&gt;</b>  | ~            |                      | <b>~</b>     |  |

| EPM7128S |              | $\checkmark$ | ~            |              | <ul> <li>Image: A set of the set of the</li></ul> |      |              | ~            |                      |              |  |

| EPM7160E |              |              |              | ~            | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | $\checkmark$ | ~            |                      | $\checkmark$ |  |

| EPM7160S |              | $\checkmark$ | ~            |              | <ul> <li>Image: A start of the start of</li></ul> |      |              | ~            |                      |              |  |

| EPM7192E |              |              |              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ~    | >            | ~            |                      | <b>&gt;</b>  |  |

| EPM7192S |              |              | ~            | 1            | <b>~</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ī    |              | ~            |                      |              |  |

| EPM7256E |              |              |              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ~    | >            | ~            |                      | <b>&gt;</b>  |  |

| EPM7256S |              |              | $\checkmark$ |              | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |              | $\checkmark$ |                      |              |  |

The MAX 7000E devices—including the EPM7128E, EPM7160E, EPM7192E, and EPM7256E devices—have several enhanced features: additional global clocking, additional output enable controls, enhanced interconnect resources, fast input registers, and a programmable slew rate.

In-system programmable MAX 7000 devices—called MAX 7000S devices—include the EPM7032S, EPM7064S, EPM7128S, EPM7160S, EPM7192S, and EPM7256S devices. MAX 7000S devices have the enhanced features of MAX 7000E devices as well as JTAG BST circuitry in devices with 128 or more macrocells, ISP, and an open-drain output option. See Table 4.

| Feature                         | EPM7032<br>EPM7064<br>EPM7096 | All<br>MAX 7000E<br>Devices | All<br>MAX 7000S<br>Devices |

|---------------------------------|-------------------------------|-----------------------------|-----------------------------|

| ISP via JTAG interface          |                               |                             | $\checkmark$                |

| JTAG BST circuitry              |                               |                             | ✓(1)                        |

| Open-drain output option        |                               |                             | $\checkmark$                |

| Fast input registers            |                               | ~                           | $\checkmark$                |

| Six global output enables       |                               | ~                           | $\checkmark$                |

| Two global clocks               |                               | ~                           | $\checkmark$                |

| Slew-rate control               |                               | ~                           | $\checkmark$                |

| MultiVolt interface (2)         | $\checkmark$                  | ~                           | $\checkmark$                |

| Programmable register           | $\checkmark$                  | ~                           | $\checkmark$                |

| Parallel expanders              | $\checkmark$                  | ~                           | $\checkmark$                |

| Shared expanders                | $\checkmark$                  | ~                           | $\checkmark$                |

| Power-saving mode               | $\checkmark$                  | ~                           | $\checkmark$                |

| Security bit                    | $\checkmark$                  | ~                           | $\checkmark$                |

| PCI-compliant devices available | $\checkmark$                  | $\checkmark$                | $\checkmark$                |

Notes:

(1) Available only in EPM7128S, EPM7160S, EPM7192S, and EPM7256S devices only.

(2) The MultiVolt I/O interface is not available in 44-pin packages.

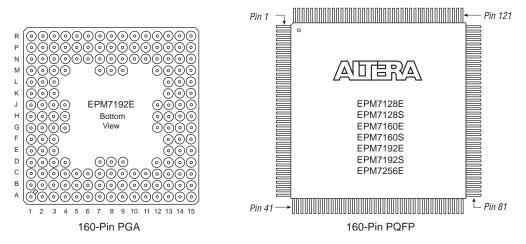

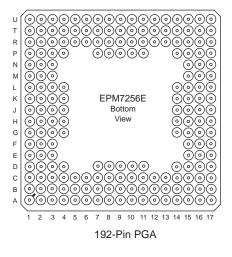

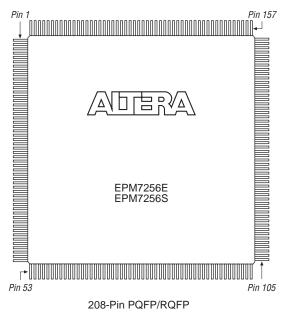

The MAX 7000 architecture supports 100% TTL emulation and high-density integration of SSI, MSI, and LSI logic functions. The MAX 7000 architecture easily integrates multiple devices ranging from PALs, GALs, and 22V10s to MACH and pLSI devices. MAX 7000 devices are available in a wide range of packages, including PLCC, PGA, PQFP, RQFP, and TQFP packages. See Table 5.

| Table 5. M | AX 7000            | ) Maxim            | um Use             | r I/O Piı          | ns N               | ote (1)             |                     |                     |                    |                    |                     |                     |

|------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|---------------------|---------------------|--------------------|--------------------|---------------------|---------------------|

| Device     | 44-<br>Pin<br>PLCC | 44-<br>Pin<br>PQFP | 44-<br>Pin<br>TQFP | 68-<br>Pin<br>PLCC | 84-<br>Pin<br>PLCC | 100-<br>Pin<br>PQFP | 100-<br>Pin<br>TQFP | 160-<br>Pin<br>PQFP | 160-<br>Pin<br>PGA | 192-<br>Pin<br>PGA | 208-<br>Pin<br>PQFP | 208-<br>Pin<br>RQFP |

| EPM7032    | 36                 | 36                 | 36                 |                    |                    |                     |                     |                     |                    |                    |                     |                     |

| EPM7032S   | 36                 |                    | 36                 |                    |                    |                     |                     |                     |                    |                    |                     |                     |

| EPM7064    | 36                 |                    | 36                 | 52                 | 68                 | 68                  |                     |                     |                    |                    |                     |                     |

| EPM7064S   | 36                 |                    | 36                 |                    | 68                 |                     | 68                  |                     |                    |                    |                     |                     |

| EPM7096    |                    |                    |                    | 52                 | 64                 | 76                  |                     |                     |                    |                    |                     |                     |

| EPM7128E   |                    |                    |                    |                    | 68                 | 84                  |                     | 100                 |                    |                    |                     |                     |

| EPM7128S   |                    |                    |                    |                    | 68                 | 84                  | 84 (2)              | 100                 |                    |                    |                     |                     |

| EPM7160E   |                    |                    |                    |                    | 64                 | 84                  |                     | 104                 |                    |                    |                     |                     |

| EPM7160S   |                    |                    |                    |                    | 64                 |                     | 84 (2)              | 104                 |                    |                    |                     |                     |

| EPM7192E   |                    |                    |                    |                    |                    |                     |                     | 124                 | 124                |                    |                     |                     |

| EPM7192S   |                    |                    |                    |                    |                    |                     |                     | 124                 |                    |                    |                     |                     |

| EPM7256E   |                    |                    |                    |                    |                    |                     |                     | 132 (2)             |                    | 164                |                     | 164                 |

| EPM7256S   |                    |                    |                    |                    |                    |                     |                     |                     |                    |                    | 164 (2)             | 164                 |

Notes:

When the JTAG interface in MAX 7000S devices is used for either boundary-scan testing or for ISP, four I/O pins become JTAG pins.

(2) Perform a complete thermal analysis before committing a design to this device package. For more information, see the *Operating Requirements for Altera Devices Data Sheet*.

MAX 7000 devices use CMOS EEPROM cells to implement logic functions. The user-configurable MAX 7000 architecture accommodates a variety of independent combinatorial and sequential logic functions. The devices can be reprogrammed for quick and efficient iterations during design development and debug cycles, and can be programmed and erased up to 100 times.

MAX 7000 devices contain from 32 to 256 macrocells that are combined into groups of 16 macrocells, called logic array blocks (LABs). Each macrocell has a programmable-AND/fixed-OR array and a configurable register with independently programmable clock, clock enable, clear, and preset functions. To build complex logic functions, each macrocell can be supplemented with both shareable expander product terms and highspeed parallel expander product terms to provide up to 32 product terms per macrocell.

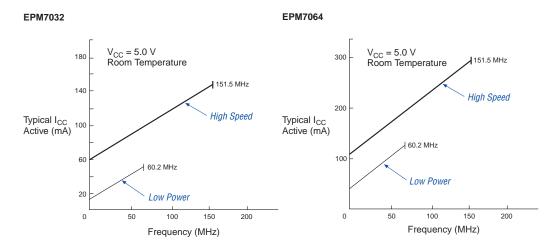

The MAX 7000 family provides programmable speed/power optimization. Speed-critical portions of a design can run at high speed/full power, while the remaining portions run at reduced speed/low power. This speed/power optimization feature enables the designer to configure one or more macrocells to operate at 50% or lower power while adding only a nominal timing delay. MAX 7000E and MAX 7000S devices also provide an option that reduces the slew rate of the output buffers, minimizing noise transients when non-speed-critical signals are switching. The output drivers of all MAX 7000 devices (except 44-pin devices) can be set for either 3.3-V or 5.0-V operation, allowing MAX 7000 devices to be used in mixed-voltage systems.

The MAX 7000 family is supported by Altera development systems, which are integrated packages that offer schematic, text—including VHDL, Verilog HDL, and the Altera Hardware Description Language (AHDL)— and waveform design entry, compilation and logic synthesis, simulation and timing analysis, and device programming. The software provides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX-workstation-based EDA tools. The software runs on Windows-based PCs, as well as Sun SPARCstation, and HP 9000 Series 700/800 workstations.

-

For more information on development tools, see the MAX+PLUS II Programmable Logic Development System & Software Data Sheet and the Quartus Programmable Logic Development System & Software Data Sheet.

# Functional Description

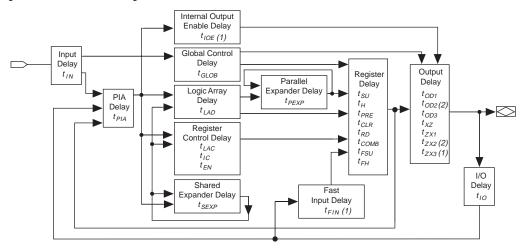

The MAX 7000 architecture includes the following elements:

- Logic array blocks

- Macrocells

- Expander product terms (shareable and parallel)

- Programmable interconnect array

- I/O control blocks

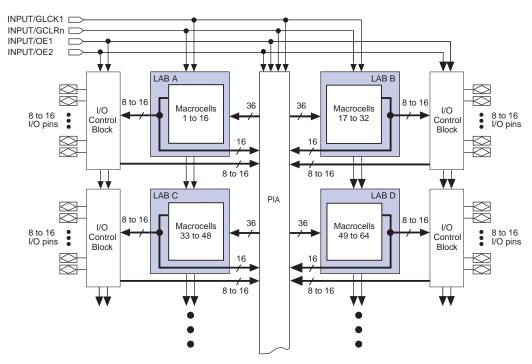

The MAX 7000 architecture includes four dedicated inputs that can be used as general-purpose inputs or as high-speed, global control signals (clock, clear, and two output enable signals) for each macrocell and I/O pin. Figure 1 shows the architecture of EPM7032, EPM7064, and EPM7096 devices.

Figure 1. EPM7032, EPM7064 & EPM7096 Device Block Diagram

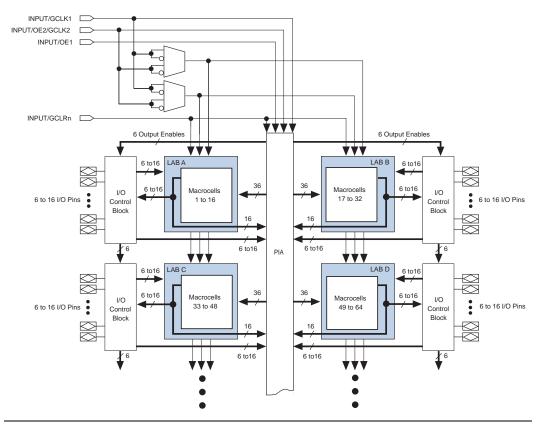

Figure 2 shows the architecture of MAX 7000E and MAX 7000S devices.

Figure 2. MAX 7000E & MAX 7000S Device Block Diagram

## **Logic Array Blocks**

The MAX 7000 device architecture is based on the linking of highperformance, flexible, logic array modules called logic array blocks (LABs). LABs consist of 16-macrocell arrays, as shown in Figures 1 and 2. Multiple LABs are linked together via the programmable interconnect array (PIA), a global bus that is fed by all dedicated inputs, I/O pins, and macrocells. Each LAB is fed by the following signals:

- **3**6 signals from the PIA that are used for general logic inputs

- Global controls that are used for secondary register functions

- Direct input paths from I/O pins to the registers that are used for fast setup times for MAX 7000E and MAX 7000S devices

#### Macrocells

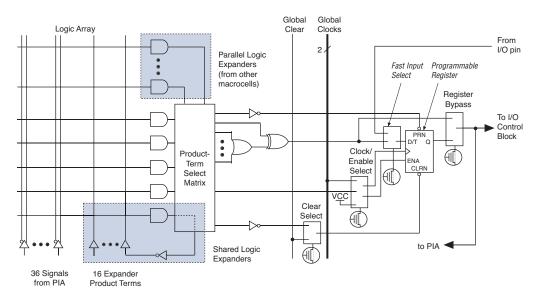

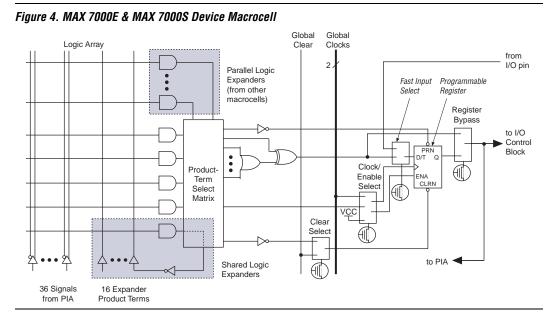

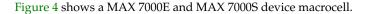

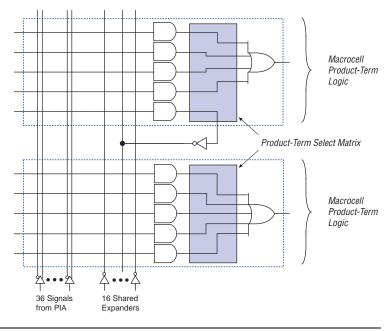

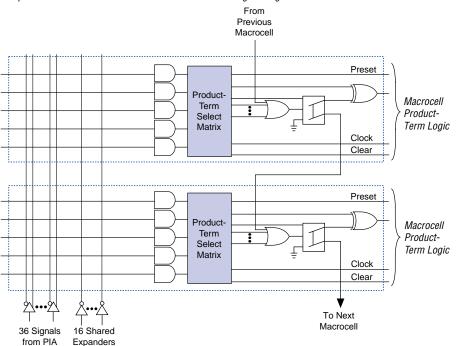

The MAX 7000 macrocell can be individually configured for either sequential or combinatorial logic operation. The macrocell consists of three functional blocks: the logic array, the product-term select matrix, and the programmable register. The macrocell of EPM7032, EPM7064, and EPM7096 devices is shown in Figure 3.

Figure 3. EPM7032, EPM7064 & EPM7096 Device Macrocell

Combinatorial logic is implemented in the logic array, which provides five product terms per macrocell. The product-term select matrix allocates these product terms for use as either primary logic inputs (to the OR and XOR gates) to implement combinatorial functions, or as secondary inputs to the macrocell's register clear, preset, clock, and clock enable control functions. Two kinds of expander product terms ("expanders") are available to supplement macrocell logic resources:

- Shareable expanders, which are inverted product terms that are fed back into the logic array

- Parallel expanders, which are product terms borrowed from adjacent macrocells

The Altera development system automatically optimizes product-term allocation according to the logic requirements of the design.

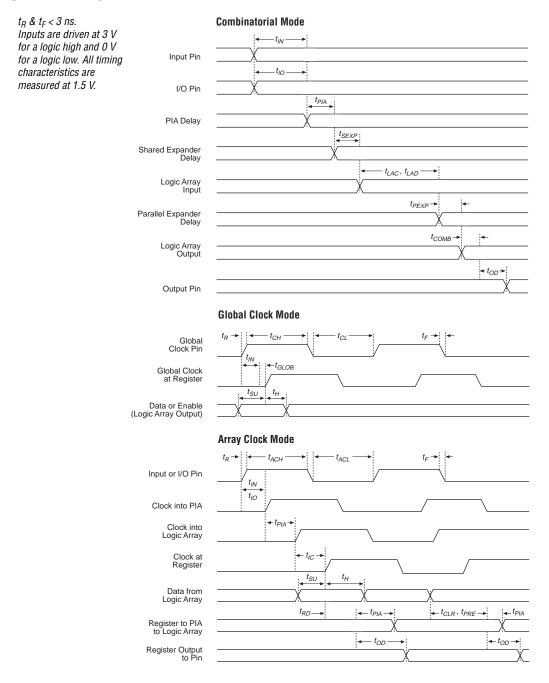

For registered functions, each macrocell flipflop can be individually programmed to implement D, T, JK, or SR operation with programmable clock control. The flipflop can be bypassed for combinatorial operation. During design entry, the designer specifies the desired flipflop type; the Altera development software then selects the most efficient flipflop operation for each registered function to optimize resource utilization. Each programmable register can be clocked in three different modes:

- By a global clock signal. This mode achieves the fastest clock-tooutput performance.

- By a global clock signal and enabled by an active-high clock enable. This mode provides an enable on each flipflop while still achieving the fast clock-to-output performance of the global clock.

- By an array clock implemented with a product term. In this mode, the flipflop can be clocked by signals from buried macrocells or I/O pins.

In EPM7032, EPM7064, and EPM7096 devices, the global clock signal is available from a dedicated clock pin, GCLK1, as shown in Figure 1. In MAX 7000E and MAX 7000S devices, two global clock signals are available. As shown in Figure 2, these global clock signals can be the true or the complement of either of the global clock pins, GCLK1 or GCLK2.

Each register also supports asynchronous preset and clear functions. As shown in Figures 3 and 4, the product-term select matrix allocates product terms to control these operations. Although the product-term-driven preset and clear of the register are active high, active-low control can be obtained by inverting the signal within the logic array. In addition, each register clear function can be individually driven by the active-low dedicated global clear pin (GCLRn). Upon power-up, each register in the device will be set to a low state.

All MAX 7000E and MAX 7000S I/O pins have a fast input path to a macrocell register. This dedicated path allows a signal to bypass the PIA and combinatorial logic and be driven to an input D flipflop with an extremely fast (2.5 ns) input setup time.

## **Expander Product Terms**

Although most logic functions can be implemented with the five product terms available in each macrocell, the more complex logic functions require additional product terms. Another macrocell can be used to supply the required logic resources; however, the MAX 7000 architecture also allows both shareable and parallel expander product terms ("expanders") that provide additional product terms directly to any macrocell in the same LAB. These expanders help ensure that logic is synthesized with the fewest possible logic resources to obtain the fastest possible speed.

#### Shareable Expanders

Each LAB has 16 shareable expanders that can be viewed as a pool of uncommitted single product terms (one from each macrocell) with inverted outputs that feed back into the logic array. Each shareable expander can be used and shared by any or all macrocells in the LAB to build complex logic functions. A small delay ( $t_{SEXP}$ ) is incurred when shareable expanders are used. Figure 5 shows how shareable expanders can feed multiple macrocells.

#### Figure 5. Shareable Expanders

Shareable expanders can be shared by any or all macrocells in an LAB.

### Parallel Expanders

Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow up to 20 product terms to directly feed the macrocell OR logic, with five product terms provided by the macrocell and 15 parallel expanders provided by neighboring macrocells in the LAB. The compiler can allocate up to three sets of up to five parallel expanders automatically to the macrocells that require additional product terms. Each set of five parallel expanders incurs a small, incremental timing delay ( $t_{PEXP}$ ). For example, if a macrocell requires 14 product terms, the Compiler uses the five dedicated product terms within the macrocell and allocates two sets of parallel expanders; the first set includes five product terms and the second set includes four product terms, increasing the total delay by  $2 \times t_{PEXP}$ .

Two groups of 8 macrocells within each LAB (e.g., macrocells 1 through 8 and 9 through 16) form two chains to lend or borrow parallel expanders. A macrocell borrows parallel expanders from lowernumbered macrocells. For example, macrocell 8 can borrow parallel expanders from macrocell 7, from macrocells 7 and 6, or from macrocells 7, 6, and 5. Within each group of 8, the lowest-numbered macrocell can only lend parallel expanders and the highest-numbered macrocell can only borrow them. Figure 6 shows how parallel expanders can be borrowed from a neighboring macrocell.

#### Figure 6. Parallel Expanders

Unused product terms in a macrocell can be allocated to a neighboring macrocell.

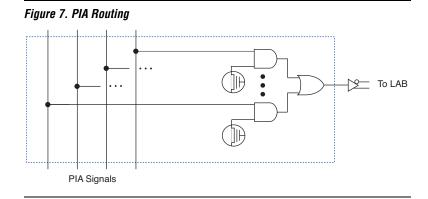

### Programmable Interconnect Array

Logic is routed between LABs via the programmable interconnect array (PIA). This global bus is a programmable path that connects any signal source to any destination on the device. All MAX 7000 dedicated inputs, I/O pins, and macrocell outputs feed the PIA, which makes the signals available throughout the entire device. Only the signals required by each LAB are actually routed from the PIA into the LAB. Figure 7 shows how the PIA signals are routed into the LAB. An EEPROM cell controls one input to a 2-input AND gate, which selects a PIA signal to drive into the LAB.

While the routing delays of channel-based routing schemes in masked or FPGAs are cumulative, variable, and path-dependent, the MAX 7000 PIA has a fixed delay. The PIA thus eliminates skew between signals and makes timing performance easy to predict.

## I/O Control Blocks

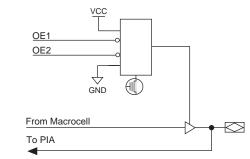

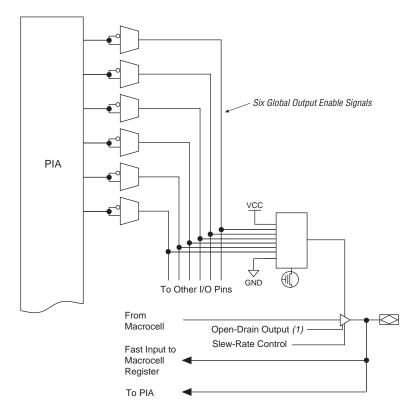

The I/O control block allows each I/O pin to be individually configured for input, output, or bidirectional operation. All I/O pins have a tri-state buffer that is individually controlled by one of the global output enable signals or directly connected to ground or  $V_{CC}$ . Figure 8 shows the I/O control block for the MAX 7000 family. The I/O control block of EPM7032, EPM7064, and EPM7096 devices has two global output enable signals that are driven by two dedicated active-low output enable pins (OE1 and OE2). The I/O control block of MAX 7000E and MAX 7000S devices has six global output enable signals that are driven by the true or complement of two output enable signals, a subset of the I/O pins, or a subset of the I/O macrocells.

## Figure 8. I/O Control Block of MAX 7000 Devices

#### EPM7032, EPM7064 & EPM7096 Devices

#### Note:

(1) The open-drain output option is available only in MAX 7000S devices.

When the tri-state buffer control is connected to ground, the output is tri-stated (high impedance) and the I/O pin can be used as a dedicated input. When the tri-state buffer control is connected to  $V_{CC}$ , the output is enabled.

The MAX 7000 architecture provides dual I/O feedback, in which macrocell and pin feedbacks are independent. When an I/O pin is configured as an input, the associated macrocell can be used for buried logic.

# In-System Programmability (ISP)

MAX 7000S devices are in-system programmable via an industry-standard 4-pin Joint Test Action Group (JTAG) interface (IEEE Std. 1149.1-1990). ISP allows quick, efficient iterations during design development and debugging cycles. The MAX 7000S architecture internally generates the high programming voltage required to program EEPROM cells, allowing in-system programming with only a single 5.0 V power supply. During in-system programming, the I/O pins are tri-stated and pulled-up to eliminate board conflicts. The pull-up value is nominally 50 k<sup>3</sup>4.

ISP simplifies the manufacturing flow by allowing devices to be mounted on a printed circuit board with standard in-circuit test equipment before they are programmed. MAX 7000S devices can be programmed by downloading the information via in-circuit testers (ICT), embedded processors, or the Altera MasterBlaster, ByteBlasterMV, ByteBlaster, BitBlaster download cables. (The ByteBlaster cable is obsolete and is replaced by the ByteBlasterMV cable, which can program and configure 2.5-V, 3.3-V, and 5.0-V devices.) Programming the devices after they are placed on the board eliminates lead damage on high-pin-count packages (e.g., QFP packages) due to device handling and allows devices to be reprogrammed after a system has already shipped to the field. For example, product upgrades can be performed in the field via software or modem.

In-system programming can be accomplished with either an adaptive or constant algorithm. An adaptive algorithm reads information from the unit and adapts subsequent programming steps to achieve the fastest possible programming time for that unit. Because some in-circuit testers cannot support an adaptive algorithm, Altera offers devices tested with a constant algorithm. Devices tested to the constant algorithm have an "F" suffix in the ordering code.

The Jam<sup>™</sup> Standard Test and Programming Language (STAPL) can be used to program MAX 7000S devices with in-circuit testers, PCs, or embedded processor.

For more information on using the Jam language, refer to AN 122: Using Jam STAPL for ISP & ICR via an Embedded Processor.

The ISP circuitry in MAX 7000S devices is compatible with IEEE Std. 1532 specification. The IEEE Std. 1532 is a standard developed to allow concurrent ISP between multiple PLD vendors.

## **Programming Sequence**

During in-system programming, instructions, addresses, and data are shifted into the MAX 7000S device through the TDI input pin. Data is shifted out through the TDO output pin and compared against the expected data.

Programming a pattern into the device requires the following six ISP stages. A stand-alone verification of a programmed pattern involves only stages 1, 2, 5, and 6.

- 1. *Enter ISP*. The enter ISP stage ensures that the I/O pins transition smoothly from user mode to ISP mode. The enter ISP stage requires 1 ms.

- 2. *Check ID*. Before any program or verify process, the silicon ID is checked. The time required to read this silicon ID is relatively small compared to the overall programming time.

- 3. *Bulk Erase.* Erasing the device in-system involves shifting in the instructions to erase the device and applying one erase pulse of 100 ms.

- 4. *Program*. Programming the device in-system involves shifting in the address and data and then applying the programming pulse to program the EEPROM cells. This process is repeated for each EEPROM address.

- 5. *Verify.* Verifying an Altera device in-system involves shifting in addresses, applying the read pulse to verify the EEPROM cells, and shifting out the data for comparison. This process is repeated for each EEPROM address.

- 6. *Exit ISP*. An exit ISP stage ensures that the I/O pins transition smoothly from ISP mode to user mode. The exit ISP stage requires 1 ms.

## **Programming Times**

The time required to implement each of the six programming stages can be broken into the following two elements:

- A pulse time to erase, program, or read the EEPROM cells.

- A shifting time based on the test clock (TCK) frequency and the number of TCK cycles to shift instructions, address, and data into the device.

By combining the pulse and shift times for each of the programming stages, the program or verify time can be derived as a function of the TCK frequency, the number of devices, and specific target device(s). Because different ISP-capable devices have a different number of EEPROM cells, both the total fixed and total variable times are unique for a single device.

### Programming a Single MAX 7000S Device

The time required to program a single MAX 7000S device in-system can be calculated from the following formula:

$$t_{PROG} = t_{PPULSE} + \frac{Cycle_{PTCK}}{f_{TCK}}$$

where:  $t_{PROG}$  = Programming time

$t_{PPULSE}$  = Sum of the fixed times to erase, program, and

verify the EEPROM cells

$Cycle_{PTCK}$  = Number of TCK cycles to program a device

$f_{TCK}$  = TCK frequency

The ISP times for a stand-alone verification of a single MAX 7000S device can be calculated from the following formula:

$$t_{VER} = t_{VPULSE} + \frac{Cycle_{VTCK}}{f_{TCK}}$$

where:  $t_{VER}$  = Verify time

$t_{VPULSE}$  = Sum of the fixed times to verify the EEPROM cells

$Cycle_{VTCK}$  = Number of TCK cycles to verify a device

The programming times described in Tables 6 through 8 are associated

| Device   | Progra                  | mming                 | Stand-Alone             | Stand-Alone Verification |  |  |

|----------|-------------------------|-----------------------|-------------------------|--------------------------|--|--|

|          | t <sub>PPULSE</sub> (s) | Cycle <sub>PTCK</sub> | t <sub>VPULSE</sub> (s) | Cycle <sub>VTCK</sub>    |  |  |

| EPM7032S | 4.02                    | 342,000               | 0.03                    | 200,000                  |  |  |

| EPM7064S | 4.50                    | 504,000               | 0.03                    | 308,000                  |  |  |

| EPM7128S | 5.11                    | 832,000               | 0.03                    | 528,000                  |  |  |

| EPM7160S | 5.35                    | 1,001,000             | 0.03                    | 640,000                  |  |  |

| EPM7192S | 5.71                    | 1,192,000             | 0.03                    | 764,000                  |  |  |

| EPM7256S | 6.43                    | 1,603,000             | 0.03                    | 1,024,000                |  |  |

with the worst-case method using the enhanced ISP algorithm.

Tables 7 and 8 show the in-system programming and stand alone verification times for several common test clock frequencies.

| Device   |        | f <sub>TCK</sub> |       |       |         |         |         |        |   |

|----------|--------|------------------|-------|-------|---------|---------|---------|--------|---|

|          | 10 MHz | 5 MHz            | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz | ] |

| EPM7032S | 4.06   | 4.09             | 4.19  | 4.36  | 4.71    | 5.73    | 7.44    | 10.86  | s |

| EPM7064S | 4.55   | 4.60             | 4.76  | 5.01  | 5.51    | 7.02    | 9.54    | 14.58  | S |

| EPM7128S | 5.19   | 5.27             | 5.52  | 5.94  | 6.77    | 9.27    | 13.43   | 21.75  | S |

| EPM7160S | 5.45   | 5.55             | 5.85  | 6.35  | 7.35    | 10.35   | 15.36   | 25.37  | S |

| EPM7192S | 5.83   | 5.95             | 6.30  | 6.90  | 8.09    | 11.67   | 17.63   | 29.55  | S |

| EPM7256S | 6.59   | 6.75             | 7.23  | 8.03  | 9.64    | 14.45   | 22.46   | 38.49  | S |

Table 8. MAX 7000S Stand-Alone Verification Times for Different Test Clock Frequencies

|          | 1      |                  |       |       |         |         |         |        | 1     |

|----------|--------|------------------|-------|-------|---------|---------|---------|--------|-------|

| Device   |        | f <sub>TCK</sub> |       |       |         |         |         |        | Units |

|          | 10 MHz | 5 MHz            | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz |       |

| EPM7032S | 0.05   | 0.07             | 0.13  | 0.23  | 0.43    | 1.03    | 2.03    | 4.03   | S     |

| EPM7064S | 0.06   | 0.09             | 0.18  | 0.34  | 0.64    | 1.57    | 3.11    | 6.19   | S     |

| EPM7128S | 0.08   | 0.14             | 0.29  | 0.56  | 1.09    | 2.67    | 5.31    | 10.59  | S     |

| EPM7160S | 0.09   | 0.16             | 0.35  | 0.67  | 1.31    | 3.23    | 6.43    | 12.83  | S     |

| EPM7192S | 0.11   | 0.18             | 0.41  | 0.79  | 1.56    | 3.85    | 7.67    | 15.31  | S     |

| EPM7256S | 0.13   | 0.24             | 0.54  | 1.06  | 2.08    | 5.15    | 10.27   | 20.51  | S     |

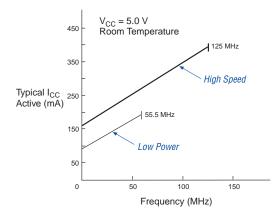

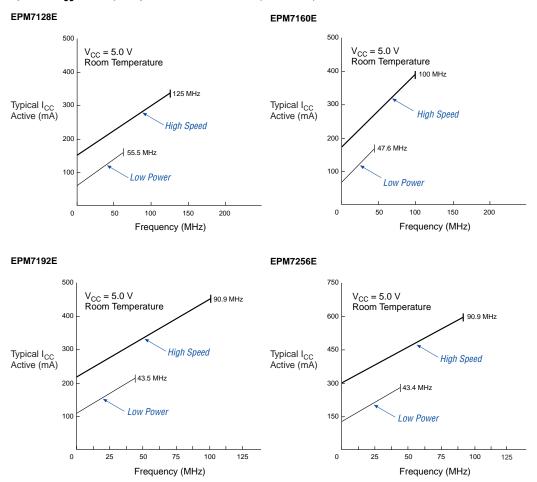

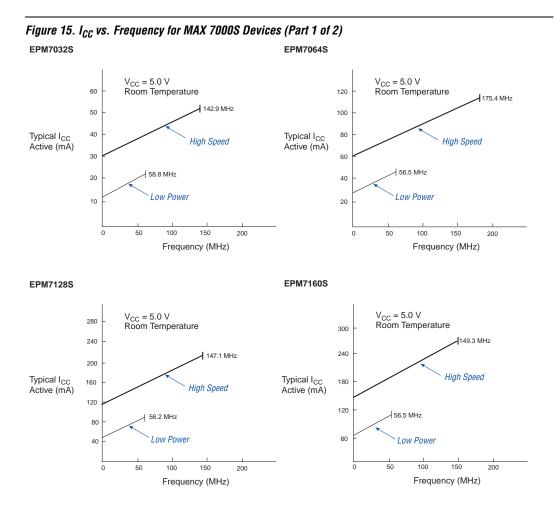

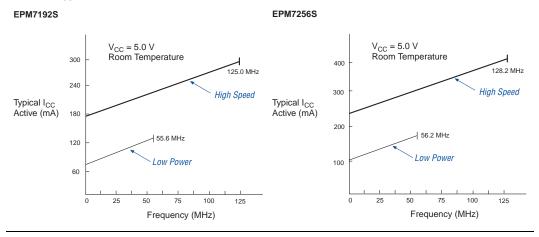

# Programmable Speed/Power Control

MAX 7000 devices offer a power-saving mode that supports low-power operation across user-defined signal paths or the entire device. This feature allows total power dissipation to be reduced by 50% or more, because most logic applications require only a small fraction of all gates to operate at maximum frequency.

The designer can program each individual macrocell in a MAX 7000 device for either high-speed (i.e., with the Turbo Bit<sup>TM</sup> option turned on) or low-power (i.e., with the Turbo Bit option turned off) operation. As a result, speed-critical paths in the design can run at high speed, while the remaining paths can operate at reduced power. Macrocells that run at low power incur a nominal timing delay adder ( $t_{LPA}$ ) for the  $t_{LAD}$ ,  $t_{LAC}$ ,  $t_{IC}$ ,  $t_{EN}$ , and  $t_{SEXP}$ ,  $\mathbf{t}_{ACL}$ , and  $\mathbf{t}_{CPPW}$  parameters.

Output Configuration

MAX 7000 device outputs can be programmed to meet a variety of system-level requirements.

# MultiVolt I/O Interface

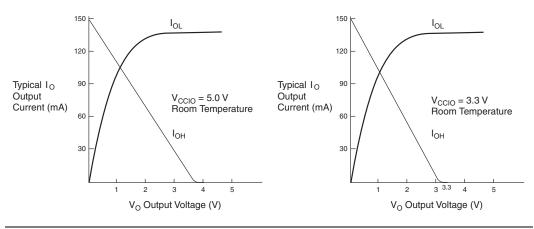

MAX 7000 devices—except 44-pin devices—support the MultiVolt I/O interface feature, which allows MAX 7000 devices to interface with systems that have differing supply voltages. The 5.0-V devices in all packages can be set for 3.3-V or 5.0-V I/O pin operation. These devices have one set of VCC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

The VCCINT pins must always be connected to a 5.0-V power supply. With a 5.0-V V<sub>CCINT</sub> level, input voltage thresholds are at TTL levels, and are therefore compatible with both 3.3-V and 5.0-V inputs.

The VCCIO pins can be connected to either a 3.3-V or a 5.0-V power supply, depending on the output requirements. When the VCCIO pins are connected to a 5.0-V supply, the output levels are compatible with 5.0-V systems. When V<sub>CCIO</sub> is connected to a 3.3-V supply, the output high is 3.3 V and is therefore compatible with 3.3-V or 5.0-V systems. Devices operating with V<sub>CCIO</sub> levels lower than 4.75 V incur a nominally greater timing delay of  $t_{OD2}$  instead of  $t_{OD1}$ .

# Open-Drain Output Option (MAX 7000S Devices Only)

MAX 7000S devices provide an optional open-drain (functionally equivalent to open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write enable signals) that can be asserted by any of several devices. It can also provide an additional wired-OR plane.

By using an external 5.0-V pull-up resistor, output pins on MAX 7000S devices can be set to meet 5.0-V CMOS input voltages. When  $V_{CCIO}$  is 3.3 V, setting the open drain option will turn off the output pull-up transistor, allowing the external pull-up resistor to pull the output high enough to meet 5.0-V CMOS input voltages. When  $V_{CCIO}$  is 5.0 V, setting the output drain option is not necessary because the pull-up transistor will already turn off when the pin exceeds approximately 3.8 V, allowing the external pull-up resistor to pull the output high enough to meet 5.0-V CMOS input voltages.

## **Slew-Rate Control**

The output buffer for each MAX 7000E and MAX 7000S I/O pin has an adjustable output slew rate that can be configured for low-noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal delay of 4 to 5 ns. In MAX 7000E devices, when the Turbo Bit is turned off, the slew rate is set for low noise performance. For MAX 7000S devices, each I/O pin has an individual EEPROM bit that controls the slew rate, allowing designers to specify the slew rate on a pin-by-pin basis.

MAX 7000 devices can be programmed on Windows-based PCs with the Altera Logic Programmer card, the Master Programming Unit (MPU), and the appropriate device adapter. The MPU performs a continuity check to ensure adequate electrical contact between the adapter and the device.

For more information, see the *Altera Programming Hardware Data Sheet*.

The Altera development system can use text- or waveform-format test vectors created with the Text Editor or Waveform Editor to test the programmed device. For added design verification, designers can perform functional testing to compare the functional behavior of a MAX 7000 device with the results of simulation. Moreover, Data I/O, BP Microsystems, and other programming hardware manufacturers also provide programming support for Altera devices.

For more information, see the Programming Hardware Manufacturers.

# Programming with External Hardware

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

MAX 7000 devices support JTAG BST circuitry as specified by IEEE Std. 1149.1-1990. Table 9 describes the JTAG instructions supported by the MAX 7000 family. The pin-out tables (see the Altera web site (http://www.altera.com) or the *Altera Digital Library* for pin-out information) show the location of the JTAG control pins for each device. If the JTAG interface is not required, the JTAG pins are available as user I/O pins.

| Table 9. MAX 7000 J | ITAG Instructions | 3                                                                                        |

|---------------------|-------------------|------------------------------------------------------------------------------------------|

| JTAG Instruction    | Devices           | Description                                                                              |

| SAMPLE/PRELOAD      | EPM7128S          | Allows a snapshot of signals at the device pins to be captured and                       |

|                     | EPM7160S          | examined during normal device operation, and permits an initial data                     |

|                     | EPM7192S          | pattern output at the device pins.                                                       |

|                     | EPM7256S          |                                                                                          |

| EXTEST              | EPM7128S          | Allows the external circuitry and board-level interconnections to be                     |

|                     | EPM7160S          | tested by forcing a test pattern at the output pins and capturing test                   |

|                     | EPM7192S          | results at the input pins.                                                               |

|                     | EPM7256S          |                                                                                          |

| BYPASS              | EPM7032S          | Places the 1-bit bypass register between the TDI and TDO pins, which                     |

|                     | EPM7064S          | allows the BST data to pass synchronously through a selected device                      |

|                     | EPM7128S          | to adjacent devices during normal device operation.                                      |

|                     | EPM7160S          |                                                                                          |

|                     | EPM7192S          |                                                                                          |

|                     | EPM7256S          |                                                                                          |

| IDCODE              | EPM7032S          | Selects the IDCODE register and places it between TDI and TDO,                           |

|                     | EPM7064S          | allowing the IDCODE to be serially shifted out of TDO.                                   |

|                     | EPM7128S          |                                                                                          |

|                     | EPM7160S          |                                                                                          |

|                     | EPM7192S          |                                                                                          |

|                     | EPM7256S          |                                                                                          |

| ISP Instructions    | EPM7032S          | These instructions are used when programming MAX 7000S devices                           |

|                     | EPM7064S          | via the JTAG ports with the MasterBlaster, ByteBlasterMV, BitBlaster                     |

|                     | EPM7128S          | download cable, or using a Jam File ( <b>.jam</b> ), Jam Byte-Code file ( <b>.jbc</b> ), |

|                     | EPM7160S          | or Serial Vector Format file (.svf) via an embedded processor or test                    |

|                     | EPM7192S          | equipment.                                                                               |

|                     | EPM7256S          |                                                                                          |

The instruction register length of MAX 7000S devices is 10 bits. Tables 10 and 11 show the boundary-scan register length and device IDCODE information for MAX 7000S devices.

| Table 10. MAX 7000S Boundary-Scan Register Length |                               |  |  |  |

|---------------------------------------------------|-------------------------------|--|--|--|

| Device                                            | Boundary-Scan Register Length |  |  |  |

| EPM7032S                                          | 1 (1)                         |  |  |  |

| EPM7064S                                          | 1 (1)                         |  |  |  |

| EPM7128S                                          | 288                           |  |  |  |

| EPM7160S                                          | 312                           |  |  |  |

| EPM7192S                                          | 360                           |  |  |  |

| EPM7256S                                          | 480                           |  |  |  |

Note:

This device does not support JTAG boundary-scan testing. Selecting either the EXTEST or SAMPLE/PRELOAD instruction will select the one-bit bypass register.

| Table 11. 32-Bit MAX 7000 Device IDCODE       Note (1) |                     |                       |                                      |                         |  |  |  |  |  |  |

|--------------------------------------------------------|---------------------|-----------------------|--------------------------------------|-------------------------|--|--|--|--|--|--|

| Device                                                 |                     | IDCODE (32 Bits)      |                                      |                         |  |  |  |  |  |  |

|                                                        | Version<br>(4 Bits) | Part Number (16 Bits) | Manufacturer's<br>Identity (11 Bits) | <b>1 (1 Bit)</b><br>(2) |  |  |  |  |  |  |

| EPM7032S                                               | 0000                | 0111 0000 0011 0010   | 00001101110                          | 1                       |  |  |  |  |  |  |

| EPM7064S                                               | 0000                | 0111 0000 0110 0100   | 00001101110                          | 1                       |  |  |  |  |  |  |

| EPM7128S                                               | 0000                | 0111 0001 0010 1000   | 00001101110                          | 1                       |  |  |  |  |  |  |

| EPM7160S                                               | 0000                | 0111 0001 0110 0000   | 00001101110                          | 1                       |  |  |  |  |  |  |

| EPM7192S                                               | 0000                | 0111 0001 1001 0010   | 00001101110                          | 1                       |  |  |  |  |  |  |

| EPM7256S                                               | 0000                | 0111 0010 0101 0110   | 00001101110                          | 1                       |  |  |  |  |  |  |

Notes:

(1) The most significant bit (MSB) is on the left.

(2) The least significant bit (LSB) for all JTAG IDCODEs is 1.

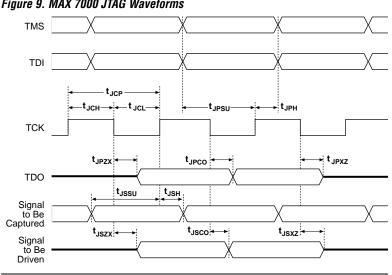

Figure 9 shows the timing requirements for the JTAG signals.

Table 12 shows the JTAG timing parameters and values for MAX 7000S devices.

| Table 12. JTAG Timing Parameters & Values for MAX 7000S Devices |                                                |     |     |      |  |  |  |  |

|-----------------------------------------------------------------|------------------------------------------------|-----|-----|------|--|--|--|--|

| Symbol                                                          | Parameter                                      | Min | Max | Unit |  |  |  |  |

| t <sub>JCP</sub>                                                | TCK clock period                               | 100 |     | ns   |  |  |  |  |

| t <sub>JCH</sub>                                                | TCK clock high time                            | 50  |     | ns   |  |  |  |  |

| t <sub>JCL</sub>                                                | TCK clock low time                             | 50  |     | ns   |  |  |  |  |

| t <sub>JPSU</sub>                                               | JTAG port setup time                           | 20  |     | ns   |  |  |  |  |

| t <sub>JPH</sub>                                                | JTAG port hold time                            | 45  |     | ns   |  |  |  |  |

| t <sub>JPCO</sub>                                               | JTAG port clock to output                      |     | 25  | ns   |  |  |  |  |

| t <sub>JPZX</sub>                                               | JTAG port high impedance to valid output       |     | 25  | ns   |  |  |  |  |

| t <sub>JPXZ</sub>                                               | JTAG port valid output to high impedance       |     | 25  | ns   |  |  |  |  |

| t <sub>JSSU</sub>                                               | Capture register setup time                    | 20  |     | ns   |  |  |  |  |

| t <sub>JSH</sub>                                                | Capture register hold time                     | 45  |     | ns   |  |  |  |  |

| t <sub>JSCO</sub>                                               | Update register clock to output                |     | 25  | ns   |  |  |  |  |

| t <sub>JSZX</sub>                                               | Update register high impedance to valid output |     | 25  | ns   |  |  |  |  |

| t <sub>JSXZ</sub>                                               | Update register valid output to high impedance |     | 25  | ns   |  |  |  |  |

For more information, see Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices).