ECN2102 / 2112 is a single chip row driver IC for electroluminescent (EL) display panel.

### Functions

- Low-voltage serial to high-voltage parallel converter

- \* 34 outputs of totem pole type

### Features

- \* Output terminal voltage up to 250V

- \* Source / Sink current 500mA

Fig. 1. OUTLINE OF FP-48 PACKAGE

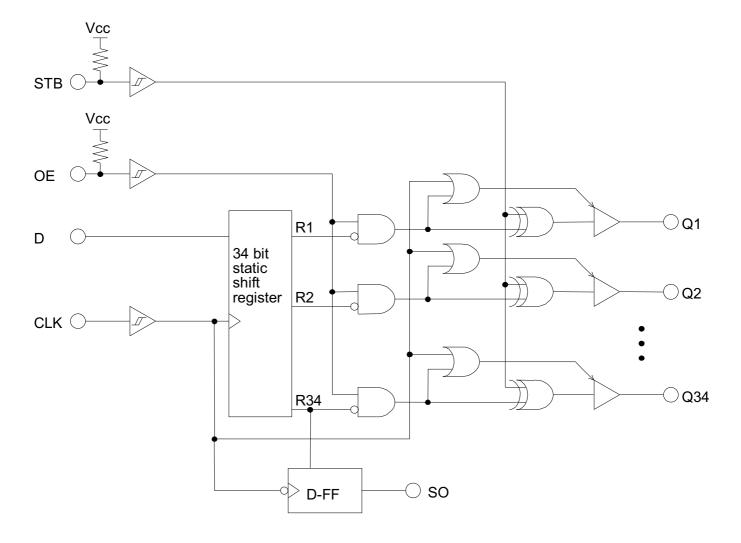

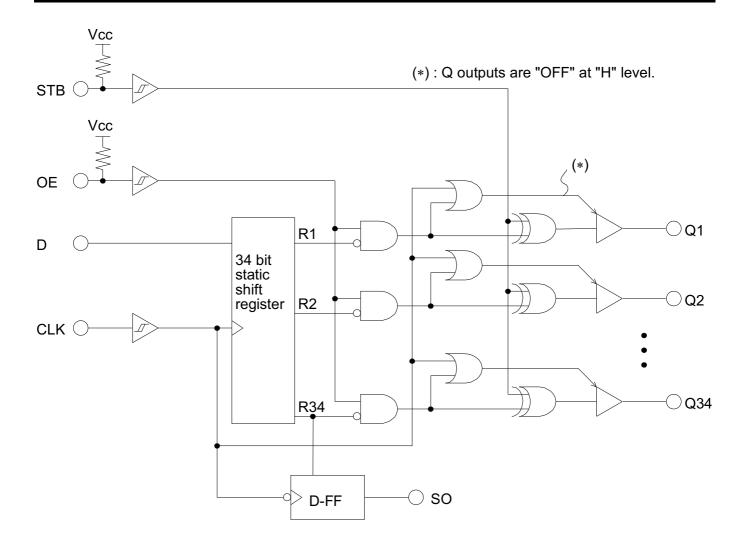

Function Block Diagram (Positive Logic)

#### 1. GENERAL

(1) TYPE ECN2102/ECN2112

(2) APPLICATION Row line driver for Electroluminecent (EL) display panel

(3) STRUCTURE Monolithic IC, processed Dielectric Isolation.

(4) PACKAGE FP-48 (Fig.1)

#### 2. MAXIMUM ALLOWABLE RATING (Ta=25°C)

| No | ITEMS                       | SYMBOLS | YMBOLS RATINGS |    | CONDITIONS          |  |

|----|-----------------------------|---------|----------------|----|---------------------|--|

| 1  | Supply Voltage (logic)      | Vcc     | -0.5 ~ +7.0    | V  | to GND terminal     |  |

| 2  | Input Voltage (logic)       | Vin     | -0.5 ~ Vcc+0.5 | V  | to GND terminal     |  |

| 3  | Vs - GND Voltage            | Vsg     | Vcc            | V  | to GND terminal     |  |

| 4  | Output Terminal Voltage     | VQ      | ±250           | V  | Between Vs,Vcc,GND, |  |

|    |                             |         |                |    | Input and Q output  |  |

| 5  | Allowable Power Dissipation | Рт      | 800            | mW |                     |  |

| 6  | Operating Temperature       | Тор     | -40 ~ +85      | °C |                     |  |

| 7  | Storage Temperature         | Tstg    | -55 ~ +150     | °C |                     |  |

#### 3. RECOMMENDED OPERATING CONDITIONS

| No | ITEMS                      | SYMBOLS | Min. | Тур. | Max. | UNITS | CONDITIONS   |

|----|----------------------------|---------|------|------|------|-------|--------------|

| 1  | Supply Voltage (logic)     | Vcc     | 5.0  | 5.5  | 6.0  | V     |              |

| 2  | Clock Frequency            | fclk    | ı    | _    | 250  | kHz   | Vcc= 5.5V    |

| 3  | Clock Pulse Width          | twclk   | 80   | _    |      | ns    | Vin= 0V/5.5V |

| 4  | Data Setup Time            | tsu     | 80   | _    | _    | ns    |              |

| 5  | Data Hold Time             | th      | 80   | _    | _    | ns    |              |

| 6  | Output Terminal Voltage    | VQ      | _    | ±230 | _    | V     | Vcc= 5.5V    |

| 7  | Peak Output Source Current | Нюн     | _    | _    | -500 | mA    | Note 1       |

| 8  | Peak Output Sink Current   | HIOL    | _    | _    | +500 | mA    | Note 1       |

Note1 : Conduction period  $\leq$  5  $\mu s$  per 1 IC

#### 4. ELECTRICAL CHARACTERISTICS (Unless otherwise specified, Ta= 25°C, Vcc= 5.5V, HVCC=230V)

| No | ITEMS                       | SYMBOLS | Min. | Тур. | Max. | UNITS | CONDITIONS                      |           |

|----|-----------------------------|---------|------|------|------|-------|---------------------------------|-----------|

| 1  | Output Voltage (logic)      | Vol     | 1    | _    | 0.1  | V     | IoL= 20μA                       |           |

|    |                             | Voн     | 5.4  | _    | _    | V     | Іон=-20μΑ                       |           |

| 2  | Output Current (logic)      | lol     | 1.0  | _    | _    | mA    | VoL= 0.8V                       |           |

|    |                             | Юн      | -1.0 | _    | _    | mA    | Volh 4.7V                       |           |

| 3  | Input Voltage (logic)       | VIL     | -    | _    | 1.0  | V     | D input                         |           |

|    |                             | ViH     | 3.5  | _    | _    | V     |                                 |           |

|    |                             | VTHL    | _    | _    | 0.4  | V     | CLK,STB input                   |           |

|    |                             | VTLH    | 4.5  | _    | _    | V     |                                 |           |

| 4  | Input Current (logic)       | lін     | _    | _    | 10   | μА    | Vin=5.5V all inpu               | t/1 input |

|    |                             | IIL     | _    | _    | -10  | μА    | Vin=0V D,CLK/1 input            |           |

|    |                             |         | _    | _    | -100 | μА    | Vin=0V STB/1 input              |           |

| 5  | Dissipation Current(logic)  | Istb    | _    | _    | 10   | μΑ    | No signal all input 5.5V,       |           |

|    |                             |         |      |      |      |       | all output Off                  |           |

|    |                             |         | _    | _    | 25   | mA    | No signal, 1ch source output On |           |

|    |                             |         | _    | _    | 5    | mA    | No signal, 1ch sink output On   |           |

| 6  | Output Voltage              | HVOL    | _    | _    | 3.0  | V     | HIOL=1mA                        | Q out-GND |

|    |                             |         | _    | _    | 6.0  | V     | HIOL=200mA                      | Q out-GND |

|    |                             | Нуон    | _    | _    | 4.0  | V     | Нюн=-1mA                        | Vs-Q out  |

|    |                             |         | _    | _    | 8.0  | V     | Нюн=-200mA                      | Vs-Q out  |

| 7  | Output SCR dv/dt capability | dv/dt1  | 200  | _    | _    | V/μs  | Vs~Q out,+dv/dt apply.Fig.6     |           |

|    |                             | dv/dt2  | 200  | -    | _    | V/μs  | Q out~GND,-dv/dt apply.Fig.7    |           |

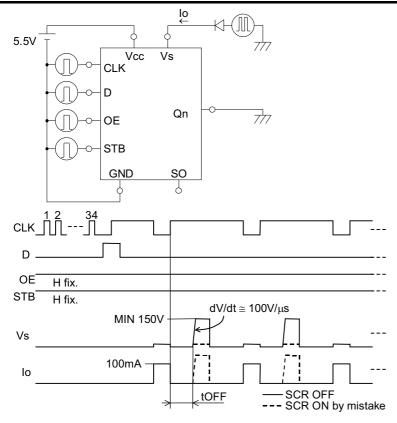

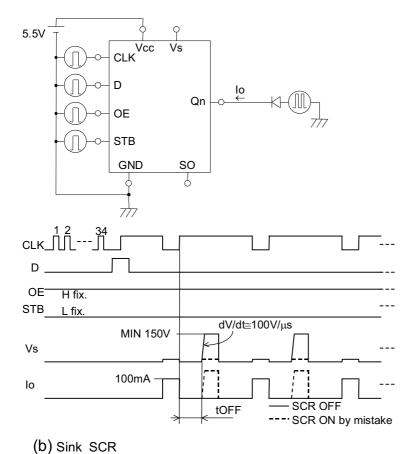

| 8  | Output SCR Off Period       | toff    | _    | _    | 6.0  | μS    | Source side                     | Fig.8     |

|    |                             |         | _    | _    | 7.0  | μS    | Sink side                       |           |

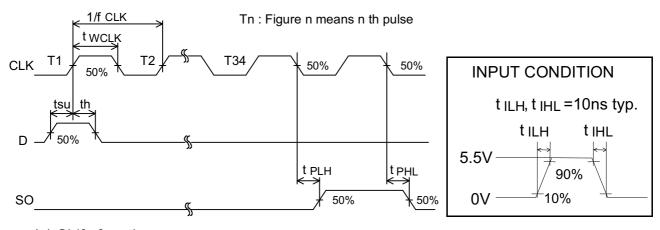

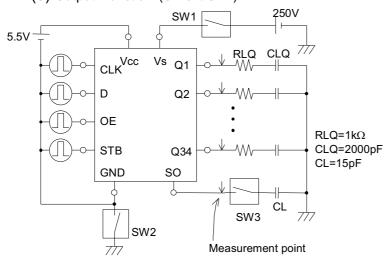

### 5. SWITCHING CHARACTERISTICS (Unless otherwise specified, Ta= 25°C, Vcc= 5.5V, Fig.5)

| No | ITEMS                     | SYMBOLS | Min. | Тур. | Max. | UNITS | CONDITIONS |

|----|---------------------------|---------|------|------|------|-------|------------|

| 1  | Output Delay Time (logic) | tPLH    | ı    | -    | 300  | ns    | CL=15pF    |

|    |                           | tPHL    | _    | _    | 300  | ns    |            |

| 2  | Output Delay Time         | tQLH    | _    | _    | 3    | μS    | RLQ=1kΩ    |

|    |                           | tQHL    | _    | _    | 3    | μS    | CLQ=2000pF |

Fig. 2. Function Block Diagram (Positive Logic)

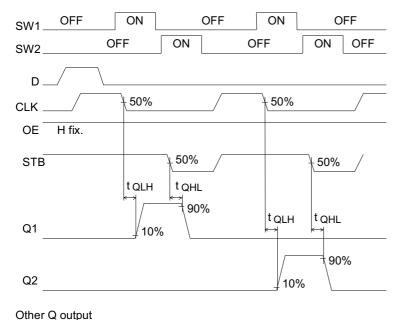

#### 6. FUNCTION TABLE

|           |         | CONTRO | OL INPUT   | - | SHIFT REGISTER | OUTF   | PUT     |  |

|-----------|---------|--------|------------|---|----------------|--------|---------|--|

|           | CLK     | D      | OE(*4) STB |   | Rn             | SO(*1) | Q       |  |

| SHIFT     | <b></b> | *      | Н          | * | shift          |        |         |  |

| OPERATION | no↑     | *      | Н          | * | keep           |        |         |  |

|           |         |        |            | Н | Н              |        | H (*2)  |  |

| OUTPUT    | L       | *      | Н          |   | L              | R34    | OFF     |  |

| OPERATION |         |        |            | L | Н              |        | L (*3)  |  |

|           |         |        |            |   | L              |        | OFF     |  |

|           | Н       | *      | H *        |   | *              |        | ALL OFF |  |

- (\*1) 34th data is pushed out as output at the state of down edge ↓ of clock signal.

- (\*2) When shift register is "H", source SCR of Q output is driven to ON.

- (\*3) When shift register is "H", sink SCR of Q output is driven to ON.

- (\*4) OE must be kept "H".

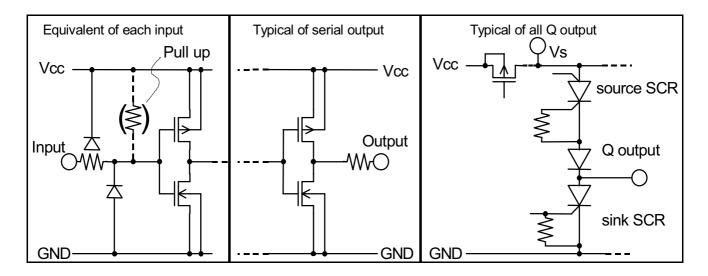

#### 7. INPUT / OUTPUT CIRCUIT

Fig. 3. Input / Output Circuit

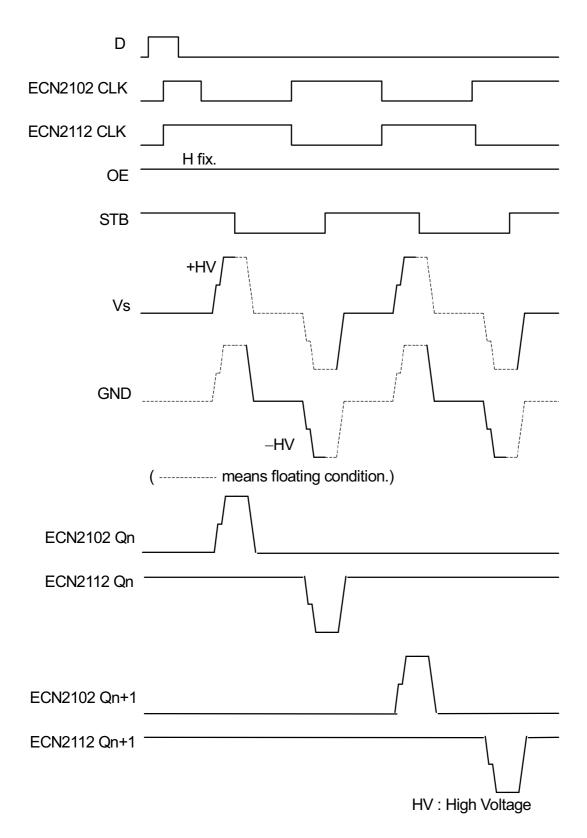

#### 8. EXAMPLE OF OPERATING TIMING CHART

Fig. 4. Example of Operating Timing Chart

#### 9. MEASUREMENT AND MEASUREMENT CIRCUIT

### (a) Shift function (SW1→OFF, SW2,3→ON)

#### (b) Output Function (SW3→OFF)

Fig. 5. Switching Characteristics Measurement Circuit

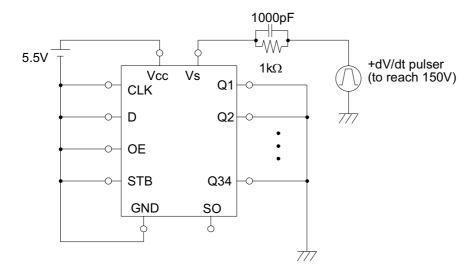

Fig. 6. Output SCR dV/dt capability (dV/dt1) Measurement Circuit

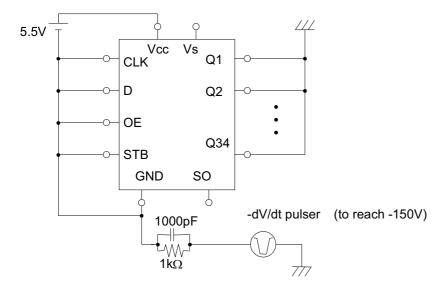

Fig. 7. Output SCR dV/dt capability (dV/dt2) Measurement Circuit

(a) Source SCR

Fig. 8. Output SCR tOFF Measurement

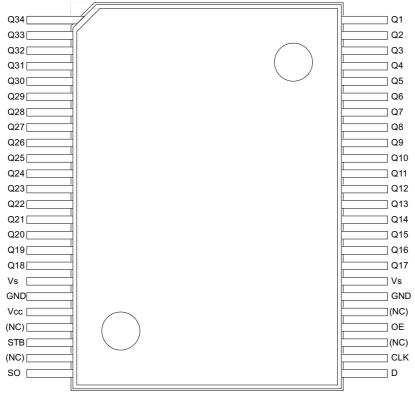

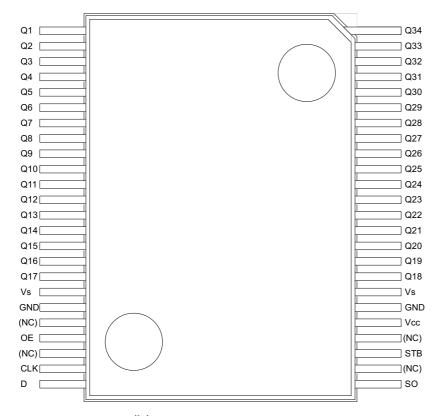

#### 10. PIN LOCATION

(a) ECN2102

(b) ECN2112

Fig. 9. Pin Location (Top view)

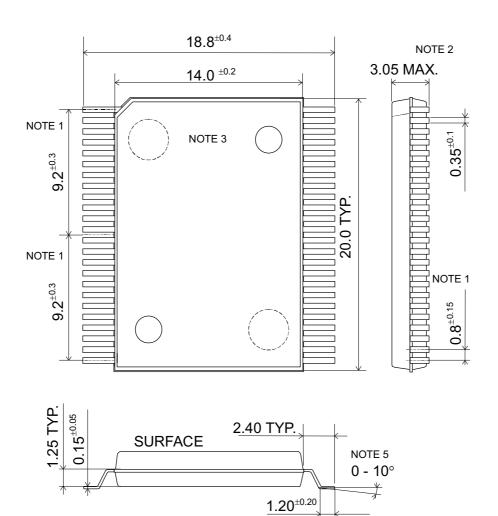

(Unit: mm)

### ECN2102/2112

#### 11. PACKAGE OUTLINE

(1) ECN2102

#### Notes.

- 1. THIS DIMENSION IS MEASURED AT ROOT OF LEAD. SPACING AT TIP OF LEAD IS MIN 0.2.

- 2. THIS DIMENSION INCLUDES A WARPAGE OF PACKAGE.

- 3. MARKING IS ON THE SURFACE OF PACKAGE, INCLUDING HITACHI MARK, TYPE NAME, LOT NUMBER, AND JAPAN MARK.

- 4. LEADS ARE SOLDER PLATED.

- 5. THIS IS THE BENDING ANGLE WITH HORIZONTAL PLANE.

Fig. 10. Package outline (ECN2102)

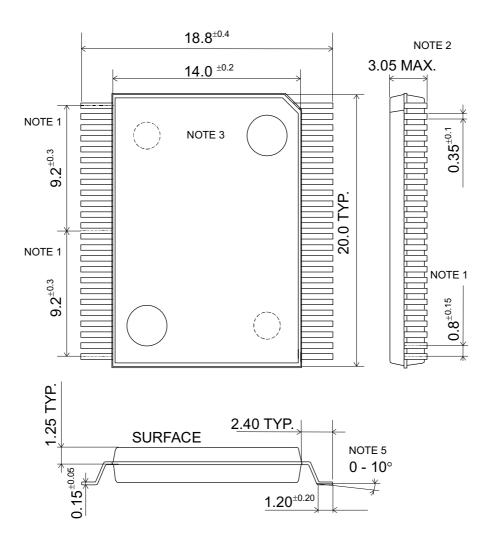

(Unit: mm)

### (2) ECN2112

#### Notes.

- 1. THIS DIMENSION IS MEASURED AT ROOT OF LEAD. SPACING AT TIP OF LEAD IS MIN 0.2.

- 2. THIS DIMENSION INCLUDES A WARPAGE OF PACKAGE.

- 3. MARKING IS ON THE SURFACE OF PACKAGE, INCLUDING HITACHI MARK, TYPE NAME, LOT NUMBER, AND JAPAN MARK.

- 4. LEADS ARE SOLDER PLATED.

- 5. THIS IS THE BENDING ANGLE WITH HORIZONTAL PLANE.

Fig. 11. Package outline (ECN2112)

### HITACHI POWER SEMICONDUCTORS

### **Notices**

- 1. The information given herein, including the specifications and dimensions, is subject to change without prior notice to improve product characteristics. Before ordering, purchasers are adviced to contact Hitachi sales department for the latest version of this data sheets.

- 2.Please be sure to read "Precautions for Safe Use and Notices" in the individual brochure before use

- 3.In cases where extremely high reliability is required(such as use in nuclear power control, aerospace and aviation, traffic equipment, life-support-related medical equipment, fuel control equipment and various kinds of safety equipment), safety should be ensured by using semiconductor devices that feature assured safety or by means of users' fail-safe precautions or other arrangement. Or consult Hitachi's sales department staff.

- 4.In no event shall Hitachi be liable for any damages that may result from an accident or any other cause during operation of the user's units according to this data sheets. Hitachi assumes no responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in this data sheets

- 5.In no event shall Hitachi be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.

- 6.No license is granted by this data sheets under any patents or other rights of any third party or Hitachi, Ltd.

- 7. This data sheets may not be reproduced or duplicated, in any form, in whole or in part, without the expressed written permission of Hitachi, Ltd.

- 8. The products (technologies) described in this data sheets are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety not are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.

- For inquiries relating to the products, please contact nearest overseas representatives which is located "Inquiry" portion on the top page of a home page.

Hitachi power semiconductor home page address http://www.hitachi.co.jp/pse