# Contents

| Page | Section | Title                                           |

|------|---------|-------------------------------------------------|

| 3    | 1.      | Introduction                                    |

| 3    | 1.1.    | General Information                             |

| 3    | 1.2.    | Environment                                     |

| 5    | 2.      | Specifications                                  |

| 5    | 2.1.    | Outline Dimensions                              |

| 5    | 2.2.    | Pin Connections                                 |

| 6    | 2.3.    | Pin Descriptions                                |

| 8    | 2.4.    | Pin Circuits                                    |

| 9    | 2.5.    | Electrical Characteristics                      |

| 9    | 2.5.1.  | Absolute Maximum Ratings                        |

| 9    | 2.5.2.  | Recommended Operating Conditions                |

| 11   | 2.5.3.  | Recommended Crystal Characteristics             |

| 12   | 2.5.4.  | Characteristics                                 |

| 15   | 2.5.5.  | DRAM Interface Characteristics                  |

| 17   | 2.5.6.  | Waveforms                                       |

| 20   | 2.5.7.  | Frequency Responses                             |

| 21   | 3.      | Functional Description                          |

| 21   | 3.1.    | Clock and Data Recovery                         |

| 21   | 3.1.1.  | The Code Converter                              |

| 21   | 3.1.2.  | The Video Clamping Circuit and the AGC Circuit  |

| 21   | 3.1.3.  | The Phase Comparator and the PLL Filter         |

| 21   | 3.1.4.  | The Data Slicer and the Synchronization Circuit |

| 21   | 3.2.    | Video Processing                                |

| 21   | 3.2.1.  | The Luminance Store                             |

| 22   | 3.2.2.  | The Luminance Interpolating Filter              |

| 22   | 3.2.3.  | The Contrast Multiplier                         |

| 22   | 3.2.4.  | The Chrominance Store                           |

| 22   | 3.2.5.  | The Line Interpolating Filter                   |

| 22   | 3.2.6.  | The Chrominance Interpolating filter            |

| 22   | 3.2.7.  | The Color Saturation Multiplier                 |

| 22   | 3.2.8.  | The Color Multiplier                            |

| 22   | 3.3.    | Sound/Data Processing                           |

| 23   | 3.3.1.  | The Golay and PT Byte Decoder                   |

| 23   | 3.3.2.  | The Address Comparator                          |

| 23   | 3.3.3.  | The Sound Decoder                               |

| 23   | 3.3.4.  | The Sound Multiplex                             |

| 24   | 3.3.5.  | The ΦA Audio Clock                              |

| 24   | 3.3.6.  | The Buffer for Packet 0                         |

| 25   | 4.      | The Three Serial Interfaces                     |

| 25   | 4.1.    | The S Bus Interface and the S Bus               |

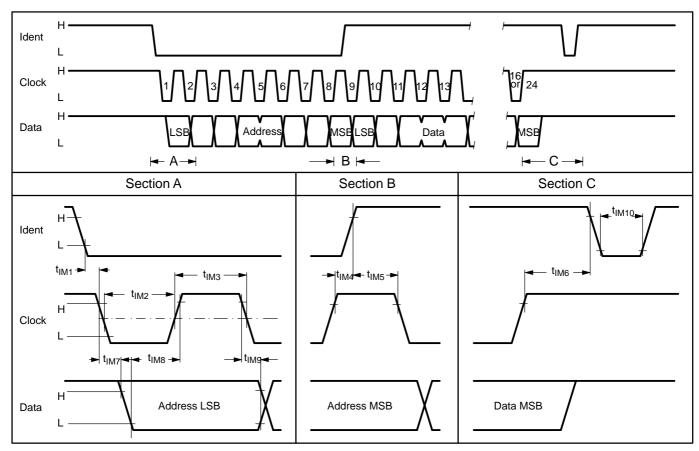

| 25   | 4.2.    | The IM Bus Interface and the IM Bus             |

| 25   | 4.2.1.  | The IM Bus                                      |

| 25   | 4.2.2.  | IM Bus Addresses and Instructions               |

| 25   | 4.3.    | The Burst Bus                                   |

| 26   | 4.3.1.  | Control and Status Registers                    |

# The DMA 2271, DMA 2280, and DMA 2281 C/D/D2-MAC Decoders

#### 1. Introduction

#### 1.1. General Information

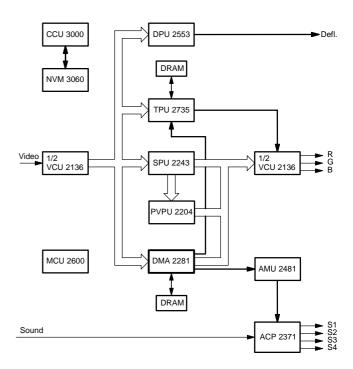

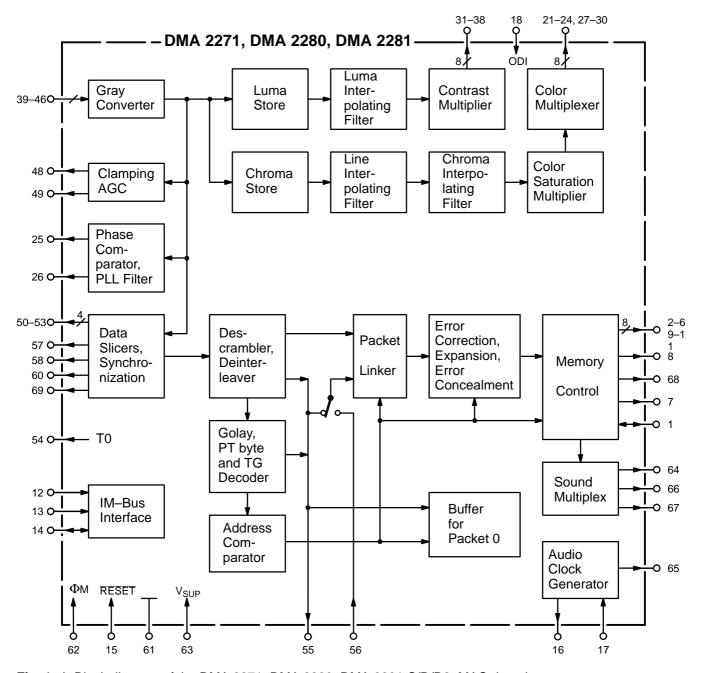

Digital real–time signal processor for processing C/D/D2–MAC video, sound, and data signals digitized by the VCU 2133 Video Codec in digital CTV receivers according to INTERMETALL's DIGIT 2000 system of or in analog CTV receivers or in stand–alone C/D/D2–MAC decoders (see Figs. 1–1 to 1–3).

In order to receive TV channels transmitted via satellite or cable network using the newly established C/D/D2–MAC standards instead of PAL or SECAM, decoders are required for decoding the TV video and sound signals. The DMA 2271, DMA 2280, and DMA 2281 are suitable for this purpose, in conjunction with the DIGIT 2000 digital TV system and also for stand–alone solutions.

The DMA 2271 is only able to decode D2–MAC/packet signals, in contrast to the DMA 2280 which decodes D–MAC/packet signals and the DMA 2281 which decodes D2, D or C–MAC/packet signals.

The DMA 2271, DMA 2280, and DMA 2281 are a programmable circuits, produced in CMOS technology and housed in a 68–pin PLCC package. These decoders contain on a single silicon chip the following functions (see Fig. 1–4):

- code converter

- circuitry for clamping, AGC and PLL

- chroma and luma store for expansion of the MAC signal

- chroma and luma interpolating filter

- contrast multiplier with limiter for the luminance signal

- color saturation multiplier with multiplexer

- duobinary decoder (data slicer)

- synchronization

- descrambler and de-interleaver

- packet linker

- packet 0 buffer

- sound decoder and sound multiplexer

- IM bus interface circuit for communicating with the CCU

#### 1.2. Environment

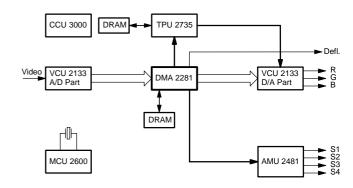

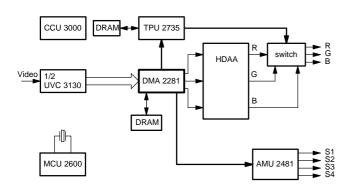

Fig. 1–1 shows the block diagram of a digital CTV receiver system DIGIT 2000, equipped with C/D/D2–MAC and Teletext, and suited for the PAL and SECAM standards. Stand–alone C/D/D2–MAC decoders are shown in Figs. 1–2 and 1–3. These two versions can either be integrated into analog CTV receivers, or can serve as stand–alone C/D/D2–MAC decoders.

**Fig. 1–1:** Block diagram for a multistandard CTV receiver according to the DIGIT 2000 system and equipped with D2–MAC

**Fig. 1–2:** Block diagram for a stand–alone C/D/D2–MAC decoder, equipped with the VCU 2133 Video Codec for A/D and D/A conversion (reduced chroma bandwidth)

**Fig. 1–3:** Block diagram for a stand–alone C/D/D2–MAC decoder, equipped with the UVC 3130 for A/D and HDAA or D/A conversion (full chroma bandwidth)

Fig. 1-4: Block diagram of the DMA 2271, DMA 2280, DMA 2281 C/D/D2-MAC decoders

# 2. Specifications

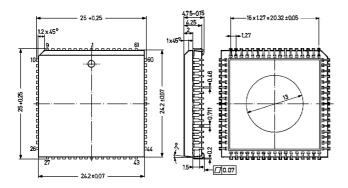

### 2.1. Outline Dimensions

**Fig. 2–1:** DMA 2271, DMA 2280, DMA 2281 in 68–pin PLCC package

Weight approx. 4.5 g, Dimensions in mm

### 2.2. Pin Connections

| Pin Nr. | Signal Name                | Symbol |

|---------|----------------------------|--------|

| 1       | RAM Data Input/Output      | RDAT   |

| 2       | RAM Address Output 0 (LSB) | RA0    |

| 3       | RAM Address Output 1       | RA1    |

| 4       | RAM Address Output 2       | RA2    |

| 5       | RAM Address Output 3       | RA3    |

| 6       | RAM Address Output 4       | RA4    |

| 7       | RAM Read/Write Output      | R/WQ   |

| 8       | Row Address Select Output  | RASQ   |

| 9       | RAM Address Output 5       | RA5    |

| 10      | RAM Address Output 6       | RA6    |

| 11      | RAM Address Output 7 (MSB) | RA7    |

| 12      | IM Bus Clock Input         | IMC    |

| 13      | IM Bus Ident Input         | IMI    |

| 14      | IM Bus Data Input/Output   | IMD    |

| 15      | Reset Input                | RESQ   |

| 16      | 18.432 MHz Output          | XTAL1  |

| 17      | 18.432 MHz Input           | XTAL2  |

| 18      | Output Disable Input       | ODI    |

| 19 | leave vacant                                    |      |

|----|-------------------------------------------------|------|

| 20 | leave vacant                                    |      |

| 21 | Chroma Output 7 (MSB)                           | CO7  |

| 22 | Chroma Output 6                                 | CO6  |

| 23 | Chroma Output 5                                 | CO5  |

| 24 | Chroma Output 4                                 | CO4  |

| 25 | PLL Tuning Data Output                          | PLLD |

| 26 | PLL Tuning Clock Output                         | PLLC |

| 27 | Chroma Output 3                                 | CO3  |

| 28 | Chroma Output 2                                 | CO2  |

| 29 | Chroma Output 1                                 | CO1  |

| 30 | Chroma Output 0 (LSB)                           | CO0  |

| 31 | Luma Output 0                                   | LO0  |

| 32 | Luma Output 1                                   | LO1  |

| 33 | Luma Output 2                                   | LO2  |

| 34 | Luma Output 3                                   | LO3  |

| 35 | Luma Output 4                                   | LO4  |

| 36 | Luma Output 5                                   | LO5  |

| 37 | Luma Output 6                                   | LO6  |

| 38 | Luma Output 7 (MSB)                             | LO7  |

| 39 | Baseband Input 7 (MSB)                          | BI7  |

| 40 | Baseband Input 6                                | BI6  |

| 41 | Baseband Input 5                                | BI5  |

| 42 | Baseband Input 4                                | BI4  |

| 43 | Baseband Input 3                                | BI3  |

| 44 | Baseband Input 2                                | BI2  |

| 45 | Baseband Input 1                                | BI1  |

| 46 | Baseband Input 0 (LSB)                          | BI0  |

| 47 | leave vacant                                    |      |

| 48 | Clamping Output                                 | CLMP |

| 49 | AGC Output                                      | AGC  |

| 50 | Combined Output for Horizontal Blanking and Key | KEY  |

| Combined Output for Horizontal and Vertical Blanking | CBL                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Burst Window Output                             | DBW                                                                                                                                                                                                                                                                                                                                                          |

| Composite Sync Output                                | CSYNC                                                                                                                                                                                                                                                                                                                                                        |

| Test Input/Output                                    | ТО                                                                                                                                                                                                                                                                                                                                                           |

| Packet Data Output                                   | PDAT                                                                                                                                                                                                                                                                                                                                                         |

| Descrambled Packet Data Input                        | DPDAT                                                                                                                                                                                                                                                                                                                                                        |

| Teletext Sync Output                                 | TSYNC                                                                                                                                                                                                                                                                                                                                                        |

| Burst Sync Output                                    | BSYNC                                                                                                                                                                                                                                                                                                                                                        |

| Burst Data Input/Output                              | BDAT                                                                                                                                                                                                                                                                                                                                                         |

| Burst Clock Output                                   | BCLK                                                                                                                                                                                                                                                                                                                                                         |

| Ground                                               | GND                                                                                                                                                                                                                                                                                                                                                          |

| Main Clock Input                                     | MCLK                                                                                                                                                                                                                                                                                                                                                         |

| Supply Voltage                                       | V <sub>SUP</sub>                                                                                                                                                                                                                                                                                                                                             |

| Sound Bus Ident Output                               | SBI                                                                                                                                                                                                                                                                                                                                                          |

| Audio Clock Output                                   | ACLK                                                                                                                                                                                                                                                                                                                                                         |

| Sound Bus Data Output                                | SBD                                                                                                                                                                                                                                                                                                                                                          |

| Sound Bus Clock Output                               | SBC                                                                                                                                                                                                                                                                                                                                                          |

| Column Address Select Output                         | CASQ                                                                                                                                                                                                                                                                                                                                                         |

|                                                      | Data Burst Window Output Composite Sync Output Test Input/Output Packet Data Output Descrambled Packet Data Input Teletext Sync Output Burst Sync Output Burst Data Input/Output Burst Clock Output Ground Main Clock Input Supply Voltage Sound Bus Ident Output Audio Clock Output Sound Bus Data Output Sound Bus Clock Output Column Address Select Out- |

#### 2.3. Pin Descriptions

Pin 1 – RAM Data Input/Output RDAT (Fig. 2–7) serves as an output for writing data into the external RAM and as an input for reading data from the external RAM.

Pins 2 to 6 and 9 to 11 – RAM Address Outputs RA0 to RA7 (Fig. 2–10)

These pins are used for addressing the external RAM.

Pin 7 – RAM Read/Write Output R/WQ (Fig. 2–10) By means of this output the external RAM is switched to read or write mode.

Pin 8 – Row Address Select Output RASQ (Fig. 2–10) This pin supplies the Row Address Select signal to the external RAM.

Pins 12 to 14 – IM Bus Connection IMC, IMI,IMD (Figs. 2–2 and 2–6)

These pins connect the DMA 2271, DMA 2280 and DMA 2281 to the IM bus. Via the IM bus the DMA 2271, DMA 2280 and DMA 2281 communicate with the CCU 3000

Central Control unit. The data transferred via the IM bus are listed in tables 4–1 to 4–4.

Pin 15 – Reset Input RESQ (Fig. 2–5)

Pin 15 is used for hardware reset. Reset is actuated at Low level, at High level the DMA 2271, DMA 2280, and DMA 2281 are ready for operation.

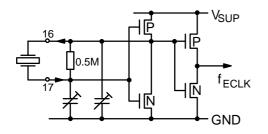

Pins 16 and 17 – XTAL 1 Output and XTAL 2 Input (Fig. 2–11)

These oscillator pins are used to connect an 18.432 MHz crystal, which determines the ACLK audio clock signal supplied by pin 65. Alternatively, an 18.432 MHz clock may be fed to pin 17.

Pin 18 - Output Disable Input ODI

This input serves for fast switchover of the luma and chroma outputs (L0 to L7 and C0 to C7) to high impedance, which is required if the TV receiver is equipped with Picture–in–picture. Low means outputs active, High means outputs are disabled.

Pin 19 – leave vacant

Pin 20 - leave vacant

Pins 21 to 24 and 27 to 30 – Chroma Outputs C7 to C0 (Fig. 2–8)

Via these pins, the DMA 2271, DMA 2280, and DMA 2281 deliver the digital chrominance signal (R–Y, B–Y) in multiplexed operation to the VCU 2133 Video Codec Unit, where it is converted to an analog signal.

Pin 25 – PLL Tuning Data Output PLLD (Fig. 2–8) This pin supplies the 12–bit data word containing the PLL tuning information from the PLL filter of the DMA 2271, DMA 2280, and DMA 2281. This information is needed by the voltage controlled oscillator (VCO) contained on the MCU 2600 Clock Generator IC and closes the PLL which determines the main clock signal.

Pin 26 – PLL Tuning Clock Output PLLC (Fig. 2–8) This pin supplies the data clock signal needed for the serial data transfer of the 12–bit PLL tuning information.

Pins 31 to 38 – Luma Outputs L0 to L7 (Fig. 2–8) Via these pins, the DMA 2271, DMA 2280 and DMA 2281 deliver the digital luminance signal to the VCU 2133 Video Codec Unit, where it is converted to an analog signal.

Pins 39 to 46 – Baseband Input BI7 to BI0 (Fig. 2–3) Via these inputs, the DMA 2271, DMA 2280, and DMA 2281 receive the digitized baseband signal from the VCU 2133 Video Codec.

Pin 47 - leave vacant

Pin 48 – Clamping Output CLMP (Fig. 2–9) This pin supplies a PDM (Pulse Density Modulated) signal for clamping the analog baseband signal at the input of the analog to digital converter. Pin 49 – AGC Output AGC (Fig. 2-9)

This tristate—controlled output allows automatic gain control (AGC) with a three—level signal. High level means that the input level of the baseband signal is too low, low level means that the input level of the baseband signal is too high. In the high impedance state the level of the baseband signal is in the proper range.

Pin 50 – Combined Output for Horizontal Blanking and Color KEY (Fig. 2–9)

This output is a tristate—controlled output. In conjunction with the input load represented by the VCU 2133 Video codec, the three level blanking and key is produced. High level means active line, high impedance state means horizontal blank and low level means color key.

Pin 51 – Combined Output for Horizontal Blanking and Vertical Blanking CBL (Fig. 2–9)

In conjunction with the input load represented by the VCU 2133 Video Codec, the three level combined blanking pulse is produced. High level means active line, high impedance means horizontal blanking and low level means vertical blanking.

Pin 52 – Data Burst Window DBW (Fig. 2–9)

This output supplies the data burst window signal which can be used to switch an external de-emphasis network. This signal is active high in line 625 and during the data burst in each line.

Pin 53 – Composite Sync Output CSYNC (Fig. 2–8) This output supplies a composite synchronization signal as it may be used by the DPU 25xx Deflection Processor or by other units which need a composite synchronization signal which is not contained in the MAC baseband signal.

Pin 54 – Test Input/Output T0 (Fig. 2–8) This pin is used for testing the DMA 2271, DMA 2280, and DMA 2281 during production.

Pin 55 – Packet Data Output PDAT (Fig. 2–10) PDAT is used to put out each received packet, de–interleaved, with Golay corrected header and with error–corrected BT Byte. This pin used to connect the DMA 2275, DMA 2285 or DMA 2286 Descrambler IC. Pin 56 – Descrambled Packet Data Input DPDAT (Fig. 2–2)

This pin is used in conjunction with PDAT, if conditional access signals must be descrambled, DPDAT receives the descrambled packet data from the DMA 2275, DMA 2285 or DMA 2286 Descrambler IC.

Pin 57 – Teletext Sync Output TSYNC (Fig. 2–9) This pin supplies a signal which marks the part of the VBI lines containing Teletext data.

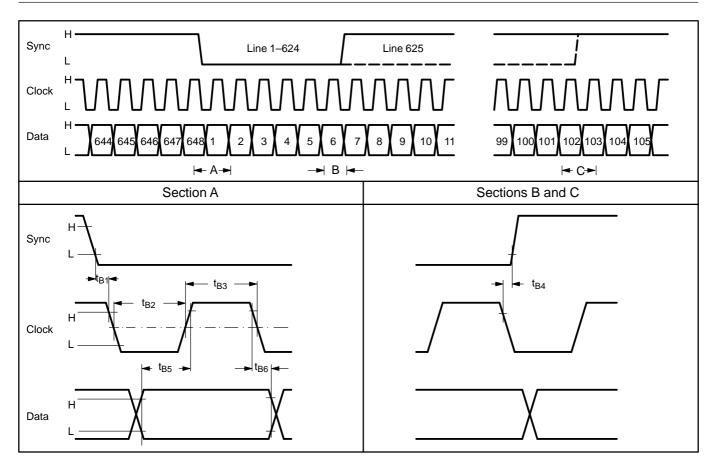

Pin 58 – Burst Sync Output BSYNC (Fig. 2–4) This connection supplies a synchronization signal for the Burst Data Output. The Sync Pulse marks the Line Synchronization Word LWS of each, and the Clock Run In CRI and Frame Sync Word FSW in line 625.

Pin 59 – Burst Data Output BDAT (Fig. 2–4) This output supplies the recovered an decoded duobinary data contained in a MAC signal. This signal may serve as an input signal for the TPU 27xx Teletext Processor or the DMA 2275, DMA 2285, DMA 2286 MAC Descrambler processor or for other purposes.

Pin 60 – Burst Clock Output BCLK (Fig. 2–9) This pin supplies the data clock signal required for the serial data transfer of the Burst Data signal. The frequency of this signal is equal MCLK or MCLK/2 controlled by parameter Data Rate Select DRS via IM Bus.

Pin 61 - Ground GND

Pin 62 – Main Clock Input MCLK (Fig. 2–4) By means of this input, the DMA 2271, DMA 2280 and DMA 2281 receive the required main clock signal from the MCU 2600 Clock Generator IC.

Pin 63 – Supply V<sub>SUP</sub>

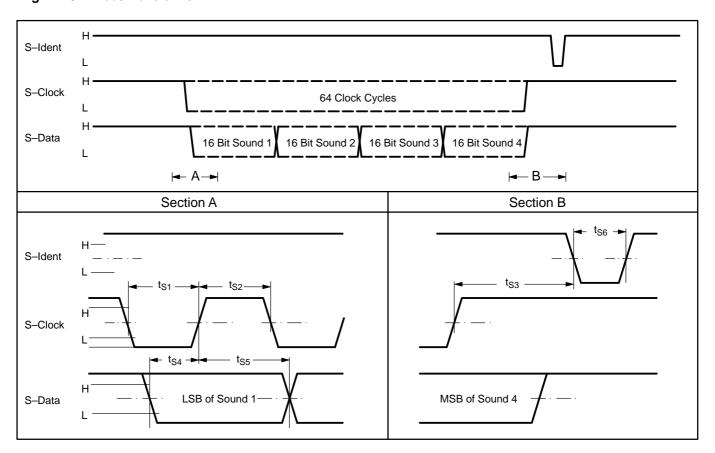

Pin 64, 66, and 67 – Sound Bus Ident SBI (Fig. 2–9) Data SBD and Clock SBC (Fig. 2–8) These pins supply the Clock, Data and Ident signals to the AMU 2481 Mixing Unit via the serial three–line Sound Bus.

Pin 65 – Audio Clock Output ACLK (Fig. NO TAG) This pin supplies the ACLK Audio Clock signal for the AMU 2481.

Pin 68 – Column Address Select CASQ (Fig. 2–10) This pin supplies the Column Address Select signal for the external RAM.

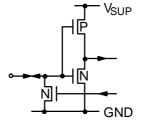

#### 2.4. Pin Circuits

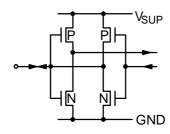

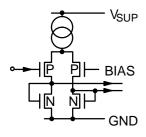

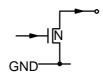

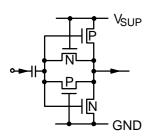

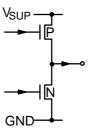

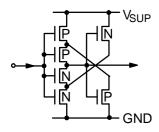

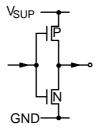

The following figures schematically show the circuitry at the various pins. The integrated protection structures are not shown. The letter "P" means P—channel, the letter "N" N—channel.

Fig. 2–6: Input/Output Pin 14

Fig. 2–2: Input Pins 12, 13, 18 and 56

Fig. 2–7: Input/Output Pin 1

Fig. 2–3: Input Pins 39 to 46

$V_{\text{SUP}}$

Fig. 2–8: Output Pins 21 to 38, 48, 52 to 54, 66 and 67

Fig. 2–4: Input Pin 62

**Fig. 2–9:** Output Pins 48 to 52, 57 to 60 and 64

Fig. 2–5: Input Pin 15

**Fig. 2–10:** Output Pins 2 to 11, 55 and 68

Fig. 2–12: Output Pin 65

Fig. 2–11: Crystal Oscillator Pins 16 and 17

### 2.5. Electrical Characteristics

All voltages are referred to ground.

### 2.5.1. Absolute Maximum Ratings

| Symbol           | Parameter                     | Pin No.    | Min.       | Max.      | Unit |

|------------------|-------------------------------|------------|------------|-----------|------|

| T <sub>A</sub>   | Ambient Operating Temperature | ı          | 0          | 65        | °C   |

| T <sub>S</sub>   | Storage Temperature           | ı          | <b>-40</b> | +25       | °C   |

| V <sub>SUP</sub> | Supply Voltage                | 19, 47, 63 | 1          | 6         | V    |

| V <sub>I</sub>   | Input Voltage, all Inputs     | 1          | –0.3 V     | $V_{SUP}$ | -    |

| Vo               | Output Voltage, all Outputs   | -          | –0.3 V     | $V_{SUP}$ | _    |

| I <sub>O</sub>   | Output Current, all Outputs   |            | -10        | +10       | mA   |

# **2.5.2. Recommended Operating Conditions** at $T_A$ = 0 to 65 $^{\circ}C,\,f_{\Phi M}$ = 20.25 MHz

| Symbol                                 | Parameter                                               | Pin No.    | Min. | Тур. | Max.                    | Unit |

|----------------------------------------|---------------------------------------------------------|------------|------|------|-------------------------|------|

| V <sub>SUP</sub>                       | Supply Voltage                                          | 19, 47, 63 | 4.75 | 5.0  | 5.25                    | V    |

| $V_{\Phi 	ext{MIDC}}$                  | $\Phi$ M Clock Input D.C. Voltage                       | 62         | 1.5  | _    | 3.5                     | V    |

| $V_{\Phi MIAC}$                        | ΦM Clock Input<br>A.C. Voltage (p-p)                    |            | 0.8  | 1    | 2.5                     | V    |

| t <sub>ΦΜΙΗ</sub><br>t <sub>ΦΜΙL</sub> | ΦM Clock Input High/Low<br>Ratio                        |            | 0.9  | 1.0  | 1.1                     | 1    |

| $t_{\PhiMIHL}$                         | $\Phi \text{M}$ Clock Input High to Low Transition Time |            | _    | -    | 0.15<br>f <sub>⊕M</sub> | _    |

| V <sub>REIL</sub>                      | Reset Input Low Voltage                                 | 15         | _    | _    | 0.8                     | V    |

| V <sub>REIH</sub>                      | Reset Input High Voltage                                |            | 2.4  | _    | _                       | V    |

| t <sub>REIL</sub>                      | Reset Input Low Time                                    |            | 2    | _    | _                       | μs   |

| V <sub>VIL</sub>                       | Video Input Low Voltage                                 | 39 to 46   | _    | _    | 2.2                     | V    |

| V <sub>VIH</sub>                       | Video Input High Voltage                                |            | 2.8  | _    | _                       | V    |

# **Recommended Operating Conditions, continued**

| Symbol                         | Parameter                                              | Pin No.         | Min.                      | Тур.   | Max.                    | Unit |

|--------------------------------|--------------------------------------------------------|-----------------|---------------------------|--------|-------------------------|------|

| $V_{\PhiVIH}$                  | Video Input Hold Time after<br>ΦM Clock Input          | 39 to 46,<br>62 | 14                        | -      | -                       | ns   |

| $V_{VIS\Phi}$                  | Video Input Setup Time before ΦM Clock Input           |                 | 4                         | -      | _                       | ns   |

| V <sub>ODIL</sub>              | Outputs Disable Inputs<br>Low Voltage                  | 18              | _                         | -      | 0.8                     | V    |

| V <sub>ODIH</sub>              | Outputs Disable Inputs<br>High Voltage                 |                 | 2.4                       | -      | -                       | V    |

| V <sub>DSIL</sub>              | Descrambled Data Input<br>Low Voltage                  | 56              | _                         | _      | 0.8                     | V    |

| V <sub>DSIH</sub>              | Descrambled Data Input<br>High Voltage                 |                 | 2.4                       | -      | -                       | V    |

| $V_{\PhiAL}$                   | ΦA Clock Input Low Voltage                             | 17              | _                         | _      | 0.8                     | V    |

| $V_{\PhiAH}$                   | ΦA Clock Input High Voltage                            |                 | V <sub>SUP</sub><br>-0.8V | -      | -                       | _    |

| $rac{t_{\PhiAH}}{t_{\PhiAL}}$ | ΦA Clock Input<br>High/Low Ratio                       |                 | 0.9                       | 1.0    | 1.1                     | _    |

| $t_{\Phi AHL}$                 | ΦA Clock Input High to Low Transition Time             |                 | _                         | -      | 0.15<br>f <sub>ΦA</sub> | _    |

| t <sub>ФALH</sub>              | ΦA Clock Input Low to High Transition Time             |                 | _                         | _      | 0.15<br>f <sub>ΦA</sub> | _    |

| $f_{\PhiA}$                    | ΦA Clock Input Frequency                               |                 | _                         | 18.432 | _                       | MHz  |

| V <sub>IMIL</sub>              | IM Bus Input Low Voltage                               | 12 to 14        | _                         | _      | 0.8                     | V    |

| $V_{\text{IMIH}}$              | IM Bus Input High Voltage                              |                 | 2.4                       | _      | _                       | V    |

| $f_{\PhiI}$                    | ΦI IM Bus Clock Frequency                              |                 | 0.05                      | _      | 1000                    | kHz  |

| t <sub>IM1</sub>               | ΦI Clock Input Delay Time after IM Bus Ident Input     |                 | 0                         | _      | -                       | _    |

| t <sub>IM2</sub>               | Φl Clock Input<br>Low Pulse Time                       |                 | 3.0                       | _      | -                       | μs   |

| t <sub>IM3</sub>               | Φl Clock Input<br>High Pulse Time                      |                 | 3.0                       | _      |                         | μs   |

| t <sub>IM4</sub>               | ΦI Clock Input Setup Time before Ident Input High      |                 | 0                         | _      | _                       | _    |

| t <sub>IM5</sub>               | ΦI Clock Input Hold Time after Ident Input High        |                 | 1.5                       | _      | _                       | μs   |

| t <sub>IM6</sub>               | ΦI Clock Input Setup Time before Ident End–Pulse Input |                 | 6.0                       | -      | _                       | μѕ   |

# **Recommended Operating Conditions, continued**

| Symbol            | Parameter                                             | Pin No.  | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------------------------------------|----------|------|------|------|------|

| t <sub>IM7</sub>  | IM Bus Data Input Delay<br>Time after Φl Clock Input  | 12 to 14 | 0    | -    | _    | -    |

| t <sub>IM8</sub>  | IM Bus Data Input Setup<br>Time before ΦI Clock Input |          | 0    | -    | _    | -    |

| t <sub>IM9</sub>  | IM Bus Data Input Hold Time<br>after ФI Clock Input   |          | 0    | -    | _    | -    |

| t <sub>IM10</sub> | IM Bus Ident End-Pulse<br>Low Time                    |          | 3.0  | _    | _    | μs   |

# 2.5.3. Recommended Crystal Characteristics

| Symbol                           | Parameter                              | Min. | Тур.     | Max. | Unit |

|----------------------------------|----------------------------------------|------|----------|------|------|

| T <sub>A</sub>                   | Ambient Operating Temperature          | -20  | _        | +85  | °C   |

| f <sub>p</sub>                   | Parallel Resonance Frequency           | -    | 18.432*) | -    | MHz  |

| $\frac{\Delta f_p}{f_p}$         | Accuracy of Adjustment                 | ı    | ı        | ±40  | ppm  |

| $\frac{\Delta f_p}{f_p}$         | Frequency Deviation versus Temperature | _    | _        | ±40  | ppm  |

| R <sub>r</sub>                   | Series Resistance                      | ı    | 1        | 50   | Ω    |

| C <sub>0</sub>                   | Shunt Capacitance                      | 5.5  | 1        | 7.5  | pF   |

| C <sub>1</sub>                   | Motional Capacitance                   | 15   | _        | 20   | fF   |

| Р                                | Rated Drive Level                      | _    | 0.02     | _    | mW   |

| f <sub>p</sub><br>f <sub>H</sub> | Spurious Frequency Attenuation         | 20   | -        | -    | dB   |

<sup>\*)</sup> at  $C_L = 10$  pF. This frequency applies for a certain application. For other applications, an appropriate frequency must be chosen.

# **2.5.4. Characteristics** at T<sub>A</sub> = 0 to 65 °C, V<sub>SUP</sub> = 4.75 to 5.25 V, $f_{\Phi M}$ = 20.25 MHz

| Symbol                             | Parameter                                                  | Pin No.                | Min. | Тур.                   | Max. | Unit | Test Conditions             |

|------------------------------------|------------------------------------------------------------|------------------------|------|------------------------|------|------|-----------------------------|

| I <sub>SUP</sub>                   | Supply Current                                             | 63                     | -    | 100                    | 130  | mA   |                             |

| $V_{\PhiAOL}$                      | ΦΑ Audio Clock Output<br>Low Voltage                       | 65                     | -    | -                      | 2.0  | V    | I <sub>ΦAO</sub> = 0.5 mA   |

| $V_{\PhiAOH}$                      | ΦΑ Audio Clock Output<br>High Voltage                      |                        | 3.0  | -                      | -    | V    | −l <sub>ΦAO</sub> = 0.5 m A |

| t <sub>ФАНL</sub>                  | ΦΑ Audio Clock Output<br>High to Low Transition Time       |                        | _    | -                      | 10   | ns   |                             |

| $f_{\PhiA}$                        | ΦΑ Audio Clock Output<br>Frequency                         |                        | -    | 18.432                 | -    | MHz  |                             |

| V <sub>LCOL</sub>                  | Luma/Chroma Output<br>Low Voltage                          | 21 to 24,<br>27 to 38  | -    | -                      | 0.3  | V    | I <sub>LCO</sub> = 6 mA     |

| I <sub>LCOH</sub>                  | Luma/Chroma Output<br>High Current                         |                        | -    | -                      | 10   | μΑ   | V <sub>LCO</sub> = 5 V      |

| <sup>t</sup> LCOT                  | Luma/Chroma Output<br>Transition Time                      |                        | _    | _                      | 10   | ns   |                             |

| $t_{\Phi L C O H}$                 | Luma/Chroma Output Hold<br>Time after ΦM Clock Input       | 21 to 24,<br>27 to 38, | 12   | _                      | -    | ns   |                             |

| t <sub>ΦLCOS</sub>                 | Luma/Chroma Output Setup<br>Time after ΦM Clock Input      | 62                     | -    | _                      | 30   | ns   |                             |

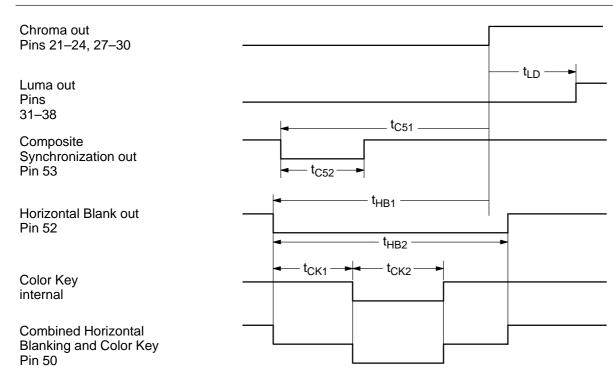

| t <sub>LD</sub>                    | Luma Output Delay Time after                               |                        | -194 | -                      | +839 | μs   |                             |

| V <sub>POL</sub>                   | PLL Bus Output Low Voltage                                 | 25, 26                 | -    | -                      | 0.2  | V    | I <sub>PO</sub> = 2 mA      |

| I <sub>POH</sub>                   | PLL Bus Output High Current                                |                        | -    | -                      | 10   | μΑ   | V <sub>PO</sub> = 5 V       |

| $f_{\PhiP}$                        | ΦP Clock Frequency                                         | 26                     | -    | $\frac{f_{\Phi M}}{4}$ | -    | -    |                             |

| $rac{t_{\PhiPOH}}{t_{\PhiPOL}}$   | ΦP Clock Output<br>High/Low Ratio                          |                        | 0.8  | 1                      | 1.25 | -    |                             |

| <sup>t</sup> PDOS⊕                 | PLL Data Output Setup<br>Time before ΦP Clock Output       | 25, 26                 | 20   | -                      | -    | ns   |                             |

| tФРDOH                             | PLL Data Output Hold<br>Time after ΦP Clock Output         |                        | 80   | _                      | -    | ns   |                             |

| V <sub>SOL</sub>                   | S Bus Output Low Voltage                                   | 64, 66, 67             | -    | -                      | 0.2  | V    | I <sub>SO</sub> = 2 mA      |

| I <sub>SOH</sub>                   | S Bus Output High Current                                  |                        | _    | -                      | 10   | μА   | V <sub>SO</sub> = 5 V       |

| t <sub>SOT</sub>                   | S Bus Output Transition Time                               |                        | _    | -                      | 10   | ns   |                             |

| $f_{\Phi S}$                       | ΦS S Clock Output Frequency                                | 67                     | -    | $\frac{f_{\PhiA}}{4}$  | -    | -    |                             |

| t <sub>S2</sub><br>t <sub>S1</sub> | ΦS S Clock Output<br>High/Low Ratio                        |                        | 0.9  | 1                      | 1.1  | -    |                             |

| t <sub>S3</sub>                    | ΦS S Clock Output Setup Time before Ident End–Pulse Output | 64, 67                 | 160  | 220                    | -    | ns   |                             |

# Characteristics, continued

| Symbol                             | Parameter                                                                | Pin No.  | Min.                  | Тур.                                   | Max.                  | Unit | Test Conditions               |

|------------------------------------|--------------------------------------------------------------------------|----------|-----------------------|----------------------------------------|-----------------------|------|-------------------------------|

| t <sub>S4</sub>                    | S Bus Data Output Setup Time before ΦS S Clock Output                    | 66, 67   | 100                   | -                                      | -                     | ns   |                               |

| t <sub>S5</sub>                    | S Bus Data Output Hold Time after $\Phi$ S S Clock Output                |          | 100                   | _                                      | -                     | ns   |                               |

| t <sub>S6</sub>                    | S Bus Ident End-Pulse<br>Output Low Time                                 | 64       | 300                   | 400                                    | _                     | ns   |                               |

| V <sub>BOL</sub>                   | Burst Bus Output Low Voltage                                             | 58 to 60 | _                     | -                                      | 0.4                   | V    | I <sub>DMO</sub> = 1.6 mA     |

| V <sub>BOH</sub>                   | Burst Bus Output High Voltage                                            |          | 2.8                   | _                                      | _                     | V    | -I <sub>DMO</sub> = 0.1 mA    |

| t <sub>BT</sub>                    | Burst Bus Output<br>Transition Time                                      |          | -                     | _                                      | 10                    | ns   |                               |

| ${\sf f}_{\Phi\sf B}$              | ΦB Burst Bus Clock Frequency                                             | 60       | -                     | $\frac{f_{\Phi M}}{2}$ or $f_{\Phi M}$ | _                     | -    |                               |

| t <sub>B3</sub><br>t <sub>B2</sub> | ФВ Clock Output<br>High/Low Ratio                                        |          | 0.9                   | 1                                      | 1.1                   | -    |                               |

| t <sub>B1</sub>                    | ΦB Clock Output Delay Time after Ident Output                            | 58, 60   | -                     | 0                                      | -                     | -    |                               |

| t <sub>B4</sub>                    | Ident Output Delay Time after ΦB Clock                                   |          | -                     | 0                                      | _                     | ı    |                               |

| t <sub>B5</sub>                    | Burst Bus Data Output Setup Time before $\Phi$ D Clock Output            | 59, 60   | _                     | 50                                     | _                     | ns   |                               |

| t <sub>B6</sub>                    | Burst Bus Data Output Hold Time after $\Phi$ B Clock Output              |          | _                     | 0                                      | _                     | -    |                               |

| $V_{\text{IMOL}}$                  | IM Bus Data Output Low Voltage                                           | 14       | _                     | _                                      | 0.3                   | V    | I <sub>IMO</sub> = 6 mA       |

| I <sub>IMOH</sub>                  | IM Bus Data Output<br>High Current                                       |          | -                     | _                                      | 10                    | μΑ   | V <sub>IMO</sub> = 5 V        |

| t <sub>4</sub>                     | IM Bus Data Output Setup Time before $\Phi$ I Clock Input High           | 14, 12   | 0                     | _                                      | _                     | -    |                               |

| t <sub>5</sub>                     | IM Bus Data Output Hold Time after $\Phi \text{I}$ Clock Input Fall      |          | 0                     | -                                      | _                     | -    |                               |

| V <sub>CLOL</sub>                  | Clamping Output Low Voltage                                              | 48       | _                     | -                                      | 0.2                   | ٧    | I <sub>CLO</sub> = 2 mA       |

| V <sub>CLOH</sub>                  | Clamping Output High Voltage                                             |          | _                     | _                                      | V <sub>SUP</sub> -0.5 | V    | -I <sub>CLO</sub> = 1 mA      |

| V <sub>AGCOL</sub>                 | AGC Output Low Voltage                                                   | 49       | _                     | _                                      | 0.4                   | ٧    | I <sub>AGCO</sub> = 6 mA      |

| I <sub>AGCOZ</sub>                 | AGC Output High-Impedance<br>Current                                     |          | -10                   | _                                      | +10                   | μΑ   | V <sub>AGC</sub> = 0 to 5 V   |

| V <sub>AGCOH</sub>                 | AGC Output High Voltage                                                  |          | V <sub>SUP</sub> -0.5 | _                                      | -                     | V    | -I <sub>AGC</sub> = 1 mA      |

| t <sub>AGCO</sub>                  | AGC Output Pulse Duration                                                |          | -                     | 40                                     | _                     | ms   |                               |

| t <sub>SAGCO</sub>                 | AGC Output Pulse Start Time                                              |          | – line No.            | 624                                    | -                     | -    |                               |

| V <sub>HBCKOL</sub>                | Combined Horizontal Blanking & Color Key Output Low Voltage              | 50       | -                     | -                                      | 0.4                   | V    | I <sub>HBCKO</sub> = 6 mA     |

| I <sub>HBCKOZ</sub>                | Combined Horizontal Blanking and Color Key Output High-Impedance Current |          | -10                   | _                                      | +10                   | μΑ   | V <sub>HBCKO</sub> = 0 to 5 V |

# Characteristics, continued

| Symbol              | Parameter                                                                     | Pin No.                      | Min. | Тур. | Max. | Unit | Test Conditions              |

|---------------------|-------------------------------------------------------------------------------|------------------------------|------|------|------|------|------------------------------|

| V <sub>НВСКОН</sub> | Combined Horizontal Blanking & Color Key Output High Voltage                  | 50                           | 4.0  | -    | -    | V    | -I <sub>HBCKO</sub> = 0.1 mA |

| t <sub>HB2</sub>    | Horizontal Blanking Output Time                                               |                              | -    | 10.5 | 0    | μs   |                              |

| t <sub>CK2</sub>    | Color Key High Z<br>Output Low Time                                           |                              | -    | 2.27 | -    | μs   |                              |

| <sup>t</sup> CK1    | Color Key Output Delay Time after Horizontal Blanking Output                  |                              | ı    | 5.5  | _    | μs   |                              |

| <sup>t</sup> HB1    | Horizontal Blanking Output<br>Lead Time before<br>Chroma Output High          | 50,<br>21 to 24,<br>27 to 30 | 5.8  | -    | 18.4 | μs   |                              |

| $V_{HVBOL}$         | Combined Horizontal and Vertical Blanking Output Low Voltage                  | 51                           | -    | -    | 0.4  | V    | I <sub>HVBO</sub> = 6 mA     |

| I <sub>HVBOZ</sub>  | Combined Horizontal and<br>Vertical Blanking Output<br>High-Impedance Current |                              | -10  | _    | +10  | μА   | V <sub>HVBO</sub> = 0 to 5 V |

| V <sub>HVBOH</sub>  | Combined Horizontal & Vertical Blanking Output High Voltage                   |                              | 4.0  | -    | -    | V    | -I <sub>HVBO</sub> = 0.1 mA  |

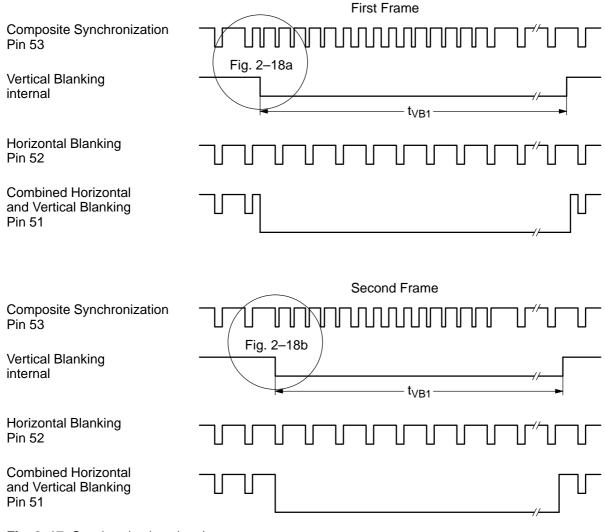

| t <sub>VB1</sub>    | Vertical Blanking Output Time                                                 |                              | -    | 0.64 | -    | ms   |                              |

| t <sub>HB2</sub>    | Horizontal Blanking Output Time                                               |                              | -    | 10.5 | -    | μs   | ]                            |

| V <sub>HBOL</sub>   | Horizontal Blanking Output<br>Low Voltage                                     | 52                           | -    | -    | 0.4  | V    | I <sub>HBO</sub> = 1.6 mA    |

| V <sub>НВОН</sub>   | Horizontal Blanking Output<br>High Voltage                                    |                              | 2.4  | -    |      | V    | -I <sub>HBO</sub> = 0.1 mA   |

| t <sub>HB2</sub>    | Horizontal Blanking Output<br>Low Time                                        |                              | -    | 12   | -    | μs   |                              |

| V <sub>CSOL</sub>   | Composite Sync Output<br>Low Voltage                                          | 53                           | -    | -    | 0.4  | V    | I <sub>CSO</sub> = 1.6 mA    |

| V <sub>CSOH</sub>   | Composite Sync Output<br>High Voltage                                         |                              | 2.8  | -    | -    | V    | -I <sub>CSO</sub> = 0.1 mA   |

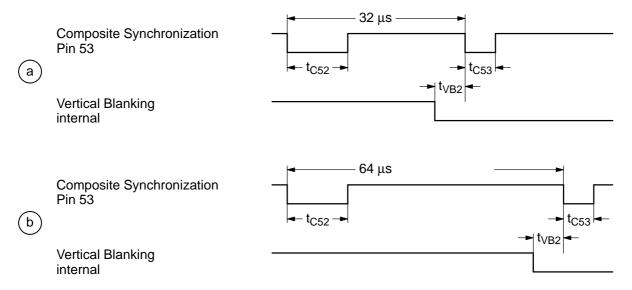

| t <sub>CS2</sub>    | Composite Sync Output<br>Low Time 1                                           |                              | ı    | 4.8  | -    | μs   |                              |

| t <sub>CS3</sub>    | Composite Sync Output<br>Low Time 2                                           |                              | ı    | 2.4  | -    | μs   |                              |

| t <sub>VB2</sub>    | Composite Sync Output Delay<br>Time after Vertical Blanking<br>Output         | 51, 53                       | -    | 1.5  | -    | μs   |                              |

| t <sub>CSOLC</sub>  | Composite Sync Output Lead<br>Time before Chroma Output                       | 53,<br>21 to 24,<br>27 to 30 | 4.2  | -    | 16.8 | μs   |                              |

| V <sub>PDOL</sub>   | Packet Data Output Low Voltage                                                | 55                           | -    | -    | 0.4  | V    | I <sub>PDO</sub> = 1.6 mA    |

| V <sub>PDOH</sub>   | Packet Data Output<br>High Voltage                                            |                              | 2.4  | _    | -    | V    | -I <sub>PDO</sub> = 0.1 mA   |

| V <sub>TSOL</sub>   | Teletext Sync Output<br>Low Voltage                                           | 57                           | -    | -    | 0.4  | V    | I <sub>TSO</sub> = 1.6 mA    |

| V <sub>TSOH</sub>   | Teletext Sync Output<br>High Voltage                                          |                              | 2.4  | -    | -    | V    | -I <sub>TSO</sub> = 0.1 mA   |

### 2.5.5. DRAM Interface Characteristics

| Symbol             | Parameter                                               | Pin No.                | Min. | Тур. | Max. | Unit | Test Conditions             |

|--------------------|---------------------------------------------------------|------------------------|------|------|------|------|-----------------------------|

| V <sub>DIL</sub>   | RAM Data Input Low Voltage                              | 1                      | -    | -    | 0.8  | V    |                             |

| V <sub>DIH</sub>   | RAM Data High Voltage                                   |                        | 2.0  | -    | -    | V    |                             |

| t <sub>DIS</sub>   | RAM Data Input Setup Time before CAS Output High        | 1, 68                  | -    | -    | 75   | ns   |                             |

| t <sub>DIH</sub>   | RAM Data Input Hold Time<br>after CAS Output High       |                        | 0    | -    | 33   | ns   |                             |

| V <sub>DOL</sub>   | RAM Data Output Low Voltage                             | 1                      | -    | -    | 0.4  | V    | I <sub>DO</sub> = 1.6 mA    |

| V <sub>DOH</sub>   | RAM Data Output High Voltage                            |                        | 2.4  | _    | _    | V    | -I <sub>DO</sub> = 0.1 mA   |

| t <sub>DT</sub>    | RAM Data Op. Transition Time                            |                        | 3    | -    | 50   | ns   |                             |

| t <sub>DHR</sub>   | RAM Data Hold Time after<br>RAS Low                     | 1, 8, 68               | 140  | -    | -    | ns   |                             |

| t <sub>DS</sub>    | RAM Data Setup Time before CAS Low                      |                        | 20   | _    | _    | ns   |                             |

| t <sub>DH</sub>    | RAM Data Output Hold Time after CAS Output Low          | 1, 68                  | 80   | -    | _    | ns   |                             |

| V <sub>AOL</sub>   | RAM Address Output<br>Low Voltage                       | 2 to 6,<br>9 to 11     | -    | -    | 0.4  | V    | I <sub>AO</sub> = 1.6 mA    |

| V <sub>AOH</sub>   | RAM Address Output<br>High Voltage                      |                        | 2.4  | _    | -    | V    | -I <sub>AO</sub> = 0.1 mA   |

| t <sub>AT</sub>    | RAM Address Output<br>Transition Time                   |                        | 3    | -    | 50   | ns   |                             |

| t <sub>RAH</sub>   | Row Address Output Hold Time after RAS Output Low       | 2 to 6, 9 to<br>11, 8  | 22   | _    | _    | ns   |                             |

| t <sub>ASR</sub>   | Row Address Output Setup<br>Time before RAS Output Low  |                        | 30   | -    | -    | ns   |                             |

| t <sub>AR</sub>    | Column Address Output Hold<br>Time after RAS Output Low | 2 to 6, 9 to<br>11, 68 | 125  | -    | -    | ns   |                             |

| <sup>t</sup> CAH   | Column Address Output Hold<br>Time after CAS Output     |                        | 70   | -    | -    | ns   |                             |

| t <sub>ASC</sub>   | Column Address Output Setup<br>Time before CAS Output   |                        | 10   | -    | -    | ns   |                             |

| V <sub>RASOL</sub> | RAS Output Low Voltage                                  | 8                      | -    | -    | 0.4  | V    | I <sub>RASO</sub> = 1.6 mA  |

| V <sub>RASOH</sub> | RAS Output High Voltage                                 |                        | 2.4  | -    | -    | V    | -I <sub>RASO</sub> = 0.1 mA |

| t <sub>RAST</sub>  | RAS Output Transition Time                              |                        | 3    | -    | 50   | ns   |                             |

| t <sub>RAS</sub>   | RAS Low Pulsewidth                                      |                        | 125  | -    | 3000 | ns   |                             |

| t <sub>RP</sub>    | RAS Output Precharge Time                               |                        | 130  | -    | -    | ns   |                             |

| t <sub>RSH</sub>   | RAS Output Hold Time after CAS Output Low               | 8, 68                  | 110  | -    | -    | ns   |                             |

| V <sub>CASOL</sub> | CAS Output Low Voltage                                  | 68                     | -    | -    | 0.4  | V    | I <sub>CASO</sub> = 1.6 mA  |

| V <sub>CASOH</sub> | CAS Output High Voltage                                 |                        | 2.4  | -    | -    | V    | -I <sub>CASO</sub> = 0.1 mA |

| t <sub>PC</sub>    | Page Mode Cycle Time                                    |                        | 170  | -    | -    | ns   |                             |

# **DRAM Interface Characteristics, continued**

| Symbol            | Parameter                                   | Pin No. | Min. | Тур. | Max. | Unit | Test Conditions           |

|-------------------|---------------------------------------------|---------|------|------|------|------|---------------------------|

| t <sub>CAST</sub> | CAS Output Transition Time                  | 68      | 3    | -    | 50   | ns   |                           |

| t <sub>CP</sub>   | CAS Output Precharge Time                   |         | 70   | -    | -    | ns   |                           |

| t <sub>CAS</sub>  | CAS Low Pulsewidth                          |         | 95   | -    | 150  | ns   |                           |

| t <sub>RCD</sub>  | CAS Output Delay Time after RAS Output      | 68, 8   | 45   | -    | -    | ns   |                           |

| t <sub>CSH</sub>  | CAS Output Hold Time after RAS Output       |         | 170  | -    | -    | ns   |                           |

| t <sub>CRP</sub>  | CAS Output Precharge Time before RAS Output |         | 150  | -    | -    | ns   |                           |

| V <sub>WOL</sub>  | WRITE Output Low Voltage                    | 7       | -    | -    | 0.4  | V    | I <sub>WO</sub> = 1.6 mA  |

| V <sub>WOH</sub>  | WRITE Output High Voltage                   |         | 2.4  |      |      | V    | -l <sub>WO</sub> = 0.1 mA |

| t <sub>WT</sub>   | WRITE Output Transition Time                |         | 3    |      | 50   | ns   |                           |

| t <sub>CWL</sub>  | WRITE Low before CAS High                   | 7, 68   | 180  |      |      | ns   |                           |

| t <sub>WCH</sub>  | WRITE Command Hold Time after CAS Low       |         | 80   | -    | -    | ns   |                           |

| t <sub>RCH</sub>  | READ Command Hold Time after CAS High       |         | 50   | -    | -    | ns   |                           |

| t <sub>RRH</sub>  | READ Command Hold Time<br>after RAS High    | 7, 8    | 20   | -    | -    | ns   |                           |

#### 2.5.6. Waveforms

Fig. 2-13: IM bus waveforms

Fig. 2-14: S bus waveforms

Fig. 2-15: Burst bus waveforms

Fig. 2-16: DRAM waveform

Fig. 2–17: Synchronization signals

Fig. 2-18: Details of Fig. 2-17

Fig. 2-19: Timing of video and sync signals

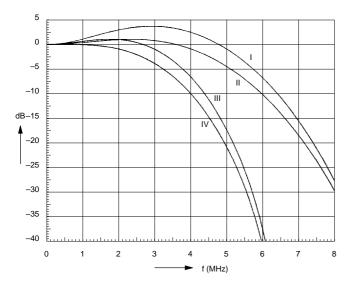

### 2.5.7. Frequency Responses

5 0 -5 -10 dB-15 -20 -25 -30 -35 -40 0 1 2 3 4

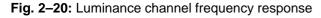

Fig. 2–21: Chrominance channel frequency response

Table 2–1: Selection of the luma filter response

| LFI | Curve No. |

|-----|-----------|

| 0   | I         |

| 1   | II        |

| 2   | III       |

| 3   | IV        |

Table 2–2: Selection of the chroma filter response

| CFI                   | Curve No. |

|-----------------------|-----------|

| 0                     | ļ<br>     |

| 1                     | II        |

| 2                     | III       |

| 3                     | IV        |

| 4                     | V         |

| 5                     | VI        |

| 2<br>3<br>4<br>5<br>6 | VII       |

| 7                     | VIII      |

#### 3. Functional Description

The DMA 2271, DMA 2280 and DMA 2281 process the digitized D2-MAC video signal supplied by the VCU 2133 or by the UVC 3130 in the various circuit parts shown in Fig. 1-4. The resulting digital luminance and chrominance signals are then reconverted to analog signals in the VCU or HDAA. The resulting digital audio signals are processed in the AMU 2481 Audio Mixer which provides filtering of the medium-quality channels and allows mixing of the four sound channels. The AMU's digital output signals are reconverted to analog in the ACP 2371 Audio Processor, which additionally carries out functions like adjustment of volume, bass and treble, loudness, etc. Remaining digital data as service and channel information in packet 0 or line 625 can be handled by software via the IM bus or by additional hardware which uses the serial B-Data interface (B-Data, B-Clock and B-Sync). Section 1.2. shows how the DMA 2271, DMA 2280 and DMA 2281 can be used together with other circuits of INTERMETALLS's DIGIT 2000 digital TV system to realize a multistandard NTSC/PAL/SECAM/C/D/D2-MAC color TV receiver.

To understand the signal processing in the DMA 2271, DMA 2280, and DMA 2281 it may be useful to distinguish three different function blocks, namely:

- Clock and Data Recovery

- Video Processing

- Sound/Data Processing

#### 3.1. Clock and Data Recovery

#### 3.1.1. The Code Converter

This circuit converts the digitized C/D/D2–MAC baseband signal, delivered by the VCU 2133 in a parallel Gray code, into a simple binary–coded signal. The function of the circuit is controlled by the CCU 3000 via the IM bus (see section 4.2.).

# 3.1.2. The Video Clamping Circuit and the AGC Circuit

The video clamping circuit measures the DC voltage level of the clamp period and, by means of the pulse density modulated signal from pin 48, sets the DC level of the clamp period to a constant 5.5 V. The white and the black levels in line 624 are measured for automatic gain control (AGC pin 49) and the two values are fed to the IM bus interface which organizes the data communication with the CCU.

AGC (pin 49) = high if WL - BL < 224

AGC (pin 49) = high impedance if  $224 \le WL - BL \le 240$

AGC (pin 49) = low if WL - BL > 240

#### 3.1.3. The Phase Comparator and the PLL Filter

The phase comparator derives the reference signal from the slopes contained in the data burst of each line. Its output signal, an 8-bit word which is passed through a digital lowpass filter, is added to an 8-bit word, VCOA, which is provided by the CCU for adjustment of the crystal frequency. This digital PLL signal is output via pins 25 and 26 and routed to the MCU 2600 Clock Generator IC thus closing the PLL, existing between DMA 2271, DMA 2280, and DMA 2281, VCU 2133 Video Codec and MCU 2600 Clock Generator IC. In this way, the main clock signal FM of the system is in phase with the duobinary-coded signal.

To adjust the crystal frequency, it is possible to render inoperative the PLL by setting PLLO bit 4 in address 201 (Table 4–1). The VCO in the MCU is then free–running and the center frequency can be aligned by varying the data word VCOA (bits 0 to 7) in the IM bus address 14.

# 3.1.4. The Data Slicer and the Synchronization Circuit

The digitized C/D/D2–MAC baseband signal is filtered by a 5 MHz lowpass filter before being routed to the data slicer. The output of the slicer is connected to pin 59 (B–Data). In phase with the continuous bit stream of 20.25 or 10.125 MBit/s, a clock signal (B–Clock), a synchronization signal (B–Sync) and a signal for Teletext information (TTSYNC) are available at pins 60, 58, and 57 (see Fig. 2–15).

The vertical synchronization pulse, on–chip, is derived from a 64–bit correlator which compares the data stream at the output of the slicer with the fixed Frame Synchronization Word (FSW). Whenever the correlation is equal to or greater than 61 a frame reset pulse is generated. Horizontal synchronization is derived by counting. In phase with the video outputs (L0 to L7, C0 to C7), the various synchronization and blanking signals are outputs at pins 50 to 53 (Fig. 2–17, 2–18 and 2–18).

#### 3.2. Video Processing

The DMA 2271, DMA 2280, and DMA 2281 process the C/D/D2–MAC baseband signal, digitized by the VCU or UVC at a sample frequency of 20.25 MHz. For time expansion, the video samples of each line are stored in an on–chip RAM and read to at the lower frequencies of 13.5 MHz for the luminance signal and 6.75 MHz for the color difference signals.

#### 3.2.1. The Luminance Store

Time expansion of the luminance signal is achieved by digitizing the analog signal at a clock frequency of 20.25 MHz, storing the Bytes, and reading them at a frequency of 13.5 MHz. For this, a fast RAM is provided on—chip.

#### 3.2.2. The Luminance Interpolating Filter

An interpolation from 13.5 MHz to 20.25 MHz is performed in order to overcome the need for a second system clock of 13.5 MHz and to simplify the reconstruction filters placed after the D/A conversion (RGB outputs of the VCU). The interpolation filter has a linear phase and can be switched to broad or narrow bandwidth by means of the CCU via the IM bus (bits 10 and 11, address 201). The different frequency responses are shown in Fig. 2–20 and in Table 2–1.

#### 3.2.3. The Contrast Multiplier

After the luminance interpolating filter is a contrast multiplier. The contrast setting is controlled by the CCU via the IM bus (bits 10 to 15, address 200), depending on the user's instruction. From the contrast multiplier, the digital luminance signal is fed back to the VCU 2133 in the form of an 8-bit signal. In the VCU, this signal is converted from digital to analog and fed to the RGB matrix. The setting range of the contrast multiplier comprises 6 bits (64 steps). If the product at the multiplier's output is higher than the working range, the largest possible number is output.

#### 3.2.4. The Chrominance Store

The chrominance store contains the color information for 3 lines. It is used for time expansion and line interpolation. The input frequency is 20.25 MHz, the output frequency 6.75 MHz.

#### 3.2.5. The Line Interpolating Filter

The color difference signals are transmitted within alternate lines as U and V. A "1, 2, 1" post–filter required to interpolate the color difference information is implemented. The action of the filter is for even lines:

$$U = U_n, V = \frac{V_{n-1} + V_{n+1}}{2}$$

and for odd lines:

$$U = \ \frac{U_{n-1} + U_{n+1}}{2} \ , \ V = V_n$$

#### 3.2.6. The Chrominance Interpolating Filter

After the line interpolating filter the 8-bit color difference signals U and V are routed to the chroma interpolating filter which has linear phase and can be switched to different frequency responses via the IM bus (Fig.

NO TAG, Table 2–2) using bits 13 to 15 in address 201. This filter is used for conversion of the sample rate from 6.75 MHz up to 10.125 MHz.

# 3.2.7. The Color Saturation Multiplier

The digital color difference signals U and V are routed to a color saturation multiplier, whose setting is also controlled by the CCU via the IM bus (address 23). The range of the multiplier comprises 6 bits, with each color difference signal being set independently.

The PAL matrix in the VCU requires a compensation factor of 0.71. This means that the color saturation factor for (B-Y) is equal to 0.71 the color saturation factor for (R-Y). Both factors are calculated in the CCU.

#### 3.2.8. The Color Multiplexer

The color difference signals are transferred back to the VCU 2133 in multiplex via a 4–line bus. Demultiplexing takes place in the VCU. The digital signals are then reconverted to analog. Subsequently they are dematrixed in the RGB matrix together with the Y signal, giving the RGB signals which drive the output amplifiers of the VCU 2133 Video Codec.

The color multiplexer can drive a 4-line bus with an effective sample rate of 5.6025 MHz for each color difference signal or an 8-line bus with a sample rate of 10.125 MHz. This function is controlled by the IM bus (Table 4-1), using bit 6 in address 201.

#### 3.3. Sound/Data Processing

This section begins with a descrambler and de-interleaver. The descrambler uses the same pseudo-random binary sequence (PRBS) generator as is used for the scrambling process. Its clock rate is 10.125 MHz or 20.25 MHz. The de-interleaver corrects the succession of the transmitted packet bits which are interleaved in order to minimize the effect of multiple bit errors.

Table 3–1: Transmission Order

| 1 2 | 95  | 189 | 283 | 377 | 471 | 565 | 659 |

|-----|-----|-----|-----|-----|-----|-----|-----|

|     | 96  | 190 | 284 | 378 | 472 | 566 | 660 |

|     |     |     |     |     |     |     |     |

| 93  | 187 | 281 | 375 | 469 | 563 | 657 | 751 |

| 94  | 188 | 282 | 376 | 470 | 564 | 658 | (1) |

#### 3.3.1. The Golay and PT Byte Decoder

The data format has changed now from data burst format (99 bits) to packet format (751 bits). The header of each packet contains defined addresses for the different sound and data services and four bits representing the sound characteristics. The PT Byte of each packet distinguishes between sound and data packets. After correction of header and PT Byte with the Golay and PT Byte decoder, this information is used for automatic configuration of the DMA 2271, DMA 2280, and DMA 2281.

In addition, the Golay decoder is used for measuring the bit error rate of the transmission channel. The bits in error in each packet header are accumulated over one frame (82 packets). The sum is stored in IM bus register 206 (Table 4–2) and can be read by the CCU which may control different muting functions.

#### 3.3.2. The Address Comparator

The DMA 2271, DMA 2280, and DMA 2281 D2–MAC Decoders are able to treat different sound services automatically by decoding the address field of the packet header. The two continuity bits CI1 and CI0 are used to link successive packets of the same service in case of a 120 Byte sound coding service.

Among the different coding characteristics all combinations are possible. The user can select up to four sound channels simultaneously by programming the sound services via the IM bus (address 203, 194, 195 and 196). These addresses are compared with the address of each transmitted sound packet. At correspondence, this packet is selected and decoded.

### 3.3.3. The Sound Decoder

The sound decoding section converts all types of selected sound packets into a sequence of 14—bit sound samples. The medium—quality channels are upsampled to the 32 kHz sampling frequency of the high-quality channels, i.e. every sample of a medium—quality channel is put out twice, the second time as a zero sample. The second part of the interpolation is performed in the AMU 2481 Audio Mixer where two oversampling filters are provided. The error correction section uses a range check and/or Hamming decoder, depending on the sound coding mode. The Hamming decoder is able to correct one error per sample and to detect double er-

rors. The range check uses the highly protected scale factor bits to check the MSBs of each sample. Its error correction and detection abilities are shown in Table 3–2.

Erroneous samples, i.e. samples with uncorrectable errors, are concealed by replacement with interpolated adjacent samples. The storage capacity for buffering the sound samples during processing and for obtaining a smooth, regular output of sound samples is provided by an external 64–K DRAM. To ensure the continuity of output sound samples in case of packet loss or packet gain, the silence information is used and blocks of samples corresponding to "silence" are repeated or omitted.

#### 3.3.4. The Sound Multiplex

After extension from 14 bits to 16 bits, the sound samples of the four channels are loaded into a 64-bit shift register and transferred to the AMU 2481 Audio Mixer via a serial 3-lines S bus. Fig. 2-14 shows the S bus timing.

Table 3–2: Error correction and detection

| Scale<br>Factor | Protection<br>Range | Defective<br>Bits    | Error<br>Correc-<br>tion | Error<br>Detec-<br>tion |  |

|-----------------|---------------------|----------------------|--------------------------|-------------------------|--|

| linear:         |                     |                      |                          |                         |  |

| 111             | 1                   | -                    | 1                        | 1                       |  |

| 110             | 2                   | X13, X12             | 1                        | 1                       |  |

| 101             | 3                   | X13, X12, X11        | 1                        | 2                       |  |

| 011             | 4                   | X13 → X10            | 1                        | 2                       |  |

| 100             | 5                   | X13 → X9             | 1                        | 3                       |  |

| 010             | 6                   | X13 → X8             | 2                        | 3                       |  |

| 001             | 7                   | $X13 \rightarrow X7$ | 2                        | 4                       |  |

| 000             | 8                   | X13 → X6             | 2                        | 4                       |  |

| compan          | ded:                |                      |                          |                         |  |

| 010             | 6                   | X9, X8               |                          | 1                       |  |

| 001             | 7                   | X9, X8, X7           | -                        | 2                       |  |

| 000             | 7                   | X9, X8, X7           | _                        | 2                       |  |

#### 3.3.5. The $\Phi$ A Audio Clock

The audio clock  $\Phi$ A for the AMU 2481 Audio Mixer and the ACP 2371 Audio Processor is also supplied by the DMA 2271, DMA 2280 and DMA 2281 which generate this 18.432 MHz clock by means of the crystal connected to pins 16 and 17 and supply it via pin 65. The frequency of 18.432 MHz is an integer multiple of the sound sampling frequency (32 kHz).

The  $\Phi$ A audio clock output pin 65 can be switched over to the normal main clock  $\Phi$ M if a standard other than C/D/D2–MAC is received. For this, bit ACS in address 204 of the IM bus is provided (Table 4–1).

The clock frequency  $\Phi$ S for the serial S bus is also derived from the audio clock  $\Phi$ A (pin 65) by dividing by eight (18.432 MHz: 4 = 4.608 MHz)

#### 3.3.6. The Buffer for Packet 0

One packet address (000H) is reserved for service and network identification data. A 720-bit (90 Byte) Buffer is

implemented on-chip especially for this, and is controlled by the CCU via the IM bus (bits 8 and 9, address 204). The following conditions must be met to ensure that a received packet is stored in this buffer:

Packet Address PA = 000H Packet Type PT = F8H

Data Group Type TG = selected type in IM bus

register 204

Packet 0 Status P0 = 0 (see IM bus registers 204

and 206)

The packet 0 buffer can be read sequentially from a 16-bit IM bus register (address 210, Table 4-2). One complete read cycle takes about 1.5 ms (IM bus frequency = 1 MHz). It is possible to reset and to clear the buffer via the IM bus in order to repeat the last-read cycle or to receive the next zero packet. Additionally, the last 16 bits of the zero packet are used for error checking. This CRC check calculates the 16-bit syndrom vector of the packet concerned and stores it in an IM bus register. It can then be used by software for error detection.

#### 4. The Three Serial Interfaces

#### 4.1. The S Bus Interface and the S Bus

The S bus has been designed to connect the digital sound output of the DMA 2271, DMA 2280, and DMA 2281 MAC Decoders or the MSP 2400 NICAM Demodulator/Decoder to audio—processing ICs such as the AMU 2481 Audio Mixer or the ACP 2371 Audio Processor etc., and to connect these ICs one to the other. The S bus is a unidirectional, digital bus which transmits the sound information in one direction only, so that it is not necessary to solve priority problems on the bus.

The S bus consists of the three lines: S–Clock, S–Ident, and S–Data. The DMA 2271, DMA 2280, and DMA 2281 or the MSP 2400 generates the signals S–Clock and S–Ident, which control the data transfer to and between the various processors which follow the DMA 2271, DMA 2280, and DMA 2281 or the MSP 2400. For this, the S–Clock and S–Ident inputs of all processors in the system are connected to the S–Clock and S–Ident outputs of the DMA 2271, DMA 2280, and DMA 2281 or the MSP 2400. S–Data output of the DMA 2271, DMA 2280, and DMA 2281 or MSP 2400 is connected to the S–Data input of the next following AMU, the AMU's S–Data output is connected to the ACP's S–Data input and so on.

The sound information is transmitted in frames of 64 bits, divided into four successive 16—bit samples. Each sample represents one sound channel. The timing of a complete transmission of four samples is shown in Fig. 2–14, the times are specified under "Recommended Operating Conditions". The transmission starts with the LSB of the first sample. The S–Clock signal is used to write the data into the receiver's input register. the S–Ident signal marks the end of one frame of 64 bits and is used as latch pulse for the input register. The repetition rate of S–Ident pulses is identical to the sampling rate of the D2–MAC or NICAM sound signal; thus it is possible to transfer four sound channels simultaneously.

The S bus interface of the DMA 2271, DMA 2280, and DMA 2281 mainly consists of an output register, 64–bit wide. The timing to write bit by bit is supplied by the S–Clock signal. In the case of an S–Ident pulse, the contents of the output register are written to the S–Data output.

#### 4.2. The IM Bus Interface and the IM Bus

### 4.2.1. The IM Bus

The INTERMETALL Bus (IM Bus for short) was designed to control the DIGIT 2000 ICs by the CCU Central Control Unit. Via this bus the CCU can write data to the ICs or read data from them. This means the CCU acts as a master, whereas all controlled ICs have purely slave status.