NOT RECOMMENDED FOR NEW DESIGNS

November 1996

63kHz, Nanopower, BiMOS Operational Amplifiers

#### Features

- High Input Resistance . . . . . . . . . . . . . . . . . . 2T $\Omega$  (Typ)

- Standby Power at V+ = 5V . . . . . . . . . . . . 300nW (Typ)

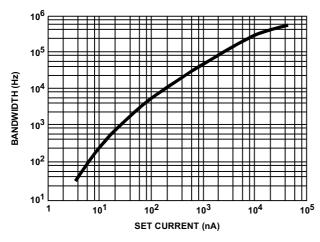

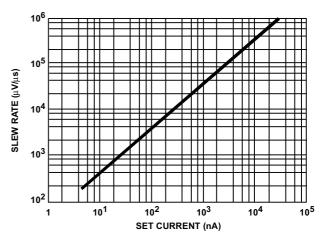

- Supply Current, BW, Slew Rate Programmable Using External Resistor

- 5V to 15V Supply

- · Output Drives Typical Bipolar Type Loads

## **Ordering Information**

| PART NUMBER<br>(BRAND) | TEMP.<br>RANGE (°C) | PACKAGE   | PKG.<br>NO. |

|------------------------|---------------------|-----------|-------------|

| CA3440AE               | -55 to 125          | 8 Ld PDIP | E8.3        |

| CA3440E                | -55 to 125          | 8 Ld PDIP | E8.3        |

| CA3440M<br>(3440)      | -55 to 125          | 8 Ld SOIC | M8.15       |

#### Description

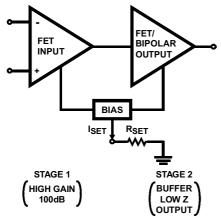

The CA3440A and CA3440 (see Note) are integrated circuit operational amplifiers that combine the advantages of MOS and bipolar transistors on a single monolithic chip.

The CA3440A and CA3440 BiMOS op amps feature gate protected PMOS transistors in the input circuit to provide very high input impedance, very low input currents (less than 10pA). These devices operate at total supply voltage from 5V to 15V and can be operated over the temperature range from -55°C to 125°C. Their virtues are programmability and very low standby power consumption (300nW). These operational amplifiers are internally phase compensated to achieve stable operation in the unity gain follower configuration. Terminals are also provided for use in applications requiring input offset voltage nulling. The use of PMOS in the input stage results in common mode input voltage capability down to 0.5V below the negative supply terminals, an important attribute for single supply applications. The output stage uses MOS complementary source follower form which permits moderate load driving capability (10k $\Omega$ ) at very low standby currents (50nA).

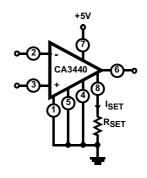

The CA3440A and CA3440 have the same 8 pin terminal pinout as the "741" and other industry standard op amps with two exceptions: terminals one and five must be connected to the negative supply or to a potentiometer if nulling is required. Terminal 8 must be programmed through an external resistor returned to the negative supply.

NOTE: Formerly Developmental Type No. TA10590.

#### **Pinout**

CA3440, CA3440A (PDIP, SOIC) TOP VIEW

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. Copyright © Harris Corporation 1996

File Number 1318.3

#### **Absolute Maximum Ratings** Thermal Information $\theta_{JA}$ (°C/W) Thermal Resistance (Typical, Note 2) Differential Input Voltage......9V DC Input Voltage . . . . . . . . . . . . (V+ +8V) to (V- -0.5V) SOIC Package..... Maximum Junction Temperature (Die)......175°C Output Short Circuit Duration (Note 1)..... Indefinite Maximum Junction Temperature (Plastic Package) . . . . . . . . 150°C Maximum Storage Temperature Range $\dots -65^{\circ}$ C to $150^{\circ}$ C **Operating Conditions** (SOIC - Lead Tips Only) Temperature Range . . . . . . . . . -55°C to 125°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. Short circuit may be applied to ground or to either supply.

- 2.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

**Electrical Specifications** Typical Values Intended Only for Design Guidance,  $V_{SUPPLY} = \pm 5V$ ,  $R_{SET} = 10M\Omega$ ,  $T_A = 25^{\circ}C$

| PARAMETER                       | SYMBOL            | TEST CONDITIONS        |                   | CA3440A | CA3440 | UNITS              |

|---------------------------------|-------------------|------------------------|-------------------|---------|--------|--------------------|

| Input Resistance                | R <sub>I</sub>    |                        |                   | 2       | 2      | TΩ                 |

| Input Capacitance               | C <sub>I</sub>    |                        |                   | 3.5     | 3.5    | pF                 |

| Output Resistance               | R <sub>O</sub>    |                        |                   | 450     | 450    | Ω                  |

| Equivalent Input                | e <sub>N</sub>    | f = 1kHz               | $R_S = 100\Omega$ | 110     | 110    | nV/√ <del>Hz</del> |

| Noise Voltage                   |                   | f = 10kHz              |                   | 110     | 110    | nV/√ <del>Hz</del> |

| Short-Circuit Current<br>Source | I <sub>OM</sub> + |                        |                   | 15      | 15     | mA                 |

| To Opposite Supply<br>Sink      | I <sub>OM</sub> - |                        |                   | 4.5     | 4.5    | mA                 |

| Gain Bandwidth Product          | f <sub>T</sub>    |                        |                   | 63      | 63     | kHz                |

| Slew Rate                       | SR                |                        |                   | 0.03    | 0.03   | V/μs               |

| Transient Response Rise Time    | t <sub>R</sub>    | $R_L = 10k\Omega, C_L$ | = 100pF           | 5.6     | 5.6    | μs                 |

| Overshoot                       | os                |                        |                   | 10      | 10     | %                  |

**Electrical Specifications** For Equipment Design, At  $V_{SUPPLY} = \pm 5V$ ;  $R_{SET} = 10M\Omega$ ,  $T_A = 25^{\circ}C$ , Unless Otherwise Specified

|                                        | SYMBOL                   | TEST<br>CONDITIONS | CA3440 |      | CA3440A |      |      |     |                      |

|----------------------------------------|--------------------------|--------------------|--------|------|---------|------|------|-----|----------------------|

| PARAMETER                              |                          |                    | MIN    | TYP  | MAX     | MIN  | TYP  | MAX | UNITS                |

| Input Offset Voltage                   | $ V_{IO} $               |                    | -      | 5    | 10      | -    | 2    | 5   | mV                   |

| Input Offset Current                   | 1 <sub>10</sub>          |                    | -      | 2.5  | 30      | -    | 2.5  | 20  | pA                   |

| Input Current                          | 1 <sub>1</sub>           |                    | -      | 10   | 50      | -    | 10   | 40  | pA                   |

| Large Signal Voltage Gain              | A <sub>OL</sub>          | $R_L = 10k\Omega$  | 10     | 100  | -       | 10   | 100  | -   | kV/V                 |

|                                        |                          |                    | 80     | 100  | -       | 80   | 100  | -   | dB                   |

| Common Mode Rejection Ratio            | CMRR                     |                    | -      | 100  | 320     | -    | 100  | 320 | μV/V                 |

|                                        |                          |                    | 70     | 80   | -       | 70   | 80   | -   | dB                   |

| Common Mode Input Voltage Range        | V <sub>ICR</sub> +       |                    | +3.5   | +3.7 | -       | +3.5 | +3.7 | -   | V                    |

|                                        | V <sub>ICR</sub> -       | 1                  | -5.0   | -5.3 | -       | -5.0 | -5.3 | -   | V                    |

| Power Supply Rejection Ratio           | PSRR                     |                    | -      | 32   | 320     | -    | 32   | 320 | μV/V                 |

|                                        |                          |                    | 70     | 90   | -       | 70   | 90   | -   | dB                   |

| Max Output Voltage                     | V <sub>OM</sub> +        |                    | +3     | +3.2 | -       | +3   | +3.2 | -   | V                    |

|                                        | V <sub>OM</sub> -        | 1                  | -3     | -3.2 | -       | -3   | -3.2 | -   | V                    |

| Supply Current                         | l+                       |                    | -      | 10   | 17      | -    | 10   | 17  | μΑ                   |

| Device Dissipation                     | $P_{D}$                  |                    | -      | 100  | 170     | -    | 100  | 170 | μW                   |

| Input Offset Voltage Temperature Drift | $\Delta V_{IO}/\Delta T$ |                    | -      | 4    | -       | -    | 4    | -   | $\mu V/^{\text{O}}C$ |

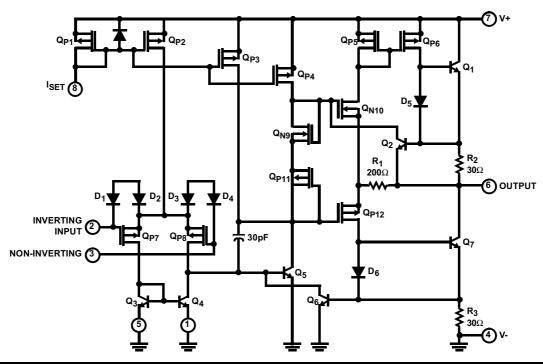

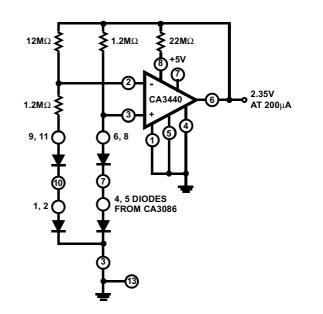

## Schematic Diagram

# **Application Information**

FIGURE 1. NANOPOWER OP AMP (SUPPLY CURRENT PROGRAMMABLE USING  $R_{SET}$ ), 1pA TYPICAL INPUT BIAS CURRENT, 4.0V TO 15V SUPPLY

As  $R_{SET}$  is increased,  $I_{SET}$  and the standby power decrease while the BW/SR also decrease.

Operating at a +5V single supply, the CA3440 exhibits the following characteristics:

| R <sub>SET</sub> | STANDBY<br>POWER | BW     | SR          |

|------------------|------------------|--------|-------------|

| 1ΜΩ              | 250μW            | 164kHz | 0.17V/μs    |

| 10ΜΩ             | 25μW             | 27kHz  | 0.017V/μs   |

| 100M $Ω$         | 2.5μW            | 2.6kHz | 0.0017V/μs  |

| 1GΩ              | 250nW            | 78kHz  | 0.00017V/μs |

FIGURE 2. NANOPOWER OP AMP (USABLE STANDBY POWER VS PROGRAMMING RESISTOR R<sub>SET</sub>)

The CA3440 is pin compatible with the 741 except that pins 1 and 5 (typical negative nulling pins) must be connected either directly to pin 4 or to a negative nulling potentiometer. In addition, pin 8, the  $I_{SET}$  terminal, must be returned to either ground or -V via  $R_{SET}$ .

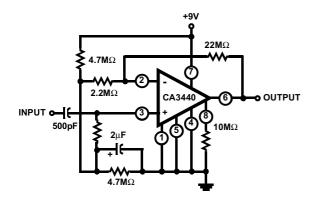

# **Typical Applications**

$R_{IN}$  >20M $\Omega$ Standby Power = 90 $\mu$ W Gain = 20dB BW: 20Hz to 3kHz SR = 0.016V/ $\mu$ s

FIGURE 3. HIGH INPUT IMPEDANCE AMPLIFIER

FIGURE 4. MICROPOWER BANDGAP REFERENCE

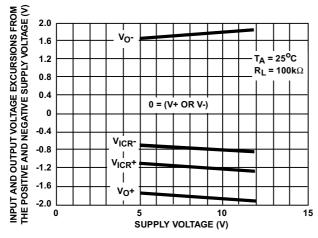

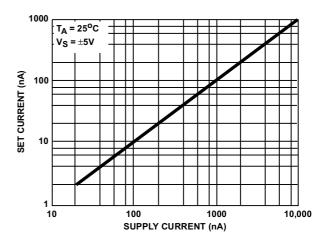

## Typical Performance Curves

FIGURE 5. OUTPUT VOLTAGE SWING AND COMMON MODE INPUT VOLTAGE RANGE vs SUPPLY VOLTAGE

FIGURE 6. SET CURRENT vs SUPPLY CURRENT

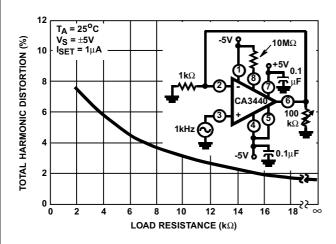

FIGURE 7. TOTAL HARMONIC DISTORTION vs LOAD RESISTANCE

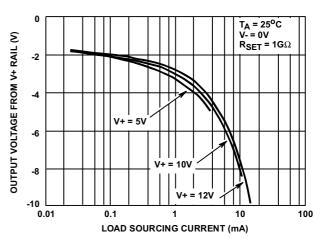

FIGURE 8. OUTPUT VOLTAGE vs SOURCING LOAD CURRENT

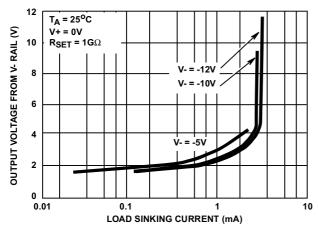

FIGURE 9. OUTPUT VOLTAGE vs SINKING LOAD CURRENT

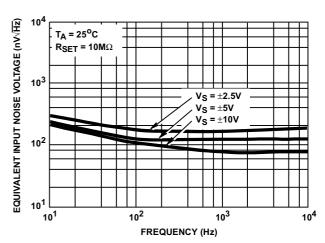

FIGURE 10. INPUT NOISE VOLTAGE vs FREQUENCY

FIGURE 11. BANDWIDTH vs SET CURRENT

FIGURE 12. SLEW RATE vs SET CURRENT