# www.tvsat.com.pl

CD4042BM/CD4042BC Quad Clocked D Latch

March 1988

3.0V to 15V

0.45 V<sub>DD</sub> (typ.)

or 1 driving 74LS

Fan out of 2 driving 74L

National Semiconductor

# CD4042BM/CD4042BC Quad Clocked D Latch

02

V<sub>SS</sub> TI /F/5966-1

## **General Description**

The CD4042BM/CD4042BC quad clocked "D" latch is a monolithic complementary MOS (CMOS) integrated circuit constructed with P- and N-channel enhancement mode transistors. The outputs Q and  $\overline{Q}$  either latch or follow the data input depending on the clock level which is programmed by the polarity input. For polarity = 0; the information present at the data input is transferred to Q and  $\overline{Q}$  during 0 clock level; and for polarity = 1, the transfer occurs during the 1 clock level. When a clock transition occurs (positive for polarity = 0 and negative for polarity = 1), the information present at the input during the clock transition is retained at the outputs until an opposite clock transition occurs.

**Dual-In-Line Package**

# **Connection Diagram**

Vnn

#

### Features

- Wide supply voltage range

- High noise immunity

- Low power TTL compatibility

- Clock polarity control

- Clock polarity control

Fully buffered data inputs

- Fully buffered data in

Q and Q outputs

# Truth Table

| Clock  | Polarity | Q     |

|--------|----------|-------|

| 0      | 0        | D     |

| _      | 0        | Latch |

| 1      | 1        | D     |

| $\sim$ | 1        | Latch |

#### Order Number CD4042B

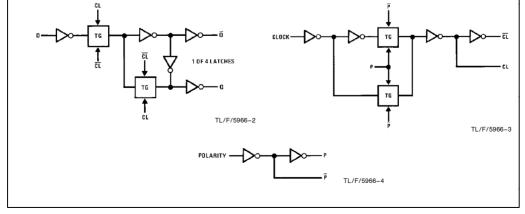

Logic Diagrams

©1995 National Semiconductor Corporation TL/F/5966

RRD-B30M105/Printed in U. S. A.

#### Absolute Maximum Ratings (Notes 1 and 2) If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| ·····,                                      |                                    |

|---------------------------------------------|------------------------------------|

| Supply Voltage (V <sub>DD</sub> )           | -0.5V to $+18V$                    |

| Input Voltage (V <sub>IN</sub> )            | $-0.5V$ to $V_{\mbox{DD}}$ $+0.5V$ |

| Storage Temperature Range (T <sub>S</sub> ) | -65°C to +150°C                    |

| Power Dissipation (P <sub>D</sub> )         |                                    |

| Dual-In-Line                                | 700 mW                             |

| Small Outline                               | 500 mW                             |

| Lead Temperature (T <sub>L</sub> )          |                                    |

| (Soldering, 10 seconds)                     | 260°C                              |

|                                             |                                    |

## Recommended Operating Conditions (Note 2)

| ( ,                                           |                                    |

|-----------------------------------------------|------------------------------------|

| Supply Voltage (V <sub>DD</sub> )             | 3V to 15V                          |

| Input Voltage (V <sub>IN</sub> )              | 0V to V <sub>DD</sub>              |

| Operating Temperature Range (T <sub>A</sub> ) |                                    |

| CD4042BM                                      | -55°C to +125°C                    |

| CD4042BC                                      | $-40^{\circ}$ C to $+85^{\circ}$ C |

|                                               |                                    |

# DC Electrical Characteristics CD4042BM (Note 2)

| Symbol          | Parameter                             | Conditions                                                  | -55°C                 |                      | + 25°C                |                                       |                      | + 125°C               |                      | Units          |

|-----------------|---------------------------------------|-------------------------------------------------------------|-----------------------|----------------------|-----------------------|---------------------------------------|----------------------|-----------------------|----------------------|----------------|

|                 |                                       |                                                             | Min                   | Max                  | Min                   | Тур                                   | Max                  | Min                   | Max                  |                |

| I <sub>DD</sub> | Quiescent Device Current              | $V_{DD} = 5V$ $V_{DD} = 10V$ $V_{DD} = 15V$                 |                       | 1<br>2<br>4          |                       | 0.02<br>0.02<br>0.02                  | 1<br>2<br>4          |                       | 30<br>60<br>120      | μΑ<br>μΑ<br>μΑ |

| V <sub>OL</sub> | Low Level Output Voltage              |                                                             |                       | 0.05<br>0.05<br>0.05 |                       | 0<br>0<br>0                           | 0.05<br>0.05<br>0.05 |                       | 0.05<br>0.05<br>0.05 | V<br>V<br>V    |

| V <sub>OH</sub> | High Level Output Voltage             |                                                             | 4.95<br>9.95<br>14.95 |                      | 4.95<br>9.95<br>14.95 | 5<br>10<br>15                         |                      | 4.95<br>9.95<br>14.95 |                      | V<br>V<br>V    |

| V <sub>IL</sub> | Low Level Input Voltage               |                                                             |                       | 1.5<br>3.0<br>4.0    |                       | 2.25<br>4.5<br>6.75                   | 1.5<br>3.0<br>4.0    |                       | 1.5<br>3.0<br>4.0    | v<br>v<br>v    |

| V <sub>IH</sub> | High Level Input Voltage              |                                                             | 3.5<br>7.0<br>11.0    |                      | 3.5<br>7.0<br>11.0    | 2.75<br>5.5<br>8.25                   |                      | 3.5<br>7.0<br>11.0    |                      | V<br>V<br>V    |

| I <sub>OL</sub> | Low Level Output Current<br>(Note 4)  |                                                             | 0.64<br>1.6<br>4.2    |                      | 0.51<br>1.3<br>3.4    | 0.88<br>2.25<br>8.8                   |                      | 0.36<br>0.9<br>2.4    |                      | mA<br>mA<br>mA |

| I <sub>ОН</sub> | High Level Output Current<br>(Note 4) |                                                             | -0.64<br>-1.6<br>-4.2 |                      | -0.51<br>-1.3<br>-3.4 | -0.88<br>-2.25<br>-8.8                |                      | -0.36<br>-0.9<br>-2.4 |                      | mA<br>mA<br>mA |

| I <sub>IN</sub> | Input Curent                          | $V_{DD} = 15V, V_{IN} = 0V$<br>$V_{DD} = 15V, V_{IN} = 15V$ |                       | -0.1<br>0.1          |                       | -10 <sup>-5</sup><br>10 <sup>-5</sup> | -0.1<br>0.1          |                       | -1.0<br>1.0          | μΑ<br>μΑ       |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The tables of "Recommended Operating Conditions" and "Electrical Characteristics" provide conditions for actual device operation.

Note 2:  $V_{SS}\,=\,0V$  unless otherwise specified.

Note 3: Being a latch, the CD4042BM/CD4042BC is not clock rise and fall time sensitive.

Note 4:  $I_{\mbox{OH}}$  and  $I_{\mbox{OL}}$  are tested one output at a time.

| Symbol          | Parameter                 | Conditions                                        | -40°C |      | + 25°C |       |      | +85°C |      | Units  |

|-----------------|---------------------------|---------------------------------------------------|-------|------|--------|-------|------|-------|------|--------|

| Symbol          |                           |                                                   | Min   | Max  | Min    | Тур   | Max  | Min   | Max  | Joints |

| I <sub>DD</sub> | Quiescent Device Current  | $V_{DD} = 5V$                                     |       | 4    |        | 0.02  | 4    |       | 30   | μΑ     |

|                 |                           | $V_{DD} = 10V$                                    |       | 8    |        | 0.02  | 8    |       | 60   | μA     |

|                 |                           | $V_{DD} = 15V$                                    |       | 16   |        | 0.02  | 16   |       | 120  | μA     |

| VOL             | Low Level Output Voltage  | $ I_0  < 1 \ \mu A, V_{IH} = V_{DD}, V_{IL} = 0V$ |       |      |        |       |      |       |      |        |

| 01              |                           | $V_{DD} = 5V$                                     |       | 0.05 |        | 0     | 0.05 |       | 0.05 | V      |

|                 |                           | $V_{DD} = 10V$                                    |       | 0.05 |        | 0     | 0.05 |       | 0.05 | V      |

|                 |                           | $V_{DD} = 15V$                                    |       | 0.05 |        | 0     | 0.05 |       | 0.05 | V      |

| Voh             | High Level Output Voltage | $ I_0  < 1 \ \mu A, V_{IH} = V_{DD}, V_{IL} = 0V$ |       |      |        |       |      |       |      |        |

| 011             |                           | $V_{DD} = 5V$                                     | 4.95  |      | 4.95   | 5     |      | 4.95  |      | V      |

|                 |                           | $V_{DD} = 10V$                                    | 9.95  |      | 9.95   | 10    |      | 9.95  |      | V      |

|                 |                           | $V_{DD} = 15V$                                    | 14.95 |      | 14.95  | 15    |      | 14.95 |      | V      |

| VIL             | Low Level Input Voltage   | I <sub>O</sub>   < 1 μA                           |       |      |        |       |      |       |      |        |

|                 |                           | $V_{DD} = 5V, V_{O} = 0.5V \text{ or } 4.5V$      |       | 1.5  |        | 2.25  | 1.5  |       | 1.5  | V      |

|                 |                           | $V_{DD} = 10V, V_O = 1V \text{ or } 9V$           |       | 3.0  |        | 4.5   | 3.0  |       | 3.0  | V      |

|                 |                           | $V_{DD} = 15V, V_O = 1.5V \text{ or } 13.5V$      |       | 4.0  |        | 6.75  | 4.0  |       | 4.0  | V      |

| VIH             | High Level Input Voltage  | I <sub>O</sub>   < 1 μA                           |       |      |        |       |      |       |      |        |

|                 |                           | $V_{DD} = 5V, V_O = 0.5V \text{ or } 4.5V$        | 3.5   |      | 3.5    | 2.75  |      | 3.5   |      | V      |

|                 |                           | $V_{DD} = 10V, V_O = 1V \text{ or } 9V$           | 7.0   |      | 7.0    | 5.5   |      | 7.0   |      | V      |

|                 |                           | $V_{DD} = 15V, V_O = 1.5V \text{ or } 13.5V$      | 11.0  |      | 11.0   | 8.25  |      | 11.0  |      | V      |

| I <sub>OL</sub> | Low Level Output Current  | $V_{IH} = V_{DD}, V_{IL} = 0V$                    |       |      |        |       |      |       |      |        |

|                 | (Note 4)                  | $V_{DD} = 5V, V_{O} = 0.4V$                       | 0.52  |      | 0.44   | 0.88  |      | 0.36  |      | mA     |

|                 |                           | $V_{DD} = 10V, V_{O} = 0.5V$                      | 1.3   |      | 1.1    | 2.25  |      | 0.9   |      | mΑ     |

|                 |                           | $V_{DD} = 15V, V_O = 1.5V$                        | 3.6   |      | 3.0    | 8.8   |      | 2.4   |      | mA     |

| Юн              | High Level Output Current | $V_{IH} = V_{DD}, V_{IL} = 0V$                    |       |      |        |       |      |       |      |        |

|                 | (Note 4)                  | $V_{DD} = 5V, V_{O} = 4.6V$                       | -0.52 |      | -0.44  | -0.88 |      | -0.36 |      | mΑ     |

|                 |                           | $V_{DD} = 10V, V_{O} = 9.5V$                      | -1.3  |      | -1.1   | -2.25 |      | -0.9  |      | mΑ     |

|                 |                           | $V_{DD} = 15V, V_O = 13.5V$                       | -3.6  |      | -3.0   | -8.8  |      | -2.4  |      | mA     |

| I <sub>IN</sub> | Input Curent              | $V_{DD} = 15V, V_{IN} = 0V$                       |       | -0.3 |        | -10-5 | -0.3 |       | -1.0 | μA     |

| -               |                           | $V_{DD} = 15V, V_{IN} = 15V$                      |       | 0.3  |        | 10-5  | 0.3  |       | 1.0  | μA     |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The tables of "Recommended Operating Conditions" and "Electrical Characteristics" provide conditions for actual device operation.

Note 2:  $V_{SS}\,=\,0V$  unless otherwise specified.

Note 3: Being a latch, the CD4042BM/CD4042BC is not clock rise and fall time sensitive.

Note 4:  $I_{OH}$  and  $I_{OL}$  are tested one output at a time.

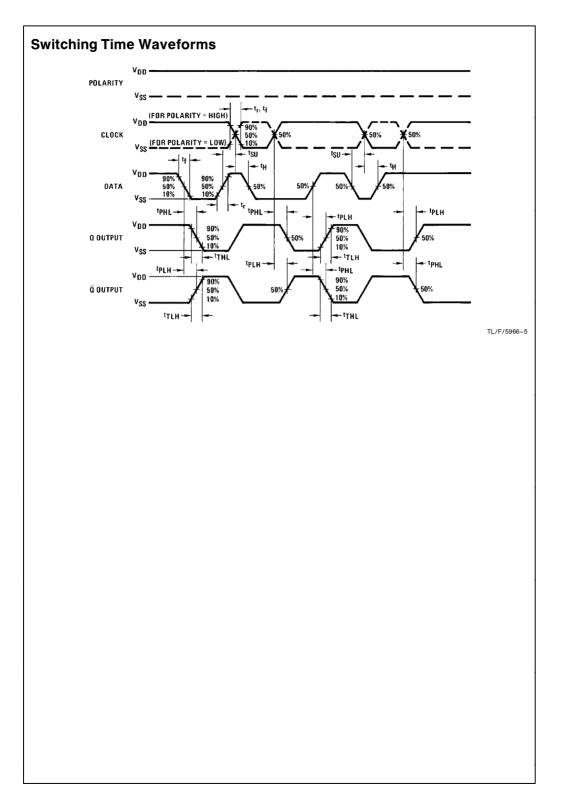

# **AC Electrical Characteristics\***

$T_A$  = 25°C,  $C_L$  = 50 pF,  $R_L$  = 200k, Input  $t_r$  =  $t_f$  = 20 ns, unless otherwise specified

| Symbol                              | Parameter                                        | Conditions                                  | Min | Тур              | Max               | Units          |

|-------------------------------------|--------------------------------------------------|---------------------------------------------|-----|------------------|-------------------|----------------|

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay Time Data In to Q              | $V_{DD} = 5V$ $V_{DD} = 10V$ $V_{DD} = 15V$ |     | 175<br>75<br>60  | 350<br>150<br>120 | ns<br>ns<br>ns |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay Time Data In to $\overline{Q}$ | $V_{DD} = 5V$ $V_{DD} = 10V$ $V_{DD} = 15V$ |     | 150<br>75<br>50  | 300<br>150<br>100 | ns<br>ns<br>ns |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay Time Clock to Q                | $V_{DD} = 5V$ $V_{DD} = 10V$ $V_{DD} = 15V$ |     | 250<br>100<br>80 | 500<br>200<br>160 | ns<br>ns<br>ns |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay Time Clock to $\overline{Q}$   | $V_{DD} = 5V$ $V_{DD} = 10V$ $V_{DD} = 15V$ |     | 250<br>115<br>90 | 500<br>230<br>180 | ns<br>ns<br>ns |

| ţн                                  | Minimum Hold Time                                | $V_{DD} = 5V$ $V_{DD} = 10V$ $V_{DD} = 15V$ |     | 60<br>30<br>25   | 120<br>60<br>50   | ns<br>ns<br>ns |

| t <sub>SU</sub>                     | Minimum Setup Time                               | $V_{DD} = 5V$ $V_{DD} = 10V$ $V_{DD} = 15V$ |     | 0<br>0<br>0      | 50<br>30<br>25    | ns<br>ns<br>ns |

| tw                                  | Minimum Clock Pulse Width                        | $V_{DD} = 5V$ $V_{DD} = 10V$ $V_{DD} = 15V$ |     | 100<br>50<br>30  | 200<br>100<br>60  | ns<br>ns<br>ns |

| t <sub>THL</sub> , t <sub>TLH</sub> | Transition Time                                  | $V_{DD} = 5V$ $V_{DD} = 10V$ $V_{DD} = 15V$ |     | 125<br>60<br>50  | 250<br>125<br>100 | ns<br>ns<br>ns |

| C <sub>IN</sub>                     | Input Capacitance                                | Any Input                                   |     | 5.0              | 7.5               | pF             |

\*AC Parameters are guaranteed by DC correlated testing.

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The tables of "Recommended Operating Conditions" and "Electrical Characteristics" provide conditions for actual device operation.

Note 2:  $V_{SS}\,=\,$  0V unless otherwise specified.

Note 3: Being a latch, the CD4042BM/CD4042BC is not clock rise and fall time sensitive.

Note 4:  $I_{OH}$  and  $I_{OL}$  are tested one output at a time.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.