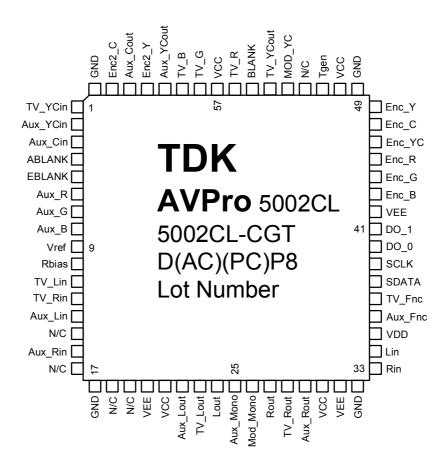

# PRELIMINARY DATASHEET

January 2003

### **DESCRIPTION**

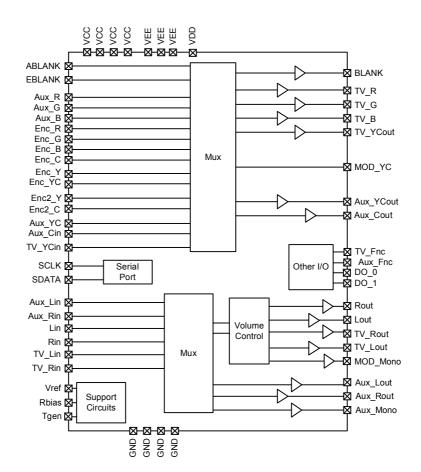

The AVPro® 5002CL device is an audio/video switching IC that supports an input/output port, an input only port, and an output only port. The device includes multiplexers that allow the inputs to be routed to the outputs in various configurations. Additional outputs are provided to drive an external RF modulator. The video outputs of the multiplexers are buffered to drive  $137\Omega$  loads. The audio outputs are buffered to provide 2 Vrms output into a  $600\Omega$  load. The 5002CL has features optimized for Canal+ satellite receiver applications, but it can also be used in other applications that require control of multiple audio and video sources.

### **FEATURES**

- Two SCART connections (Auxiliary, TV)

- Video section

- Integrated output drivers

- RGB, SVHS, composite outputs

- Programmable RGB gain

- Audio section

- Dual mode volume control

0 or 6 dB gain, plus 0 to -31 dB attenuation (1 dB step)

- Programmable gain on DAC input channels

- Ground based outputs (no AC coupling caps)

- Serial port control of switching I<sup>2</sup>C bus

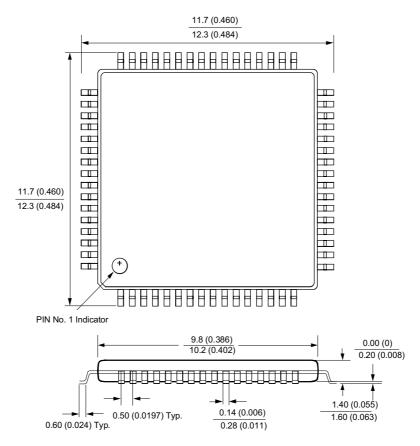

- 64-lead LQFP package

### **BLOCK DIAGRAM**

### **FUNCTIONAL DESCRIPTION**

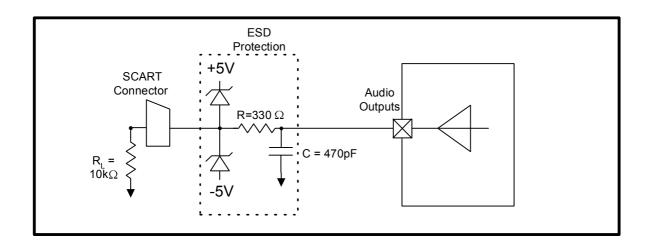

The 5002CL is an audio/video switching device. The device integrates both audio and video drivers so that it can directly drive the SCART interface. The use of a -5 volt supply eliminates the need for AC coupling capacitors on the audio outputs and the SCART audio inputs. Since the –5V supply biases the substrate of the device, the supplies sequencing should be such that the –5V supply turns on first and turns off last. All programmable functions of the device are controlled through a standard I<sup>2</sup>C serial interface and a set of internal registers.

The device will interface to an external video encoder that provides six video outputs. In addition, the 5002CL includes two programmable digital outputs and provides inputs for the TV SCART audio/video.

### **SCART VIDEO SWITCHING**

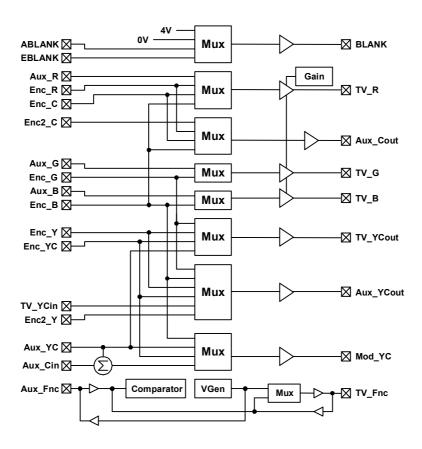

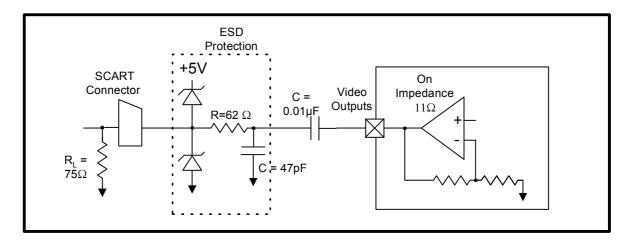

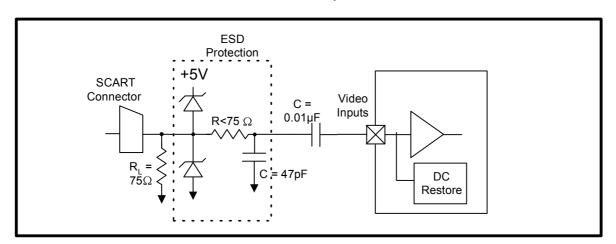

The device is designed to accept video signals from an auxiliary SCART connector, TV SCART connector, and an external video encoder/DAC device. The devices include a set of analog multiplexers that receive video signals from these sources and allow routing of the signals to the various video outputs. The video output drivers have a nominal gain of 1.83 V/V to allow for a series resistance of 62 ohms prior to the 75 ohm termination. A block diagram of the video switching function is provided in Figure 1. Details of the register settings are provided in the section titled "Serial Port Register Tables".

Figure 1: 5002CL Video switching block diagram

### **TV RGB OUTPUTS**

The device accepts RGB video signals from two sources. The Aux\_R, Aux\_G, Aux\_B input pins are typically connected to the auxiliary SCART connector. The Enc\_R, Enc\_G, Enc\_B input pins are connected to the RGB outputs of an external video encoder device. These outputs are used as a video source for the TV SCART pins TV\_R, TV\_G, and TV\_B. The RGB video source is selected by setting the lower three (3) bits of serial port Register 1. When these bits are set to xxxxx000, the RGB source will be the encoder. When these bits are set to xxxxx001, the source will be the auxiliary port. The TV RGB outputs can be muted independently from the TV composite outputs. Setting Bit 6 of Register 1 low (0) will allow normal operation. Setting Bit 6 high (1) will set the TV RGB outputs to the blank level.

**RGB Gain:** The gain of the RGB outputs can be adjusted to one of four different levels. Bits 4 and 5 in Register 2 set the gain of the RGB output amplifiers according to the following table:

| Bit 5 | Bit 4 | RGB Amplifier Gain               |  |

|-------|-------|----------------------------------|--|

| 0     | 0     | Gain = 1.83 V/V = A <sub>0</sub> |  |

| 0     | 1     | Gain = A <sub>0</sub> - 10%      |  |

| 1     | 0     | Gain = A <sub>0</sub> - 20%      |  |

| 1     | 1     | Gain = A <sub>0</sub> - 30%      |  |

**DC Restore:** The device will generate a DC restore level on each video output based on timing referenced to a horizontal sync pulse. When the sync pulse is detected, the DC restore circuit will act to position the blank level to 0.6 V at the respective video output load. The device can be programmed to look for the horizontal sync pulse on all of the RGB input pins or on the associated composite video input pin (Aux\_YC for the auxiliary port or Enc YC for the external encoder). Bit 7 of Register 1 determines the horizontal sync source. At power-up, this bit defaults to a low (0) state, which programs the device to look for sync detect on the RGB input signals. In this mode, the device can detect a horizontal sync on any of the three RGB input signals. When Bit 7 is set to a high (1) state, the device will look for a sync detect from the signal on either the Aux\_YC or Enc\_YC pin depending on which source is selected.

**Blanking**: The signal on the *Blank* output pin is determined by the state of two MSBs in Register 2 according to the following table:

| Bit 7 | Bit 6 | Blank source               |

|-------|-------|----------------------------|

| 0     | 0     | BLANK = ABLANK             |

| 0     | 1     | BLANK = EBLANK             |

| 1     | 0     | BLANK = 0V                 |

| 1     | 1     | BLANK = 4V @ IC output pin |

The user must insure that the source of the *Blank* output is the same as the source for the RGB outputs, i.e. *ABLANK* is selected when the auxiliary RGB is active and *EBLANK* is selected when the encoder RGB is active.

## TV COMPOSITE OUTPUT

The device provides inputs for two composite video sources that can be switched to the TV SCART composite video pin,  $TV\_YCout$ . The  $Aux\_YC$  input pin is typically connected to the "Video In" pin on the auxiliary SCART connector. The  $Enc\_YC$  input pin is typically connected to the "YC" or "CVBS" output from the external video encoder device. Selection of the video source for the TV composite output is accomplished when the RGB video source is selected (see the register tables).

### TV SVHS OUTPUT MODE

The device supports SVHS video format. The SVHS mode is selected for the TV SCART using the lower three (3) bits of Register 1(except for SVHS Enc 4 mode). When the SVHS mode is selected, the  $TV\_YCout$  pin will provide the luminance signal output from the selected source. The chroma output will be provided on the  $TV\_R$  pin. The video source for SVHS mode can be either the auxiliary port or the encoder port. When the auxiliary port is selected as the video source, the video on  $Aux\_R$  will be provided at the  $TV\_R$  output pin and the  $Aux\_YC$  video will be provided at the  $TV\_YCout$  pin.

The device will support SVHS mode for four encoder interface formats. The first encoder interface format accepts chroma signals on the Enc\_C pin and luminance signals on the Enc\_Y pin. This is designated "SVHS. Enc 1" mode. The second format will receive chroma information on the Enc B pin and luminance information on Enc\_G. This format is designated "SVHS, Enc 2". The third format will receive chroma information from the Enc\_R pin and luminance information from the Enc G pin. This mode is designated "SVHS. Enc 3" on the serial port register table. For these three modes, audio will come from the Lin/Rin inputs. The fourth format is designated "SVHS Enc 4". It is selected by setting register one to xx110xxx. Chroma information is received on the Enc2 C input pin and the luminance is received on the Enc2\_Y input pin. For this mode only, audio will come from the TV\_Lin/TV\_Rin inputs, and the video will have chroma output on Aux\_Cout, and luminance output on Aux\_YCout.

When the SVHS mode is selected, the DC restore on the  $TV\_R$  pin will average to approximately 1.8 VDC at the output pin. The DC restore circuit will act to position the blank level to 0.6 V at the  $TV\_YCout$  video output

load. The  $TV\_G$  and  $TV\_B$  outputs will be set to 0 VDC when the SVHS mode is active.

### **RF MODULATOR OUTPUT**

The device provides an output,  $Mod\_YC$ , to drive an external RF modulator. The  $Mod\_YC$  output is a unity gain amplifier designed to drive a  $1k\Omega$  load or higher. When the device is operating in the RGB mode, the signal on the  $Mod\_YC$  output will follow the same source as the  $TV\_YCout$  output.

When the device is in the SVHS mode, the *Mod\_YC* output can be driven by several sources depending on the SVHS video source. These various options are detailed in the serial port register table.

One case that requires additional detail is the auxiliary SVHS mode. In the SVHS mode, the *Aux\_YC* video input will only provide luminance information. Composite video for the modulator output must be generated by summing this luma information with the chroma information from the auxiliary port. The input pin labeled *Aux\_Cin* is used for this purpose. The *Aux\_Cin* input pin is AC coupled to the same source that provides the input signal to *Aux\_R*. An internal summing node combines the video signal on *Aux\_Cin* (chroma) with the video signal on *Aux\_YC* (luma) to generate a composite video signal. In the auxiliary SVHS mode, this signal is provided at the *Mod\_YC* pin.

## TV COMPOSITE VIDEO MUTE

The TV composite video outputs can be muted by programming the lower three (3) bits in Register 1. The power-up default condition is xxxxxx111, which sets the TV composite video outputs to 0 VDC and switches the TV audio outputs to Aux\_Lin/Aux\_Rin. Setting these bits to xxxxxx110 will also mute the TV composite video outputs and switch the TV audio outputs to Lin/Rin.

### **AUXILIARY COMPOSITE OUTPUT**

The auxiliary port includes a composite video output pin (AUX\_YCout) that is typically connected to the "Video Out" pin on an auxiliary SCART connector. Bits 3-5 in Register 1 determine the source for the AUX\_YCout pin as well as for the Aux\_Cout pin. When these bits are set to xx000xxx, the video source will be the Enc\_B input. When these bits are set to xx001xxx, the video source will be the Enc\_YC input. When these bits are set to xx010xxx, the video source will be the TV\_YCin input.

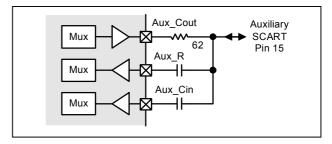

### **AUXILIARY SVHS OUTPUT MODE**

In the SVHS mode, Pin 15 on the auxiliary SCART connector provides chroma information. To support this, the auxiliary port on the 5002CL includes a chroma input pin (*Aux\_Cin*) that is externally AC coupled to Pin 15 on the auxiliary SCART connector.

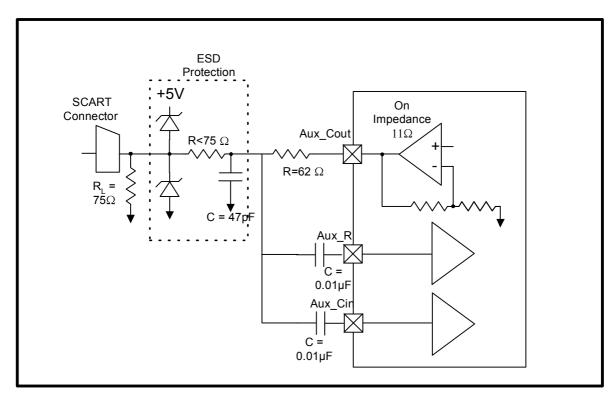

The device also includes an output pin ( $Aux\_Cout$ ) that provides a chroma output to Pin 15 (RED) on the auxiliary SCART connector. When connected with the  $Aux\_R$  and  $Aux\_Cin$  pins, this forms a bi-directional port as shown in the following diagram:

### **Bi-Directional Pin Circuit**

Using this configuration, the device will support SVHS mode for four encoder interface formats. The first encoder interface format will receive chroma information from the *Enc\_C* pin and luminance information from the

Enc\_Y pin. This format is designated "SVHS, Enc 1". The second format will receive chroma information on the Enc\_B input and luminance information on Enc\_G. This format is designated "SVHS, Enc 2". The third format will receive chroma information from the Enc\_R pin and luminance information from the Enc\_G pin. This mode is designated "SVHS, Enc 3" on the serial port register table. For these three modes, audio will come from the Lin/Rin inputs. The fourth format is designated "SVHS Enc 4". Chroma information is received on the Enc2\_C input pin and the luminance is received on the Enc2\_Y input pin. For this mode only, audio will come from the TV Lin/TV Rin inputs.

When the SVHS mode is selected, the DC restore on the *Aux\_Cout* pin will average to approximately 0.9 VDC at the video output load. The DC restore on the *Aux\_YCout* pin will set the blank level to 1.2 V at the IC pin or approximately 0.6 V across the video output load.

### **AUXILIARY VIDEO MUTE**

All auxiliary video outputs can be simultaneously disabled by programming Bits 3-5 in Register 1. The power-up default condition is xx111xxx, which sets all auxiliary video outputs to 0 VDC and switches the auxiliary audio outputs to *Lin/Rin*.

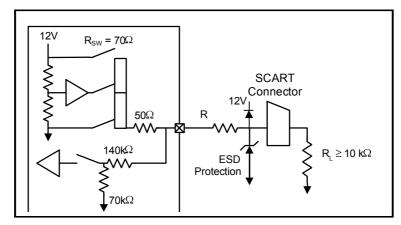

### **FUNCTION SWITCHING**

The device provides functions switching pins for both the Auxiliary ( $Aux\_Fnc$ ) and TV ( $TV\_Fnc$ ) SCART ports. Both of these pins are bi-directional. The direction of the pins is determined by setting bits in Register 2 according to the following table:

| Bits              | Aux_Fnc      | TV_Fnc       |

|-------------------|--------------|--------------|

| xxxx <b>00</b> xx | output       | output       |

| xxxx01xx          | output       | input        |

| xxxx10xx          | input        | output       |

| xxxx11xx          | Passthru I/O | Passthru O/I |

For the case where Register 2 is set to xxxx11xx, the input signal on the *Aux\_Fnc* pin is passed directly through to the *TV\_Fnc* pin as an output, or vice versa. This mode is useful when the rest of the system powers down and all signals from the auxiliary port are passed directly through to the TV port, or vice versa.

When a function pin is set as an input, the voltage on that pin is applied to an internal comparator. The comparator senses

the voltage on the input pin and sets the two (2) LSBs in the read register according to the following table:

| Input voltage | Bits     | Function       |  |

|---------------|----------|----------------|--|

| < 2.0 V       | xxxxxx00 | Normal TV      |  |

| 4.5 to 7.0V   | xxxxxx01 | 16:9 aspect    |  |

| >9.5 V        | xxxxxx10 | Peritelevision |  |

When a function pin is set as an output, the output level for the pin is determined by the state of the two LSBs in Register 2, according to the following table:

| Bits     | Output voltage | Function       |

|----------|----------------|----------------|

| xxxxxx00 | ~0 V           | Normal TV      |

| xxxxxx01 | ~6 V           | 16:9 aspect    |

| xxxxxx10 | ~ 11 V         | Peritelevision |

| xxxxxx11 | ~ 11 V         | Peritelevision |

Note that both the *Aux\_Fnc* pin and the *TV\_Fnc* pin can be set as outputs simultaneously, however they will have the same output voltage.

The function output circuit includes short circuit protection. When a function pin is in the 6V or 11V output mode, if the SCART connection is shorted to ground, then the output is disabled. Likewise, when a function pin is in the 0V output mode, if the SCART connection is connected to a voltage source, then the output is disabled. The load for the function outputs is designed to be  $10 k\Omega$  or higher.

Mux Mux Aux\_Lout Aux\_Mono Mux Aux\_Rout TV\_Rin ⊠-Mux Mux Lout Mux Mux ▼ TV\_Lout Mux Mod\_Mono Mux Aux\_Rin X Mux ▼ TV\_Rout Mux Rout Mux

Figure 2: 5002CL Audio Switching Block Diagram

A: DAC Input Gain (0, 6, 9, or 11.6dB)

B: Volume Control Gain (0 or 6dB)

C: Volume Control Attenuation (0 to -31 dB in -1dB steps)

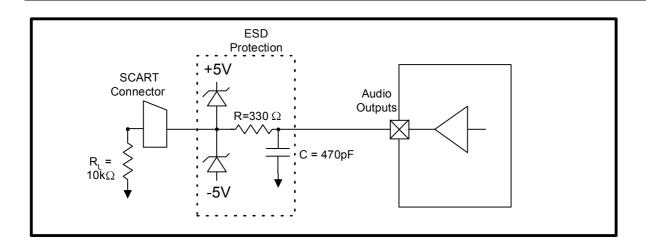

#### **SCART AUDIO SWITCHING**

The audio inputs are considered to be associated with the respective video inputs. As a result, the video selection determines which audio signals will be switched to a given SCART output. Refer to the serial port register table for more information. Also see the audio switching block diagram shown in Figure 2.

The 5002CL provides inputs for the auxiliary audio source (*Aux\_Lin/Aux\_Rin*), a stereo DAC associated with the video encoder inputs (*Lin/Rin*), and inputs from the TV SCART (*TV\_Lin/TV\_Rin*).

### **TV AUDIO OPERATION**

The audio source for the TV port is selected in concert with the video source using the three (3) LSBs of Register 1. The selected audio signals are input to internal multiplexers that allow the user to select between mono and stereo output options. Bits 4 and 5 of Register 3 control the stereo/mono selection according to the following table:

| Bit 1 | Bit 0 | TV left source TV right source |              |  |  |  |

|-------|-------|--------------------------------|--------------|--|--|--|

| 0     | 0     | left input                     | right input  |  |  |  |

| 0     | 1     | left + right                   | left + right |  |  |  |

| 1     | 0     | left input                     | left input   |  |  |  |

| 1     | 1     | right input                    | right input  |  |  |  |

At power-up, these bits default to 00 putting the device in the stereo mode.

**Volume Control:** The left and right TV audio channels can be selected to pass through volume control circuits. Each volume control circuit is formed by a serially connected amplifier and attenuator pair. The amplifier is programmed by register 4, bit 2( "0" for 0 dB and "1" for 6 dB gains ). The attenuator is programmed by the lower 6 bits of register 0( "xx000000" for 0 dB and "xx111111" for -63 dB attenuation, in -1 dB steps ). Only the lower 5 bits are guaranteed for accuracy (0 to -31 dB ).

**DAC Input Gain** (*Lin/Rin*): To support audio DACs that have a limited output range, the 5002CL provides programmable gain amplifiers on the *Lin* and *Rin* inputs. The gain is set by Bits 2 and 3 of Register 3, according to the following table:

| Bit 3 | Bit 2 | Gain           |  |  |

|-------|-------|----------------|--|--|

| 0     | 0     | 0 Gain = 0 dB  |  |  |

| 0     | 1     | Gain = 6 dB    |  |  |

| 1     | 0     | Gain = 9 dB    |  |  |

| 1     | 1     | Gain = 11.6 dB |  |  |

**TV SCART Audio Outputs:** The first pair of signals is labeled *TV\_Lout* and *TV\_Rout* on the block diagram. *TV\_Lout* and *TV\_Rout* are typically used to drive the TV SCART audio pins. These outputs also have an internal multiplexer that allows the user to select TV audio either before or after the internal volume control function. When Bit 0 in Register 4 is set low (0), the volume control is used. When this bit is set high (1), the volume control is bypassed. The power-up default state is volume control active.

TV Audio Line Outputs: The second pair of signals is labeled Lout and Rout on the block diagram. Lout and Rout are standard line outputs. The Lout/Rout outputs have an internal multiplexer that allows the user to select TV audio either before or after the internal volume control function. When Bit 1 in Register 4 is set low (0), the volume control is used. When this bit is set high (1), the volume control is bypassed. The power-up default state is volume control active. In addition, the audio inputs from the TV SCART connector (TV\_Lin/TV\_Rin) can be switched to the line outputs. This is controlled by bit-3 of Register 4. Setting this bit low (0) is the normal operation where the line outputs follow the TV SCART outputs. Setting this bit high (1) will switch the line outputs to the audio source on the TV\_Lin/TV\_Rin inputs.

RF Mono Output: The  $TV\_Lout$  and  $TV\_Rout$  signals are also summed internally to generate a mono audio signal for an external RF modulator. This output is labeled  $Mod\_Mono$ . The internal summing circuit is after the volume control mux so the audio control on this output will be the same as that selected for the  $TV\_Lout$  and  $TV\_Rout$  outputs.

**TV Audio Mute:** A mute function is provided for all *TV* audio outputs. The mute function is controlled by setting Bit 6 in Register 0. When this bit is set to a high state (1), all *TV* audio outputs are muted. This will be the default condition at power-up. When the bit is set to a low state (0), the audio path will be in normal operating mode. This bit can be set independent of the volume control such that the outputs can be muted before any change in volume, or any switching of audio sources.

### **AUXILIARY AUDIO OPERATION**

The auxiliary port includes stereo audio outputs for a SCART connector ( $Aux\_Lout$ ,  $Aux\_Rout$ ) and a mono audio output ( $Aux\_Mono$ ). These outputs can choose between the Lin/Rin input pins or the  $TV\_Lin/TV\_Rin$  input pins. The audio inputs are switched in concert with the associated video inputs according to Bits 3-5 in Register 1.

Internal multiplexers allow the *Aux\_Lout* and *Aux\_Rout* outputs to be configured into either stereo or mono audio outputs. The two MSBs of Register 3 control the stereo/mono selection according to the following table:

| Bit 1 | Bit 0 | Aux_Lout | Aux_Rout |

|-------|-------|----------|----------|

|       |       | source   | source   |

| 0     | 0     | Lin      | Rin      |

| 0     | 1     | Lin+Rin  | Lin+Rin  |

| 1     | 0     | Lin      | Lin      |

| 1     | 1     | Rin      | Rin      |

At power-up, these bits default to 00 putting the device in the stereo mode.

The Aux\_Mono output is generated through an internal summing node that combines the signals of the Aux\_Lout and Aux\_Rout outputs. All three auxiliary audio outputs can be muted by setting the MSB in Register 0. This bit is set high (1) at power-up causing the outputs to be muted. Setting this bit low (0) enables all auxiliary audio outputs.

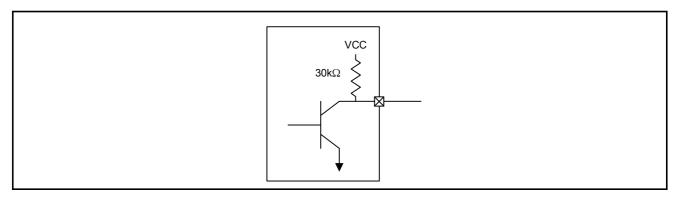

### **DIGITAL OUTPUTS**

The 5002CL provides two programmable digital outputs,  $DO_0$  and  $DO_1$ . These pins are general purpose outputs programmed by setting Bit 0 and 1 in Register 3. Setting the register bits to 0 puts these outputs in the logic low state. Setting the register bits to 1 puts the outputs in the logic high state. Internal pullup resistors (approximately  $30k\Omega$ ) are included on these pins.

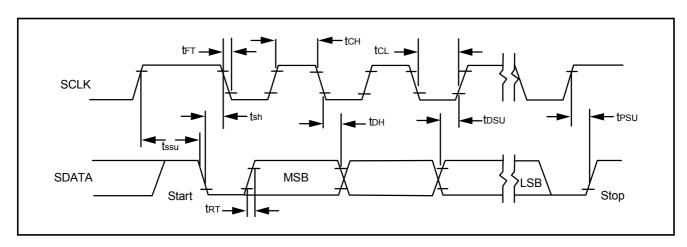

### **SERIAL PORT DEFINITION**

Internal functions of the device are monitored and controlled by a standard inter-IC ( $I^2C$ )bus with data being transferred MSB first on the rising edge of the clock. The serial port operates in a slave mode only and can be written to or read from. The device uses 7-bit addressing, and does not support 10-bit addressing mode. The write register data is sent sequentially, such that if register 4 is to be programmed, then

registers 0, 1, 2, 3 and 4 need to be sent. If only register 2 needs to be programmed, then only registers 0, 1 and 2 data need to be sent. It will support standard and fast bus speed. The default address of the device is 1001000x (1001000 for Write and 10010001 for Read).

The 5002CL includes a read register in which the upper four bits identify the specific chip within the AVPro® family. This allows a single application platform and software to work with a wide variety of AVPro® chips. The ID code for the 5002CL is 0001.

### **DATA TRANSFERS**

A data transfer starts when the SDATA pin is driven from HIGH to LOW by the bus master while the SCLK pin is HIGH. On the following eight clock cycles, the device receives the data on the SDATA pin and decodes that data to determine if a valid address has been received. The first seven bits of information are the address with the eighth bit indicating whether the cycle is a read (bit is HIGH) or a write (bit is LOW). If the address is valid for this device, on the falling SCLK edge of the eighth bit of data, the device will drive the SDATA pin low and hold it LOW until the next rising edge of the SCLK pin to acknowledge the address transfer. The device will continue to transmit or receive data until the bus master has issued a stop by driving the SDATA pin from LOW to HIGH while the SCLK pin is held HIGH

**Write Operation:** When the read/write bit (LSB) is LOW and a valid address is decoded, the device will receive data from the *SDATA* pin. The device will continue to latch data into the registers until a stop condition is detected. The device generates an acknowledge after each byte of data written.

**Read Operation:** When the read/write bit (LSB) is HIGH and a valid address is decoded, the device will transmit the data from the internal register on the following eight *SCLK* cycles. Following the transfer of the register data and the acknowledge from the master, the device will release the data bus.

**Reset:** At power-up the serial port defaults to the states indicated in boldface type. The device also responds to the system level reset that is transmitted through the serial port. When the master sends the address 00000000 followed by the data 00000110, the device resets to the default condition. The device also generates an acknowledge.

## **Serial Port Register Tables**

## Read register Device Address = 10010001

| FUNCTION               | BITS     | DESCRIPTION                                        |

|------------------------|----------|----------------------------------------------------|

| Function Control Input | xxxxxx00 | TV_Fnc or Aux_Fnc pin level =Level 0 < 2V          |

| · ·                    | xxxxxx01 | TV_Fnc or Aux_Fnc pin level =Level 1A ~6.0V        |

|                        | xxxxxx10 | TV_Fnc or Aux_Fnc pin level = Level 1B >9.5V       |

| Not Used               | xxx00xx  | See the note below*                                |

|                        | xxxx11xx |                                                    |

| Device ID code         | 0001xxxx | This code identifies the device type as the 5002CL |

<sup>\*</sup> For customers who require a video sync detection function, please contact the factory regarding this feature.

Write Registers: Device Address = 10010000 (Bold indicates default setting)

Register 0: Audio Control Register A

| FUNCTION                 | BITS                                        | DESCRIPTION                                                              |

|--------------------------|---------------------------------------------|--------------------------------------------------------------------------|

| Volume Control           | xx000000                                    | Audio volume = maximum (0 dB)                                            |

| Attenuation for TV, Line | Audio volume = minimum (-31 dB attenuation) |                                                                          |

| or Mod_Mono audio        | xx100000                                    | Extended TV audio volume control range. Range is approximately -32 dB to |

|                          | xx111111                                    | -63 dB. Extended range is not guaranteed linear.                         |

| TV audio mute            | x0xxxxxx                                    | TV audio (TV_Lout/TV_Rout, Lout/Rout, Mod_Mono) output = normal audio    |

|                          |                                             | output                                                                   |

|                          | x1xxxxxx                                    | TV audio ( <i>TV_Lout/TV_Rout, Lout/Rout, Mod_Mono</i> ) output = Muted  |

| AUX audio mute           | 0xxxxxxx                                    | AUX audio (Aux_Lout/Aux_Rout) output = normal audio output               |

|                          | 1xxxxxxx                                    | AUX audio (Aux_Lout/Aux_Rout) output = Muted                             |

Register 1: Audio/Video Control Register; audio/video source select bits

| TV A/V source     | Bits              | TV_R                                  | TV_G                                                                         | TV_B  | TV_YCout  | Mod_Y0    |                    | TV_Lout,<br>TV_Rout |  |

|-------------------|-------------------|---------------------------------------|------------------------------------------------------------------------------|-------|-----------|-----------|--------------------|---------------------|--|

| RGB/YC, Encoder   | xxxxx000          | Enc_R                                 | Enc_G                                                                        | Enc_B | Enc_YC    | Enc_YC    | ;                  | Lin, Rin            |  |

| RGB/YC, Auxiliary | xxxxx001          | Aux_R                                 | Aux_G                                                                        | Aux_B | Aux_YC    | Aux_YC    |                    | Aux_Lin, Aux_Rin    |  |

| SVHS, Enc 1       | xxxxx010          | Enc_C                                 | 0V                                                                           | 0V    | Enc_Y     | Enc_YC    |                    | Lin, Rin            |  |

| SVHS, Enc 2       | xxxxx011          | Enc_B                                 | 0V                                                                           | 0V    | Enc_G     | Enc_YC    | ;                  | Lin, Rin            |  |

| SVHS, Enc 3       | xxxxx100          | Enc_R                                 | 0V                                                                           | 0V    | Enc_G     | Enc_B     |                    | Lin, Rin            |  |

| SVHS, Aux 1       | xxxxx101          | Aux_R                                 | 0V                                                                           | 0V    | Aux_YC    | AuxYC+Aux | кСin               | Aux_Lin, Aux_Rin    |  |

| TV mute           | xxxxx110          | Enc_R                                 | Enc_G                                                                        | Enc_B | 0V        | 0V        |                    | Lin, Rin            |  |

| TV mute           | xxxxx111          | Aux_R                                 | Aux_G                                                                        | Aux_B | <b>0V</b> | 0V        |                    | Aux_Lin,Aux_Rin     |  |

| Aux A/V source    | Bits              | Aux_Cout                              |                                                                              |       | Aux_YCout |           | Aux_Lout, Aux_Rout |                     |  |

| Composite, Enc 1  | xx000xxx          |                                       | 0V                                                                           |       | Enc_B     |           |                    | Lin, Rin            |  |

| Composite, Enc 2  | xx001xxx          | 0V                                    |                                                                              |       | Enc       | Enc_YC    |                    | Lin, Rin            |  |

| Composite, TV     | xx010xxx          | 0V                                    |                                                                              | TV_   | TV_YCin   |           | TV_Lin, TV_Rin     |                     |  |

| SVHS, Enc 1       | xx011xxx          | Enc_C                                 |                                                                              |       | End       | c_Y       |                    | Lin, Rin            |  |

| SVHS, Enc 2       | xx100xxx          |                                       | Enc_B                                                                        |       | End       | Enc_G     |                    | Lin, Rin            |  |

| SVHS, Enc 3       | xx101xxx          |                                       | Enc_R                                                                        |       | End       | Enc_G     |                    | Lin, Rin            |  |

| SVHS, Enc 4       | xx110xxx          |                                       | Enc2_C                                                                       |       |           | 2_Y       |                    | TV_Lin, TV_Rin      |  |

| Aux mute          | xx111xxx          | 0V                                    |                                                                              |       | 0         | 0V        |                    | Lin, Rin            |  |

| Function          | Bits              | Description                           |                                                                              |       |           |           |                    |                     |  |

| TV RGB Mute       | x <b>0</b> xxxxxx | TV RGB outputs are active             |                                                                              |       |           |           |                    |                     |  |

|                   | x1xxxxxx          | TV RGB outputs are mute (Blank level) |                                                                              |       |           |           |                    |                     |  |

| RGB Sync Source   | 0xxxxxxx          | RGB sync /DC restore source = RGB     |                                                                              |       |           |           |                    |                     |  |

|                   | 1xxxxxxxx         | RGB syn                               | RGB sync /DC restore source = Aux_YC or Enc_YC depending on source selection |       |           |           |                    |                     |  |

Register 2: Video Control Register; video function bits

| Function                | Bits              | Description                                                                  |  |  |  |  |

|-------------------------|-------------------|------------------------------------------------------------------------------|--|--|--|--|

| Function Control Output | xxxxxx00          | Level 0; normal TV output (Function Voltage ~ 0V)                            |  |  |  |  |

| Voltage                 | xxxxxxx01         | Level 1A; 16:9 aspect ratio (Function Voltage ~ 6V)                          |  |  |  |  |

|                         | xxxxxx10          | Level 1B; Peritelevision output mode (Function Voltage ~ 12V)                |  |  |  |  |

|                         | xxxxxxx11         | Level 1B; Peritelevision output mode (Function Voltage ~ 12V)                |  |  |  |  |

| Function Pin Control*   | xxx00xx           | Aux_Fnc pin = output, TV_Fnc pin = output                                    |  |  |  |  |

|                         | xxxx01xx          | Aux_Fnc pin = output, TV_Fnc pin = input                                     |  |  |  |  |

|                         | xxxx10xx          | Aux_Fnc pin = input, TV_Fnc pin = output                                     |  |  |  |  |

|                         | xxxx11xx          | Signals will pass through from Aux_Fnc to TV_Fnc or vice versa.              |  |  |  |  |

|                         |                   |                                                                              |  |  |  |  |

|                         |                   | The voltage applied to this pin (when set as an input) sets the state of the |  |  |  |  |

|                         |                   | two LSBs of the read register. See the note below*                           |  |  |  |  |

| RGB Gain Control        | xx <b>00</b> xxxx | RGB output amplifier gain = normal                                           |  |  |  |  |

|                         | xx01xxxx          | RGB output amplifiers attenuated by 10%                                      |  |  |  |  |

|                         | xx10xxxx          | RGB output amplifiers attenuated by 20%                                      |  |  |  |  |

|                         | xx11xxxx          | RGB output amplifiers attenuated by 30%                                      |  |  |  |  |

| BLANK output selection  | 00xxxxxx          | BLANK = ABLANK                                                               |  |  |  |  |

|                         | 01xxxxxx          | BLANK = EBLANK                                                               |  |  |  |  |

|                         | 10xxxxxx          | BLANK = 0V                                                                   |  |  |  |  |

|                         | 11xxxxxxx         | BLANK = 4V @ IC output pin                                                   |  |  |  |  |

Register 3: Audio and general purpose control register B

| Function                | Bits              | Description                                                  |

|-------------------------|-------------------|--------------------------------------------------------------|

| DO_0 output control     | xxxxxxx0          | DO_0 output = 0 (low)                                        |

|                         | xxxxxxx1          | DO_0 output = 1 (high)                                       |

| DO_1 output control     | xxxxxx <b>0</b> x | DO_1 output = 0 (low)                                        |

|                         | xxxxxx1x          | DO_1 output = 1 (high)                                       |

| Lin/Rin Gain control    | xxxx00xx          | Input amplifier gain set at 0 dB                             |

|                         | xxxx01xx          | Input amplifier gain set at 6 dB                             |

|                         | xxxx10xx          | Input amplifier gain set at 9 dB                             |

|                         | xxxx11xx          | Input amplifier gain set at 11.6 dB                          |

| TV Stereo/mono control  | xx00xxxx          | TV audio mode: stereo                                        |

|                         | xx01xxxx          | TV audio mode: mono (sum L+R) on both TV_Lout and TV_Rout    |

|                         | xx10xxxx          | TV audio mode: L channel on both TV_Lout and TV_Rout         |

|                         | xx11xxxx          | TV audio mode: R channel on both TV_Lout and TV_Rout         |

| Aux Stereo/mono control | 00xxxxxx          | Aux audio mode: stereo                                       |

|                         | 01xxxxxx          | Aux audio mode: mono (sum L+R) on both Aux_Lout and Aux_Rout |

|                         | 10xxxxxx          | Aux audio mode: L channel on both Aux_Lout and Aux_Rout      |

|                         | 11xxxxxx          | Aux audio mode: R channel on both Aux_Lout and Aux_Rout      |

## Register 4: Audio control register C

| Function                   | Bits              | Description                                                |

|----------------------------|-------------------|------------------------------------------------------------|

| TV volume control select 1 | xxxxxxx           | Volume control active on TV_Lout, TV_Rout; Mod_Mono        |

|                            | xxxxxxxx1         | TV_Lout, TV_Rout; Mod_Mono bypass the volume control       |

| TV volume control select 2 | xxxxxx <b>0</b> x | Volume control active on Lout, Rout                        |

|                            | xxxxxx1x          | Lout, Rout bypass the volume control                       |

| Enable 6dB gain            | xxxxxx0xx         | 0 dB of additional gain added to volume control            |

|                            | xxxxx1xx          | 6 dB additional gain added to volume control               |

| Line Out Source            | xxx0xxx           | Audio on Lout/Rout will be the same as the TV_Lout/TV_Rout |

|                            | xxxx1xxx          | Audio on Lout/Rout will be from the TV_Lin/TV_Rin inputs   |

| Not used                   | 0000xxxx          | Reserved, set to 0 for normal operation                    |

<sup>\*</sup> Function pin voltages: (I) in output mode, are defined by the two LSBs of register 2, (II) in input mode, set the state of the two LSBs of the read register.

Digital read is not meaningful in the pass-through mode( xxxx11xx ).

## **SCART Switching Table**

| INPUT PINS                                    | OUTPUT PIN                                                         |

|-----------------------------------------------|--------------------------------------------------------------------|

| Aux_R: Red input from Aux port                | TV_R: Red video output to TV port or SVHS chroma output to TV port |

| Enc_R: Red input from Enc port                |                                                                    |

| Enc_B: Optional chroma input from Enc port    |                                                                    |

| Enc_C: Chroma input from Enc port             |                                                                    |

| Aux_G: Green input from Aux port              | TV_G: Green video output to TV port                                |

| Enc_G: Green input from Enc port              |                                                                    |

| Aux_B: Blue input from AUX SCART              | TV_B: Blue video output to TV port                                 |

| Enc_B: Blue input from Enc port               |                                                                    |

| ABLANK: Blanking input from Aux port          | BLANK: TV blanking output for RGB                                  |

| EBLANK: Blanking input from Enc port          | (also can have internal 0V or 4V produced at this pin)             |

| Aux_YC: Composite input from Aux port         | TV_YCout: Composite video or SVHS Luminance output to TV port      |

| Enc_YC: Composite input from Enc port         |                                                                    |

| Enc_Y: Luminance input from Enc port          |                                                                    |

| Enc_G: Optional luminance input from Enc port |                                                                    |

| Aux_YC: Composite input from Aux port         | Mod_YC: Follows TV_YCout output. Composite (or luma sum with       |

| Enc_YC: Composite input from Enc port         | chroma) output to RF modulator                                     |

| Enc_B: Optional chroma input from Enc port    |                                                                    |

| Aux_Cin/Aux_YC: sum of chroma and luma        |                                                                    |

| Enc_C: Chroma input from Enc port             | Aux_Cout: Chroma output to auxiliary port                          |

| Enc_R: Optional chroma input from Enc port    |                                                                    |

| Enc_B: Optional chroma input from Enc port    |                                                                    |

| Enc2_C: Encoder 2 chroma input                |                                                                    |

| Enc_YC: Composite input from Enc port         | Aux_YCout: Composite video output to auxiliary port                |

| Enc_B: Optional chroma input from Enc port    |                                                                    |

| Enc_G: Optional luminance input from Enc port |                                                                    |

| Enc_Y: Luminance input from Enc port          |                                                                    |

| TV_YCin: Composite input from TV SCART        |                                                                    |

| Enc2_Y: Encoder 2 luminance input             |                                                                    |

| Aux_Lin: Left audio input from Aux port       | Lout: Left audio output to RCA jack                                |

| Lin: Left audio input from audio DAC          |                                                                    |

| TV_Lin: Left audio input from TV SCART        |                                                                    |

| Aux_Lin: Left audio input from Aux port       | TV_Lout: Left audio output to TV port                              |

| Lin: Left audio input from audio DAC          |                                                                    |

| Lin: Left audio input from audio DAC          | Aux_Lout: Left audio output to auxiliary port                      |

| TV_Lin: Left input from TV SCART              |                                                                    |

| Aux_Rin: Right audio input from Aux port      | Rout: Right audio output to RCA jack                               |

| Rin: Right audio input from audio DAC         |                                                                    |

| TV_Rin: Right audio input from TV SCART       |                                                                    |

| Aux_Rin: Right audio input from Aux port      | TV_Rout: Right audio output to TV port                             |

| Rin: Right audio input from audio DAC         |                                                                    |

| Rin: Right audio input from audio DAC         | Aux_Rout: Right audio output to auxiliary port                     |

| TV_Rin: Right input from TV SCART             |                                                                    |

PIN DESCRIPTIONS (Pins marked N/C should be left unconnected during normal use)

| NAME      | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                            |

|-----------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Pi | ns  |      |                                                                                                                                                                                                                                                                                                                        |

| ABLANK    | 4   | I    | Auxiliary Blanking Input: In a typical system, this pin is connected to the RGB status pin (pin 16) from the auxiliary SCART connector.                                                                                                                                                                                |

| Aux_R     | 6   | I    | Auxiliary Red Input: In a typical system, this pin is connected to the RED input pin (pin 15) of the auxiliary SCART connector. This input can be selected as the signal source for the <i>TV_R</i> output pin.                                                                                                        |

| Aux_G     | 7   | I    | Auxiliary Green Input: In a typical system, this pin is connected to the GREEN input pin (pin 11) of the auxiliary SCART connector. This input can be selected as the signal source for the <i>TV_G</i> output pin.                                                                                                    |

| Aux_B     | 8   | I    | Auxiliary Blue Input: In a typical system, this pin is connected to the BLUE input pin (pin 7) of the auxiliary SCART connector. This input can be selected as the signal source for the <i>TV_B</i> output pin.                                                                                                       |

| Aux_Fnc   | 37  | I/O  | Auxiliary Function Pin: This is a bi-directional pin. As an input, it digitizes the analog voltage on the auxiliary SCART function pin (8). As an output, it puts out one of three voltage levels to the auxiliary SCART function pin.                                                                                 |

| Aux_Cin   | 3   | I    | Auxiliary Chroma Input: In a typical application, this pin is AC coupled to the Red input line from the Auxiliary SCART connector. When the SVHS mode is selected from the Auxiliary SCART video source, this pin is internally summed to the Aux_YC input to generate a composite video signal for the Mod_YC output. |

| Aux_YC    | 2   | I    | Auxiliary Video Input: In a typical system, this pin is connected to the composite video input pin (pin 20) of the auxiliary SCART connector. This input can be selected as the signal source for the <i>TV_YCout</i> .                                                                                                |

| Aux_Lin   | 13  | I    | Auxiliary Left Audio Input: In a typical system, this pin is connected to the L Audio input pin (pin 6) of the auxiliary SCART connector. This input can be selected as the signal source for the <i>TV_Lout</i> .                                                                                                     |

| Aux_Rin   | 15  | I    | Auxiliary Right Audio Input: In a typical system, this pin is connected to the R Audio input pin (pin 2) of the auxiliary SCART connector. This input can be selected as the signal source for the <i>TV_Rout</i> .                                                                                                    |

| EBLANK    | 5   | I    | Encoder Blanking Input: In a typical system, this pin is connected to the blanking signal from the external video encoder device.                                                                                                                                                                                      |

| Enc_R     | 45  | I    | Encoder Red Input: In a typical system, this pin is connected to the RED output pin from the external video encoder device. This input can be selected as the signal source for the <i>TV_R</i> output pin.                                                                                                            |

| Enc_G     | 44  | I    | Encoder Green Input: In a typical system, this pin is connected to the GREEN output pin from the external video encoder device. This input can be selected as the signal source for the <i>TV_G</i> output pin.                                                                                                        |

| Enc_B     | 43  | I    | Encoder Blue Input: In a typical system, this pin is connected to the BLUE output pin from the external video encoder device. This input can be selected as the signal source for the <i>TV_B</i> output pin.                                                                                                          |

## PIN DESCRIPTIONS (Continued)

| NAME      | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                              |

|-----------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enc_YC    | 46  | I    | Encoder Video Input: In a typical system, this pin is connected to the composite video output pin from the external video encoder device. This input can be selected as the signal source for the <i>AUX_YCout</i> and/or <i>TV_YCout</i> pins.                          |

| Enc_Y     | 48  | I    | Encoder Luminance Input: In a typical system, this pin is connected to the composite video output pin from the external video encoder device. In SVHS mode, this input can be selected as the signal source for the <i>TV_YCout</i> pin and/or the <i>Aux_YCout</i> pin. |

| Enc2_Y    | 61  | 1    | Encoder 2 Luminance Input: In a typical system, this pin is used as an alternate source for S-video luminance information to a VCR when OSD information is not desired. This input can be selected as the signal source for the <i>Aux_YCout</i> pin.                    |

| Enc_C     | 47  | _    | Encoder Chroma Input: In a typical system, this pin is connected to the <i>TV_R</i> output pin from the external video encoder device. In the SVHS mode, this input can be selected as the signal source for the <i>TV_R</i> pin and/or the <i>Aux_Cout</i> output pin.  |

| Enc2_C    | 63  | _    | Encoder 2 Chroma Input: In a typical system, this pin is used as an alternate source for S-video chroma information to a VCR when OSD information is not desired. This input can be selected as the signal source for the <i>Aux_Cout</i> output pin.                    |

| Lin       | 34  | _    | Left Audio Input: In a typical system, this pin is connected to the left audio output pin of the external audio DAC. This input can be selected as the signal source for the <i>TV_Lout</i> and/or <i>Aux_Lout</i> pins.                                                 |

| Rin       | 33  | Ι    | Right Audio Input: In a typical system, this pin is connected to the right audio output pin of the external audio DAC. This input can be selected as the signal source for the <i>TV_Rout</i> and/or <i>Aux_Rout</i> pins.                                               |

| TV_YCin   | 1   | -    | TV Composite Video input: This pin accepts composite video from the TV SCART. This pin can be selected as the source for the <i>Aux_YCout</i> pin.                                                                                                                       |

| TV_Lin    | 11  | I    | TV Left Audio input: This pin accepts audio from the TV SCART. This pin can be selected as the source for the Aux_Lout audio output and the Lout audio output.                                                                                                           |

| TV_Rin    | 12  | -    | TV Right Audio input: This pin accepts audio from the TV SCART. This pin can be selected as the source for the Aux_Rout audio output and the Rout audio output.                                                                                                          |

| Aux_YCout | 60  | 0    | Auxiliary Video Output: This pin is the composite video output to the auxiliary SCART connector (pin 19). In the SVHS mode, this pin is the luma output.                                                                                                                 |

| Aux_Lout  | 22  | 0    | Auxiliary Left Audio Output: This pin is the output to the left channel audio (pin 3) of the auxiliary SCART connector.                                                                                                                                                  |

| Aux_Rout  | 29  | 0    | Auxiliary Right Audio Output: This pin is the output to the right channel audio (pin1) of the auxiliary SCART connector.                                                                                                                                                 |

| Aux_Mono  | 25  | 0    | Auxiliary Mono Output: This pin is equivalent to the sum of the output signals on Aux_Lout and Aux_Rout.                                                                                                                                                                 |

| BLANK     | 55  | 0    | Blanking output: This output provides the blanking signal to the TV SCART connector (pin 16). This signal is either the blanking signal from the auxiliary SCART connector ( <i>ABLANK</i> ) or the external video encoder ( <i>EBLANK</i> ).                            |

| Lout      | 24  | 0    | Left Audio Output: This pin is the output to the left channel audio RCA jack.                                                                                                                                                                                            |

| Rout      | 27  | 0    | Right Audio Output: This pin is the output to the right channel audio RCA jack.                                                                                                                                                                                          |

| Mod_Mono  | 26  | 0    | Mono Audio Output: This pin is sum of Lout & Rout to the RF modulator input.                                                                                                                                                                                             |

## PIN DESCRIPTIONS (continued)

| NAME         | PIN                     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|--------------|-------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Aux_Cout     | 62                      | 0    | Aux Chroma Output: This output provides a chroma signal to the auxiliary SCART connector to support SVHS operation. This pin is typically AC coupled to pin 15 of the auxiliary SCART connector. When the S-video mode is selected, a chroma signal from the video encoder is output to this pin. |  |  |  |  |  |

| Mod_YC       | 53                      | 0    | TV Modulator Video Output: This pin provides composite video for an external RF modulator. The signal on this pin follows the composite video output to the <i>TV_YCout</i> pin.                                                                                                                  |  |  |  |  |  |

| TV_YCout     | 54                      | 0    | TV Video Output: This pin is the composite video output to the TV SCART connector (pin 19). In the SVHS mode, this pin provides luminance information.                                                                                                                                            |  |  |  |  |  |

| TV_R         | 56                      | 0    | TV Red Output: This pin provides Red video to the TV SCART connector (pin 15). In SVHS mode, this pin provides the chroma information.                                                                                                                                                            |  |  |  |  |  |

| TV_G         | 58                      | 0    | TV Green Output: This pin provides Green video to the TV SCART connector (pin 11).                                                                                                                                                                                                                |  |  |  |  |  |

| TV_B         | 59                      | 0    | TV Blue Output: This pin provides Blue video to the TV SCART connector (pin 7).                                                                                                                                                                                                                   |  |  |  |  |  |

| TV_Lout      | 23                      | 0    | TV Left Audio Output: This pin is the output to the left channel audio (pin 3) of the TV SCART connector.                                                                                                                                                                                         |  |  |  |  |  |

| TV_Rout      | 28                      | 0    | TV Right Audio Output: This pin is the output to the right channel audio (pin1) of the TV SCART connector.                                                                                                                                                                                        |  |  |  |  |  |

| TV_Fnc       | 36                      | I/O  | TV Function Pin: This is a bi-directional pin. As an input, it digitizes the analog voltage on the TV SCART function pin (8). As an output, it puts out one of three voltage levels to the TV SCART function pin.                                                                                 |  |  |  |  |  |

| Digital Pins |                         |      |                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| DO_0         | 40                      | 0    | Digital Output 0: This pin is a general purpose output that is controlled by serial port register.                                                                                                                                                                                                |  |  |  |  |  |

| DO_1         | 41                      | 0    | Digital Output 1: This pin is a general purpose output that is controlled by serial port register.                                                                                                                                                                                                |  |  |  |  |  |

| SCLK         | 39                      | I    | Serial Clock Input: This pin accepts a serial port clock input signal.                                                                                                                                                                                                                            |  |  |  |  |  |

| SDATA        | 38                      | I/O  | Serial Data Input/Output that can receive or transmit serial data.                                                                                                                                                                                                                                |  |  |  |  |  |

| Power/Grou   | ınd Pin                 | ıs   |                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| VCC          | 21,<br>30,<br>50,<br>57 | 1    | +5 VDC power supply pins.                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| VEE          | 20,<br>31,<br>42        | -    | -5 VDC power supply pins.                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| VDD          | 35                      | -    | +12 VDC power supply pin for function switching circuits.                                                                                                                                                                                                                                         |  |  |  |  |  |

| Vref         | 9                       | -    | Internal voltage reference, bypass pin. Add capacitor $0.1\mu F(1.0~\mu F$ for better PSRR ) to ground.                                                                                                                                                                                           |  |  |  |  |  |

| GND          | 17,<br>33,<br>49,<br>64 | -    | Ground for all blocks.                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Rbias        | 10                      | -    | Bias point of internal current generator. Add resistor $10.0k\Omega(\pm 1\%)$ to ground.                                                                                                                                                                                                          |  |  |  |  |  |

| Tgen         | 51                      | _    | Reference point for internal timing circuit. Add capacitor 470pF to ground.                                                                                                                                                                                                                       |  |  |  |  |  |

## **ELECTRICAL SPECIFICATIONS**

## **ABSOLUTE MAXIMUM RATINGS**

Operation beyond the maximum ratings may damage the device

| PARAMETER                                   | RATING                                      |  |  |  |  |

|---------------------------------------------|---------------------------------------------|--|--|--|--|

| Storage temperature                         | -55 to 150 °C                               |  |  |  |  |

| Junction operating temperature              | +150 °C                                     |  |  |  |  |

| Positive supply voltages                    | -0.3 V < VCC < 6V; VCC - 0.3 V < VDD < 13 V |  |  |  |  |

| Negative supply voltages                    | -6 V < VEE < +0.3 V                         |  |  |  |  |

| Voltage applied to Digital and Video Inputs | -0.3V to VCC+0.3 V                          |  |  |  |  |

| Audio input pins                            | VEE -0.3V to VCC+0.3 V                      |  |  |  |  |

| function input pins (300 $\Omega$ source)   | -0.3V to +15 V                              |  |  |  |  |

**SPECIFICATIONS**: Unless otherwise specified:  $0^{\circ}$  < Ta < 70  $^{\circ}$ C; power supplies VCC = +5.0 V ±5%, VEE = -5.0 V ±5%, VDD = 12.0 V ±5%.

| PARAMETER                                 | CONDITION                                     | MIN    | NOM | MAX | UNIT       |

|-------------------------------------------|-----------------------------------------------|--------|-----|-----|------------|

| OPERATING CHARACTERIST                    | TICS                                          |        | •   |     |            |

| Power Supply Currents                     | All outputs loaded                            |        |     |     |            |

|                                           | VCC (+5 VDC)                                  |        | 125 | 150 | mA         |

|                                           | VEE (-5 VDC)                                  |        | -27 | -40 | mA         |

|                                           | VDD (+12 VDC)                                 |        | 2   | 5   | mA         |

| PSRR                                      | f <sub>in</sub> = 100 Hz, 0.3 Vpp on VCC/ VEE | 40     |     |     | dB         |

| Switch time                               | From serial data acknowledge                  |        | 2.0 |     | μ <b>s</b> |

| Serial Port Timing( Set by I <sup>2</sup> | C controller )                                |        |     |     |            |

| SCLK Input Frequency                      |                                               |        |     | 400 | kHz        |

| SCLK LOW time (tcL)                       |                                               | 1.3    |     |     | μs         |

| SCLK HIGH time (tch)                      |                                               | 0.6    |     |     | μs         |

| Rise time (trt)                           | SCLK and SDATA                                |        |     | 300 | ns         |

| Fall time (tft)                           | SCLK and SDATA                                |        |     | 300 | ns         |

| Data set-up time* (tosu)                  | SDATA change to SCLK HIGH                     | 100    |     |     | ns         |

| Data hold time* (tьн)                     | SCLK LOW to SDATA change                      | 0      |     |     | ns         |

| Start set-up time (tssu)                  |                                               | 0.6    |     |     | μS         |

| Start hold time (tsh)                     |                                               | 0.6    |     |     | μS         |

| Stop set-up time (tpsu)                   |                                               | 0.6    |     |     | μs         |

| Glitch rejection                          | maximum pulse on SCLK and/or SDATA            |        |     | 50  | ns         |

| * These specifications also ap            | pply to an acknowledge generated by the d     | evice. | •   | •   |            |

## **SPECIFICATIONS** (continued)

| Digital I/O Characteristics (SCLK, SDATA)                    |                                                                                                                                                                                                   |                    |                     |                   |             |  |  |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|-------------------|-------------|--|--|

| PARAMETER                                                    | CONDITION                                                                                                                                                                                         | MIN                | NOM                 | MAX               | UNIT        |  |  |

| High level input voltage                                     |                                                                                                                                                                                                   | 0.7* VCC           |                     | VCC+0.3           | V           |  |  |

| Low level input voltage                                      |                                                                                                                                                                                                   | GND-0.3            |                     | 0.3* VCC          | V           |  |  |

| High level input current                                     | Vin = Vcc - 1.0V                                                                                                                                                                                  | -10                |                     | 10                | μA          |  |  |

| Low level input current                                      | Vin = 1.0V                                                                                                                                                                                        | -10                |                     | 10                | μA          |  |  |

| Low level output voltage (SDATA)                             | I <sub>OL</sub> = 3 mA                                                                                                                                                                            |                    |                     | 0.4               | V           |  |  |

| Fall time (tft) $V_{lhmin}$ to $V_{lLmax}$ (SDATA)           | Acknowledge or read with $C_L = 400pF$                                                                                                                                                            |                    |                     | 250               | ns          |  |  |

| Digital I/O Characteristics (DO_0                            | , DO_1, TV_Fnc, Aux_Fnc)                                                                                                                                                                          |                    |                     |                   |             |  |  |

| Digital output sink current                                  | DO_0, DO_1, Register bits read 0                                                                                                                                                                  |                    | 1.0                 |                   | mA          |  |  |

| Digital output fall time                                     | $R_{pullup} = 10 \text{ k}\Omega, C_L = 15 \text{ pF}$                                                                                                                                            |                    | 100                 |                   | ns          |  |  |

| TV_Fnc or Aux_Fnc output level 10kΩ or higher load to ground | Register 2 = xxxxxx00 Register 2 = xxxxxx01 Register 2 = xxxxxx10 or xxxxxx11                                                                                                                     | 0.0<br>4.9<br>10.0 | .002<br>5.6<br>11.7 | 1.2<br>6.5<br>VDD | V<br>V<br>V |  |  |

|                                                              | Passthrough Mode Register $2 = xxxx11xx$ $0.0 \text{ V} \leq \text{Vin} \leq 2.0 \text{ V}$ $4.9 \text{ V} \leq \text{Vin} \leq 7.0 \text{ V}$ $10.0 \text{ V} \leq \text{Vin} \leq \text{VDD V}$ | 0.0<br>4.5<br>9.5  |                     | 2.0<br>7.0<br>VDD | V<br>V<br>V |  |  |

| TV_Fnc or Aux_Fnc input levels                               | Read Register = xxxxxx00 Read Register = xxxxxx01 Read Register = xxxxxx10                                                                                                                        | 0.0<br>4.5<br>9.5  |                     | 2.0<br>7.0<br>VDD | V<br>V<br>V |  |  |

Video Characteristics - Unless otherwise noted, typical output loading on all video outputs is  $137\Omega$ . All video outputs are capable of withstanding a sustained  $62\Omega$  load to ground without damage.

| PARAMETER                                | CONDITION                                 | MIN                 | NOM                 | MAX                 | UNIT |

|------------------------------------------|-------------------------------------------|---------------------|---------------------|---------------------|------|

| Input impedance                          | All video inputs                          | 100                 |                     |                     | kΩ   |

| Input dynamic range                      | f <sub>in</sub> = 100 kHz, THD < 1.0%     |                     | 1.5                 |                     | Vpp  |

| Gain at all video outputs, Except Mod_YC | 1.0 Vpp input, f <sub>in</sub> = 100 kHz  | 1.73                | 1.83                | 1.93                | V/V  |

| Gain at Mod_YC                           | 1.0 Vpp input, f <sub>in</sub> = 100 kHz  | 0.95                | 1.0                 | 1.05                | V/V  |

| RGB Gain control                         | 1.0 Vpp input, f <sub>in</sub> = 100 kHz; |                     |                     |                     |      |

| $A_0$ = reading xx00xxxx gain            | Register 2 = xx00xxxx                     | 1.73                | 1.83                | 1.93                | V/V  |

|                                          | Register 2 = xx01xxxx                     | A <sub>0</sub> -12% | A <sub>0</sub> -10% | A <sub>0</sub> -8%  | V/V  |

|                                          | Register 2 = xx10xxxx                     | A <sub>0</sub> –22% | A <sub>0</sub> –20% | A <sub>0</sub> –18% | V/V  |

|                                          | Register 2 = xx11xxxx                     | A <sub>0</sub> –33% | A <sub>0</sub> –30% | $A_0 - 27\%$        | V/V  |

| Output gain inequality                   | RGB or SVHS output channel to channel     | -2.5                |                     | 2.5                 | %    |

| Output DC level                          |                                           |                     |                     |                     |      |

| Blank level clamp voltage                | RGB, CVBS or luma outputs                 |                     | 1.2                 |                     | V    |

| Average level                            | chroma output                             |                     | 1.8                 |                     | V    |

| Signal to noise ratio                    | 1 Vpp input                               | 58                  | 65                  |                     | dB   |

| Cross talk                               | f <sub>in</sub> = 4.43 MHz, 1 Vpp         |                     | -55                 |                     | dB   |

| Output to output differential delay      | RGB signals, f <sub>in</sub> = 100 kHz    | -20                 |                     | 20                  | ns   |

| Blanking level                           | Input or output, logical "0"              | 0.0                 |                     | 0.4                 | V    |

|                                          | Input or output, logical "1"              | 1.0                 |                     | 3.0                 | V    |

| Blanking delay                           | BLANK to RGB signals                      | -50                 |                     | 50                  | ns   |

| Differential phase                       | TV_YCout, Aux_YCout and Mod_YC            | -2.5                |                     | 2.5                 | Deg. |